# Single-Inductor, Multiple-Output (SIMO) Regulator

Check for Samples: TPS65135

### **FEATURES**

- **SIMO Regulator Technology**

- 2.5 V to 5.5 V Input Voltage Range

- 750 mW Output Power at  $V_{IN} = 2.9 \text{ V}$

- Positive Output Voltage up to 6 V

- Negative Output Voltage Down to -7 V

- 1% Output Voltage Accuracy

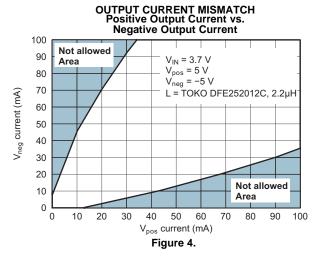

- **Output Current Mismatch of pos and neg rail** up to 50%

- **Excellent Line Regulation**

- **Advanced Power-Save Mode for Light-Load** Efficiency

- **Low-Noise Operation**

- **Out-of-Audio Mode**

- **Short-Circuit Protection**

- **Thermal Shutdown**

- 3-mm × 3-mm Thin QFN Package

### **APPLICATIONS**

- **Active-Matrix OLED Power Supply**

- **LCD Power Supply**

- General dual power supply applications

#### DESCRIPTION

The TPS65135 is a high efficient single inductor dual output converter. Due to its single-inductor multiple-output (SIMO) technology the converter uses a minimum of external components. The device operates with a buckboost topology and generates a positive and a negative output voltage above or below the input voltage rail. The SIMO technology enables excellent line and load regulation which is for instance required to avoid disturbance of a mobile phone display as a result of input voltage variations that occur during transmit periods in mobile communication systems. The device can also be used as a standard ± supply as long as the output current mismatch between the rails is smaller than 50%.

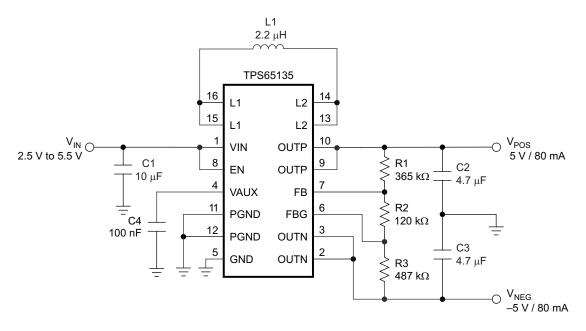

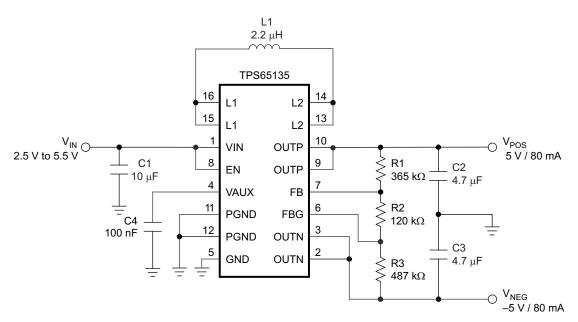

#### TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ORDERING INFORMATION(1)

| T <sub>A</sub> | ORDERING P/N | PACKAGE | PACKAGE MARKING |

|----------------|--------------|---------|-----------------|

| -40°C to 85°C  | TPS65135RTE  | RTE     | CCR             |

(1) The RTE package is available in tape and reel. Add R suffix (TPS65135RTER) to order quantities of 3000 parts per reel. For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

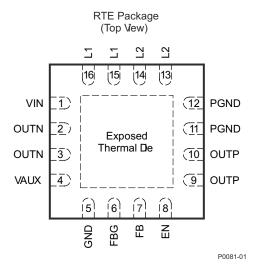

### **16-PIN TQFN PACKAGE**

## **PIN FUNCTIONS**

| PIN         |           | I/O | DESCRIPTION                                                                                                                         |  |  |  |

|-------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | NO.       | 1/0 | DESCRIPTION                                                                                                                         |  |  |  |

| EN          | 8         | 1   | Input pin to enable the device. Pulling this pin high enables the device. This pin has an internal 500 $k\Omega$ pulldown resistor. |  |  |  |

| FB          | 7         | Ι   | Feedback regulation input for the positive output voltage rail                                                                      |  |  |  |

| FBG         | 6         | 1   | Feedback regulation input for GND reference (regulation of the negative output voltage rail)                                        |  |  |  |

| GND         | 5         | -   | Analog ground                                                                                                                       |  |  |  |

| L1          | 15, 16    | I/O | Inductor terminal                                                                                                                   |  |  |  |

| L2          | 13, 14    | I/O | Inductor terminal                                                                                                                   |  |  |  |

| OUTN        | 2, 3      | 0   | Negative output                                                                                                                     |  |  |  |

| OUTP        | 9, 10     | 0   | Positive output                                                                                                                     |  |  |  |

| PGND        | 11, 12    | _   | Power GND                                                                                                                           |  |  |  |

| VAUX        | 4         | I/O | Reference voltage output. This pin requires a 100-nF capacitor for stability.                                                       |  |  |  |

| VIN         | 1         | I   | Input supply                                                                                                                        |  |  |  |

| Exposed the | ermal die | -   | Connect this pad to analog GND.                                                                                                     |  |  |  |

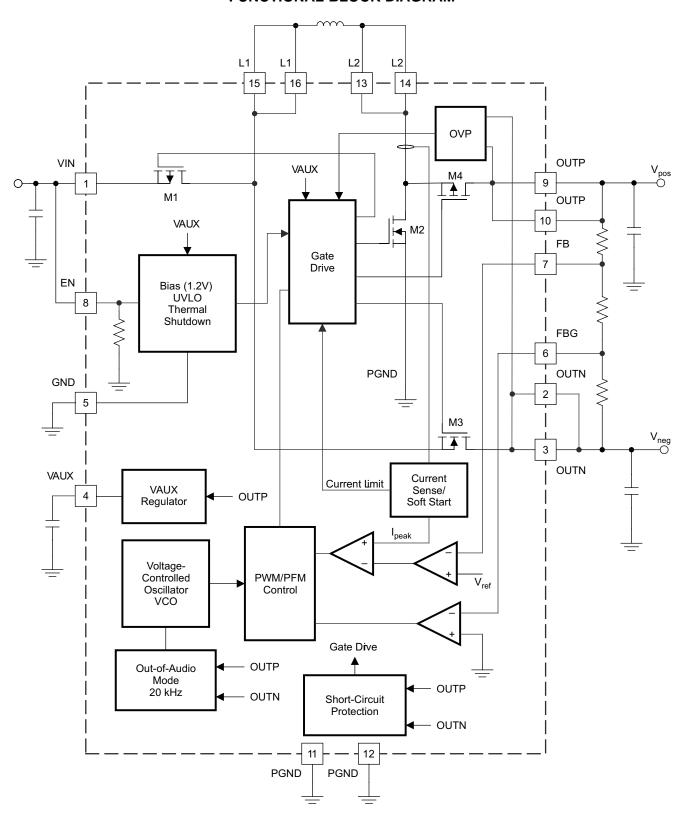

### **FUNCTIONAL BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**(1)(2)

over operating free-air temperature range (unless otherwise noted)

|                                                      |                             | VA             | VALUE           |      |

|------------------------------------------------------|-----------------------------|----------------|-----------------|------|

|                                                      |                             | MIN            | MAX             | UNIT |

|                                                      | VIN, EN, VAUX, FB, OUTP, L2 | -0.3           | 7               | V    |

| Voltage range                                        | L1, OUTN                    | -8             | 7               | V    |

|                                                      | FBG                         | -0.3           | 0.3             | V    |

|                                                      | Human Body Model            |                | 2               | kV   |

| ESD rating                                           | Machine Model               |                | 200             | V    |

|                                                      | Charged Device Model        |                | 1               | kV   |

| Continuous total po                                  | ower dissipation            | See Dissipatio | n Ratings Table |      |

| Operating junction temperature range, T <sub>J</sub> |                             | -40            | 150             | °C   |

| Operating ambient temperature range, T <sub>A</sub>  |                             | -40            | 85              | °C   |

| Storage temperature range, T <sub>stg</sub>          |                             | -65            | 150             | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                  | THERMAL METRIC (1)                           |      | UNIT |

|------------------|----------------------------------------------|------|------|

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 44.8 |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 42.0 |      |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 4.3  | 9004 |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 16.9 | °C/W |

| $\Psi_{JT}$      | Junction-to-top characterization parameter   | 0.4  |      |

| ΨЈВ              | Junction-to-board characterization parameter | 16.8 |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# RECOMMENDED OPERATING CONDITIONS

|                                          |                                  | MIN | TYP | MAX | UNIT |

|------------------------------------------|----------------------------------|-----|-----|-----|------|

| $V_{IN}$                                 | Input voltage range              | 2.5 |     | 5.5 | V    |

| L                                        | Inductor <sup>(1)</sup>          | 1   | 2.2 | 4.7 | μH   |

| C <sub>IN</sub>                          | Input Capacitor <sup>(1)</sup>   | 4.7 | 10  |     | μF   |

| C <sub>OUTP</sub> ,<br>C <sub>OUTN</sub> | Output Capacitors <sup>(1)</sup> | 4.7 | 10  | 20  | μF   |

| T <sub>A</sub>                           | Operating ambient temperature    | -40 |     | 85  | °C   |

| TJ                                       | Operating junction temperature   | -40 |     | 125 | °C   |

(1) Please refer to DETAILED DESCRIPTION for further information

<sup>(2)</sup> All voltage values are with respect to ground.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 3.7 V, EN =  $V_{IN}$ , OUTP = 5 V, OUTN = -5 V,  $T_A$  = -40°C to 85°C; typical values are at  $T_A$  = 25°C (unless otherwise noted).

|                     | PARAMETER                                                                   | TEST CONDITIONS                                              | MIN  | TYP  | MAX  | UNIT       |

|---------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------------|

| SUPPLY (            | CURRENT                                                                     |                                                              |      |      |      |            |

| V <sub>IN</sub>     | Input voltage range                                                         |                                                              | 2.5  |      | 5.5  | V          |

| $I_Q$               | Operating quiescent current into V <sub>IN</sub>                            |                                                              |      | 7    |      | mA         |

| I <sub>SD</sub>     | Shutdown current into V <sub>IN</sub>                                       | EN = low                                                     |      | 0.1  | 2    | μΑ         |

| \/                  | Undervoltage lockout threshold                                              | V <sub>IN</sub> falling                                      | 1.8  | 1.8  | 2.1  | V          |

| $V_{UVLO}$          | Shasivolage lookout ulloshola                                               | V <sub>IN</sub> rising                                       |      | 2    | 2.3  | V          |

|                     | Thermal shutdown                                                            |                                                              |      | 140  |      | °C         |

|                     | Thermal shutdown hysteresis                                                 |                                                              |      | 5    |      | °C         |

| <b>ENABLE</b>       |                                                                             |                                                              |      |      |      |            |

| $V_{H}$             | Logic high-level voltage                                                    | $V_{IN} = 2.5 \text{ V to } 5.5 \text{ V}$                   | 1.2  |      |      | V          |

| $V_L$               | Logic low-level voltage                                                     | V <sub>IN</sub> = 2.5 V to 5.5 V                             |      |      | 0.4  | V          |

| R <sub>EN</sub>     | Enable pulldown resistor                                                    |                                                              | 200  | 500  | 900  | kΩ         |

| OUTPUT              |                                                                             |                                                              |      |      |      |            |

| V <sub>OUTP</sub>   | Positive output voltage range                                               |                                                              | 3    |      | 6    | V          |

| $OVP_P$             | Positive overvoltage protection                                             | I <sub>OUT</sub> = 10 mA                                     | 6.1  | 7    |      | V          |

| V <sub>OUTN</sub>   | Negative output voltage range                                               |                                                              | -2.5 |      | -7   | V          |

| $OVP_N$             | Negative overvoltage protection                                             | I <sub>OUT</sub> = 10 mA                                     | -7.1 | -7.6 |      | V          |

| I <sub>mis</sub>    | Output current mismatch I <sub>pos</sub> to I <sub>neg</sub> <sup>(1)</sup> |                                                              | -50% |      | 50%  |            |

| $V_{OUTP}$          | Positive output voltage regulation                                          |                                                              | -1 % | 1.24 | +1 % | V          |

| $V_{FBG}$           | Feedback ground regulation                                                  |                                                              | -10  | 0    | 10   | mV         |

|                     | M1 MOSFET on-resistance                                                     | I <sub>L1</sub> = 100 mA                                     |      | 250  |      |            |

| _                   | M2 MOSFET on-resistance                                                     | I <sub>L2</sub> = 100 mA                                     |      | 200  |      | <b>~</b> 0 |

| r <sub>DS(on)</sub> | M3 MOSFET on-resistance                                                     | I <sub>L1</sub> = 100 mA                                     |      | 500  |      | mΩ         |

|                     | M4 MOSFET on-resistance                                                     | I <sub>L2</sub> = 100 mA                                     |      | 300  |      |            |

|                     | Switch current limit (M2)                                                   | $V_{IN} = 3.7 V$                                             | 0.9  | 1.2  | 1.6  | Α          |

| I <sub>SW</sub>     | Switch current limit (M2)                                                   | $V_{IN} = 2.5 \text{ V}$                                     | 1    | 1.5  | 1.9  |            |

| P <sub>OUT</sub>    | Output power                                                                | $V_{pos} - V_{neg} \le 10 \text{ V}; V_{IN} = 2.9 \text{ V}$ | 750  |      |      | mW         |

| f <sub>s</sub>      | Switching frequency                                                         | I <sub>OUT</sub> neg = I <sub>OUT</sub> pos = 30 mA          |      | 1    |      | MHz        |

|                     | Line regulation positive output OUTP                                        | $V_{IN}$ = 2.5V to 5.5V, $I_{OUTN}$ = $I_{OUTP}$ = 5 mA      |      | 0    |      | %/V        |

|                     | Line regulation negative output OUTN                                        | $V_{IN}$ = 2.5V to 5.5V, $I_{OUTN}$ = $I_{OUTP}$ = 5 mA      |      | 0    |      | %/V        |

|                     | Load regulation positive output OUTP                                        | I <sub>OUTN</sub> = I <sub>OUTP</sub> = 0 mA to 80 mA        |      | 0    |      | %/A        |

|                     | Load regulation negative output OUTN                                        | I <sub>OUTN</sub> = I <sub>OUTP</sub> = 0 mA to 80 mA        |      | 0    |      | %/A        |

<sup>(1)</sup> See TYPICAL CHARACTERISTICS and DETAILED DESCRIPTION for more detail

# **Application for Typical Characteristics Measurements**

Figure 1. Application Circuit for Typical Characteristics Measurements

Table 1. Component List for Typical Characteristics Circuit

| Reference  | Description Manufacturer and Part Number                                                       |                            |  |

|------------|------------------------------------------------------------------------------------------------|----------------------------|--|

| C1, C2, C3 | 10 μF, 6.3 V, 0603, X5R, ceramic                                                               | Murata, GRM188R60J106ME84D |  |

| C4         | 100 nF, 10 V, 0603, X7R, ceramic                                                               | Murata, GRM188R71H104KA93D |  |

| L1         | 2.2 μH, 2.2 A, 90 mΩ, 2.5 mm * 2.0 mm * 1.2 mm                                                 | Toko, DFE252012C           |  |

| R1         | Depending on the output voltage, 1%, (all measurements with +/-5 V output voltage uses 365 kΩ) |                            |  |

| R2         | Depending on the output voltage, 1%, (all measurements with +/-5 V output voltage uses 120 kΩ) |                            |  |

| R3         | Depending on the output voltage, 1%, (all measurements with +/-5 V output voltage uses 487 kΩ) |                            |  |

| U1         | TPS65135RTE                                                                                    | Texas Instruments          |  |

#### TYPICAL CHARACTERISTICS

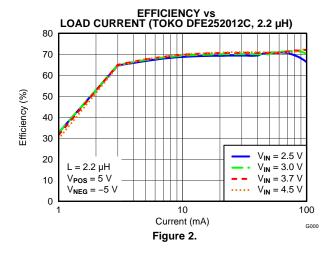

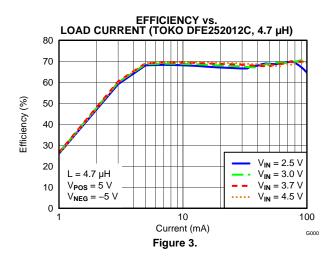

$V_{POS}$ = 5 V,  $V_{NEG}$ = -5 V, unless otherwise noted

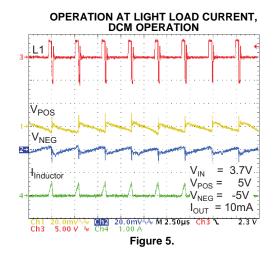

#### **TABLE OF GRAPHS**

| TABLE OF ORAL III                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                       | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| vs. load current with TOKO DFE252012C 2.2 µH inductor                                 | Figure 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| vs. load current with TOKO DFE252012C 4.7 µH inductor                                 | Figure 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| I <sub>OUTP</sub> vs. I <sub>OUTN</sub>                                               | Figure 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| DCM operation                                                                         | Figure 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

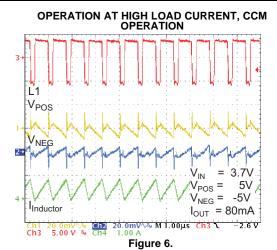

| CCM operation                                                                         | Figure 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

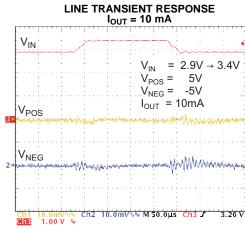

| I <sub>OUT</sub> = 10 mA                                                              | Figure 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

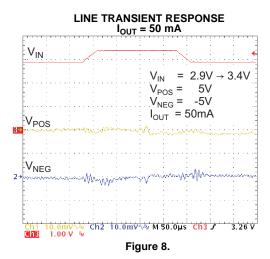

| I <sub>OUT</sub> = 50 mA                                                              | Figure 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

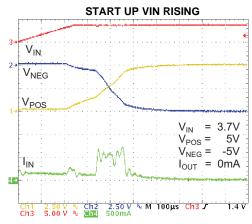

| V <sub>IN</sub> rising, no load                                                       | Figure 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

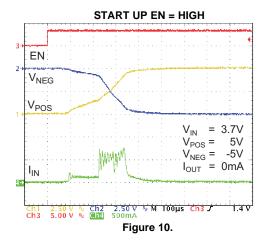

| EN = high, no load                                                                    | Figure 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

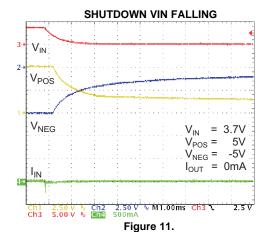

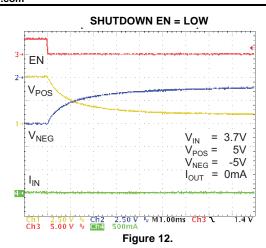

| V <sub>IN</sub> falling, no load                                                      | Figure 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| EN = low, no load                                                                     | Figure 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

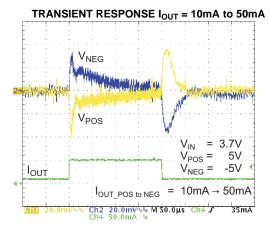

| I <sub>OUT</sub> = 10mA to 50mA (load between V <sub>NEG</sub> and V <sub>POS</sub> ) | Figure 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

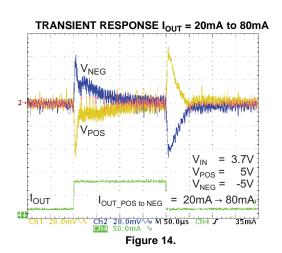

| I <sub>OUT</sub> = 20mA to 80mA (load between V <sub>NEG</sub> and V <sub>POS</sub> ) | Figure 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

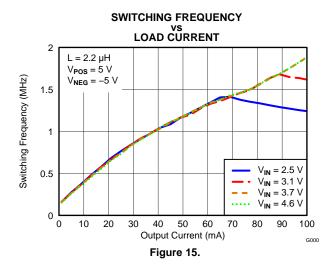

| vs. load current                                                                      | Figure 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

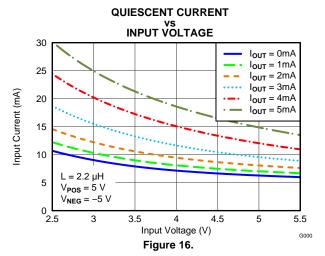

| vs. input voltage                                                                     | Figure 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                                                       | vs. load current with TOKO DFE252012C 4.7 µH inductor  I <sub>OUTP</sub> vs. I <sub>OUTN</sub> DCM operation  CCM operation  I <sub>OUT</sub> = 10 mA  I <sub>OUT</sub> = 50 mA  V <sub>IN</sub> rising, no load  EN = high, no load  V <sub>IN</sub> falling, no load  EN = low, no load  I <sub>OUT</sub> = 10mA to 50mA (load between V <sub>NEG</sub> and V <sub>POS</sub> )  I <sub>OUT</sub> = 20mA to 80mA (load between V <sub>NEG</sub> and V <sub>POS</sub> )  vs. load current |  |  |  |

Figure 9.

8

Figure 13.

#### DETAILED DESCRIPTION

The TPS65135 operates with a four-switch buck-boost converter topology, generating a negative and a positive output voltage with a single inductor. The device uses the SIMO regulator technology featuring best-in-class line-transient regulation, buck-boost mode for the positive and negative outputs, and highest efficiency over the entire load-current range. High efficiency over the entire load-current range is implemented by reducing the converter switching frequency. Out-of-audio mode avoids the switching frequency going below 20 kHz.

As illustrated in the FUNCTIONAL BLOCK DIAGRAM, the converter operates with two control loops. One error amplifier sets the output voltage for the positive output OUTP. The ground error amplifier regulates FBG to typically 0 V. Using the external feedback divider allows setting both output voltages, OUTP and OUTN. In principle the converter topology operates just like any other buck-boost converter topology with the difference that the output voltage across the inductor is the sum of the positive and negative output voltage. With this consideration all calculations of the buck-boost converter apply for this topology as well. During the first switch cycle M1 and M2 are closed, connecting the inductor from VIN to GND. During the second switch cycle the inductor discharges to the positive and negative outputs by closing switches M4 and M3. Because the inductor is discharged to both of the outputs simultaneously, the output voltages can be higher or lower than the input voltage. Because of this the converter operates best when the current out of OUTP is equal to the current flowing into OUTN. This is for example the case when driving an AMOLED panel. Asymmetries in load current can be canceled out by the used topology. However this is only possible for current asymmetries of up to 50%. During light load the converter operates in discontinuous conduction mode. The converter operates in peak-currentmode control with the switching cycle given by an internal voltage-controlled oscillator (VCO). As the load current increases the converter operates in continuous-conduction mode. In this mode, the converter moves to peakcurrent control with the switch cycle given by the fixed off-time. The SIMO regulator topology has excellent line transient regulation when operating in discontinuous conduction mode. As the load current increases, entering continuous conduction mode, the line transient performance is linearly decreased.

## **Advanced Power-Save Mode for Light-Load Efficiency**

In order to maintain high efficiency over the entire load-current range, the converter reduces its switching frequency as the load current decreases. The advanced power-save mode controls the switching frequency using a voltage-controlled oscillator (VCO). The VCO frequency is proportional to the inductor peak current, with a lower frequency limit of 20 kHz in typical applications the frequency does not go below 100 kHz. This avoids disturbance of the audio band and minimizes audible noise coming from the ceramic input and output capacitors. By maintaining a controlled switching frequency, possible EMI is minimized. This is especially important when using the device in mobile phones. See Figure 15 for typical switching frequency versus load current. For zero load an internal shunt regulator ensures stable output voltage regulation.

### **Buck-Boost Mode Operation**

Buck-boost mode operation allows the input voltage to be higher or lower than the output voltage. This mode allows the use of batteries and supply voltages that are above the output voltage of OUTP.

### **Inherent Excellent Line-Transient Regulation**

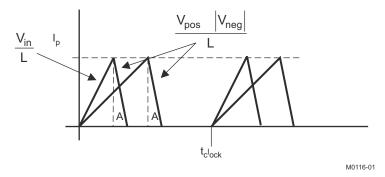

The SIMO regulator achieves inherent superior line-transient regulation when operating in discontinuous conduction mode, shown in Figure 7 and Figure 8. In discontinuous conduction mode the current delivered to the output is given by the inductor peak current and falling slope of the inductor current. This is shown in Figure 17, where the output current, given by the area A, is the same for different input voltages. Because the converter uses peak-current-mode control, the peak current is fixed as long as the load current is fixed. The falling slope of the inductor current is given by the sum of the output voltage and inductor value. This is also a fixed value and independent of the input voltage. Because of this, any change in input voltage changes the converter duty cycle but does not change the inductor peak current or the falling slope of the inductor current. Therefore the output current, given by the area A (Figure 17), remains constant over any input voltage variation. Because the area A is constant, the converter has an inherently perfect line regulation when operating in discontinuous conduction mode. Entering continuous conduction mode (CCM) linearly decreases the line-transient performance. However the line-transient response in CCM is still as good as for any standard current-mode-controlled switching converter. The following formulas detail the relations of the TPS65135 converter topology operating in CCM.

Figure 17. Inherently Perfect Line-Transient Regulation

The converter always sees the sum of the negative and positive output voltage, which is calculated as:

$$V_{O} = V_{OUTP} + |V_{OUTN}|$$

(1)

The converter duty cycle is calculated using the efficiency estimation from the data sheet curves or from real application measurements. A 70% efficiency value is a good value to go through the calculations.

$$D = \frac{V_O}{\eta \cdot V_{IN} + V_O} \tag{2}$$

The output current for entering continuous conduction mode can be calculated. The switching frequency can be obtained from the data sheet graphs. A frequency of 1.5 MHz is usually sufficient for these types of calculations.

$$I_{c} = \frac{V_{o} \cdot (1-D)^{2}}{f_{s} \cdot 2 \cdot L}$$

(3)

The inductor ripple current when operating in CCM can also be calculated.

$$\Delta I_{L} = \frac{V_{IN} \cdot D}{L \cdot f_{S}} \tag{4}$$

Last but not least, the converter switch peak current is calculated as follows.

$$I_{L_{Deak}} = \frac{I_{OUT}}{1 - D} + \frac{1}{2} \cdot \Delta I_{L}$$

(5)

### **Overvoltage Protection**

The device monitors the positive and negative output voltage. The regulators monitor the outputs and reduce the current limit when the output voltages exceed the overvoltage protection limit. They are clamped using a zener diode, the positive output to typically 7V and the negative to -7.6 V.

#### **Short-Circuit Protection**

Both outputs are protected against short circuits either to GND or against the other output. The device switching frequency and the current limit are reduced in case of a short circuit.

#### **Soft-Start Operation**

The device increases the current limit during soft-start operation to avoid high inrush currents during start-up. The current limit typically ramps up to its full-current limit within 100 µs.

Copyright © 2011, Texas Instruments Incorporated

#### **Output-Current Mismatch**

The device operates best when the current of the positive output is similar to the current of the negative output. However the device is able to regulate an output-current mismatch between the outputs of up to 50% (See Figure 4 for typically allowed currents, only 50% mismatch is specified). If the output-current mismatch becomes much larger one of the outputs goes out of regulation and finally the IC shuts down. In case of zero load of one output the other output can support up to 5mA. The IC automatically recovers when the mismatch is reduced. The below formula is used to calculate the maximum supported current mismatch.

$$1 - \frac{\text{Smaller } I_{\text{OUT}}}{\text{Bigger } I_{\text{OUT}}} \le 50\% \tag{6}$$

## **Input Capacitor Selection**

The device typically requires a 10  $\mu$ F ceramic input capacitor. Larger values can be used to lower the input voltage ripple. Table 2 lists capacitors suitable for use on the TPS65135 input.

**Table 2. Input Capacitor Selection**

| CAPACITOR     | COMPONENT SUPPLIER        | SIZE |

|---------------|---------------------------|------|

| 10 μF / 6.3V  | Murata GRM188R60J106ME84D | 0603 |

| 10 μF / 6.3 V | Taiyo Yuden JMK107BJ106   | 0603 |

## Inductor Selection/Efficiency/Line-Transient Response

The device is internally compensated and operates best with a 2.2 µH inductor. For this type of converter the inductor selection is a key element in the design process because it has a big impact on several application parameters. The inductor selection influences the converter efficiency a lot, also the line and load transient response as well as the maximum output current. Because the inductor ripple current is fairly large in this type of application, the inductor has a major impact on the overall converter efficiency. Having large inductor ripple current causes the inductor core and magnetizing losses to become dominant. Due to this, an inductor with a larger dc winding resistance can achieve higher converter efficiencies when having lower core and magnetizing losses. The used inductance influences the line transient regulation, it influences the current range entering continuous conduction mode (CCM). As discussed, the line transient performance decreases when entering CCM. The larger the inductor value, the lower the load current when entering CCM. The formula to calculate the current entering CCM is shown in Equation 3. The inductors listed in Table 3 achieve a good overall converter efficiency while having a low device profile. The first two TOKO inductors achieve the highest efficiency (almoust identical) followed by the LPS3008. The best compromize between efficiency and inductor size is given by the XFL2006 inductor. The inductor saturation current should be 1A or higher, depending on the maximum output current of the application it can also be lower. See Equation 5, where the converter switch current limit is calculated. The converter switch current is equal to the peak inductor current.

**Table 3. Inductor Selection**

| INDUCTOR VALUE | COMPONENT SUPPLIER    | DIMENSIONS in mm              | I <sub>sat</sub> / R <sub>DC</sub> |

|----------------|-----------------------|-------------------------------|------------------------------------|

| 2.2 µH         | TOKO DFE252010C       | 2.5 x 2 x 1                   | 1.9 A / 130 mΩ                     |

| 2.2 µH         | TOKO DFE252012C       | 2.5 x 2 x 1.2                 | 2.2 A / 90 mΩ                      |

| 2.2 µH         | Coilcraft XFL2006-222 | 2 × 1.9 × 0.6                 | 0.8 A / 278 mΩ                     |

| 2.2 µH         | Coilcraft LPS3008-222 | $3 \times 3 \times 0.8$       | 1.1 A / 175 mΩ                     |

| 2.2 µH         | Samsung CIG2MW2R2NNE  | 2 × 1.6 × 1                   | 1.2 A / 110 mΩ                     |

| 2.2 µH         | TOKO FDSE0312-2R2     | $3.3 \times 3.3 \times 1.2$   | 1.2 A / 160 mΩ                     |

| 2.2 µH         | ABCO LPF3010T-2R2     | 2.8 × 2.8 × 1                 | 1.0 A / 100 mΩ                     |

| 2.2 µH         | Maruwa CXFU0208-2R2   | $2.65 \times 2.65 \times 0.8$ | 0.85 A / 185 mΩ                    |

## **Output Capacitor Selection**

A 4.7-µF output capacitor is generally sufficient for most applications, but larger values can be used as well for improved load- and line-transient response at higher load currents. The capacitors of Table 4 is recommended for use with the TPS65135.

**Table 4. Output Capacitor Selection**

| CAPACITOR     | COMPONENT SUPPLIER        | SIZE |

|---------------|---------------------------|------|

| 10 μF / 6.3V  | Murata GRM188R60J106ME84D | 0603 |

| 4.7 μF / 10V  | Taiyo Yuden LMK107BJ475   | 0603 |

| 10 μF / 6.3 V | Taiyo Yuden JMK107BJ106   | 0603 |

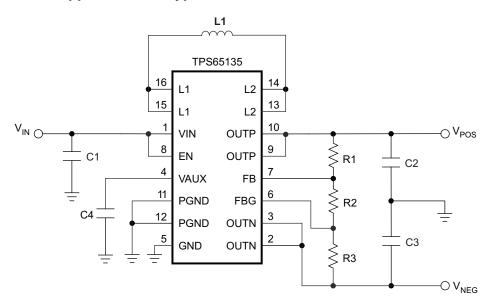

## **Setting the Output Voltages OUTP and OUTN**

The feedback divider R1, R2, R3 sets the positive and negative output voltage. The device regulates the feeback voltage FB to typically 1.24 V and the feedback FBG to typically 0V. R2 is selected to have at least 10  $\mu$ A through the feedback divider.

$$R2 = \frac{1.24V}{10\mu A} \approx 120k\Omega \tag{7}$$

The positive output voltage and R1 are calculated as:

$$V_{POS} = 1.24V \cdot \frac{R1 + R2}{R2} \tag{8}$$

$$R1 = R2 \cdot \left(\frac{V_{POS}}{1.24V} - 1\right) \tag{9}$$

The negative output voltage is calculated as:

$$V_{NEG} = -\left(V_{FB} + V_{FBG}\right) \cdot \frac{R3}{R2} \tag{10}$$

Since V<sub>FBG</sub> is typically regulated to 0 V, the formula can be simplified and R3 is then calculated as:

$$R3 = \frac{|V_{NEG}|}{1.24V} \cdot R2 \tag{11}$$

## **PCB Layout Guidelines**

PCB layout is an important task in the power supply design. Good PCB layout minimizes EMI and allows very good output voltage regulation. For the TPS65135 the following PCB layout guidelines are recommended.

Place the power components first. The inductor and the input and output capacitors must be as close as possible to the IC pins. Place the bypass capacitor for the reference output voltage VAUX as close as possible to pin 4. Use bold and wide traces for power traces connecting the inductor and input and output capacitors. Use a common ground plane or a start ground connection.

See the TPS65135EVM-063 user's guide (SLVU244) and evaluation module for a PCB layout example.

### TYPICAL APPLICATION

Figure 18. Standard Application +/- 5 V Supply

### **REVISION HISTORY**

### Changes from Original (November 2011) to Revision A

Page

Changed the UVLO threshould max value for V<sub>IN</sub> falling From: 2 V To 2.1 V

# PACKAGE MATERIALS INFORMATION

www.ti.com 26-Jan-2013

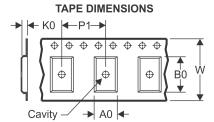

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS65135RTER | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 26-Jan-2013

#### \*All dimensions are nominal

| ĺ | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

|   | TPS65135RTER | WQFN         | RTE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

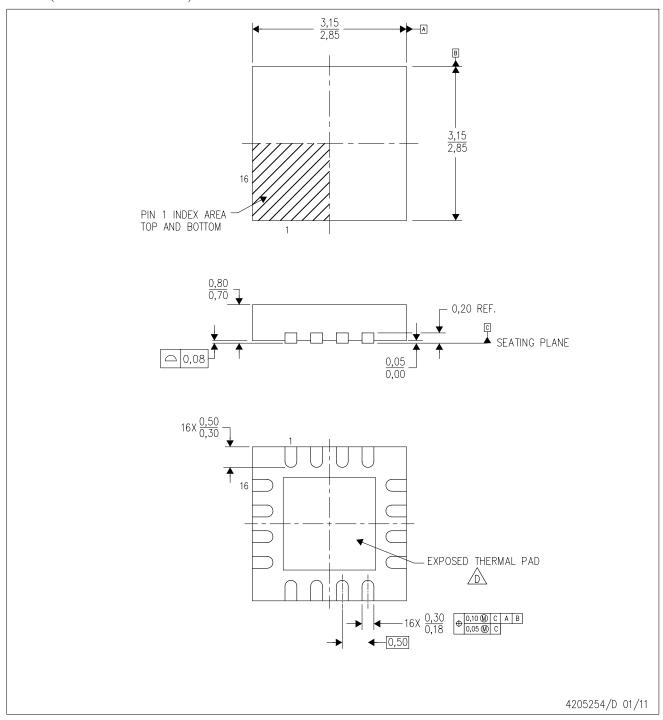

# RTE (S-PWQFN-N16)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. Falls within JEDEC MO-220.

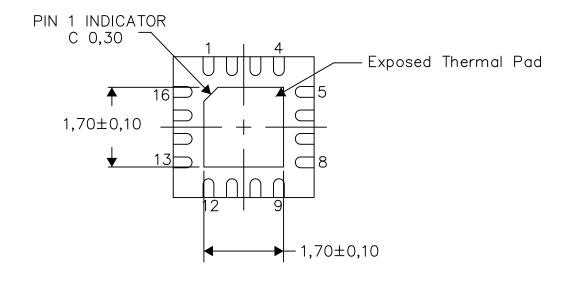

# RTE (S-PWQFN-N16)

# PLASTIC QUAD FLATPACK NO-LEAD

# THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4206446-3/N 07/13

NOTE: A. All linear dimensions are in millimeters

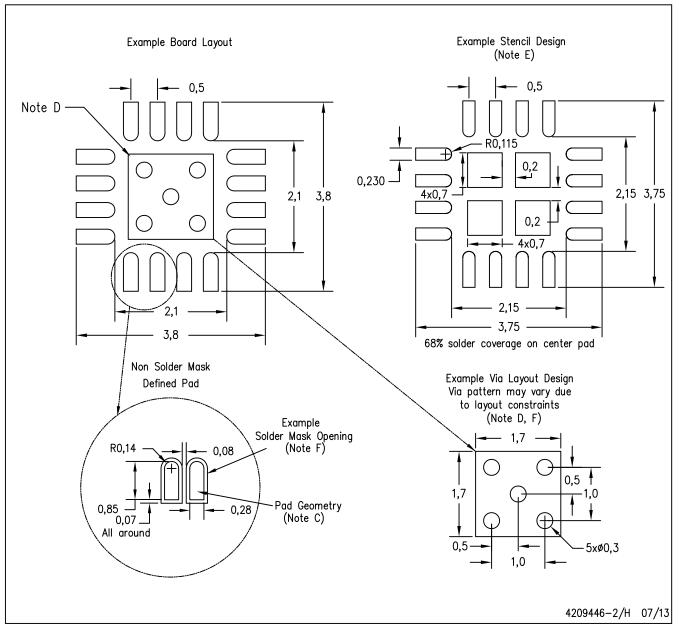

# RTE (S-PWQFN-N16)

# PLASTIC QUAD FLATPACK NO-LEAD

#### NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>