# USB OTG Companion Device with V<sub>BUS</sub> Over Voltage, Over Current Protection, and Four Channel ESD Clamps

Check for Samples: TPD4S214

#### FEATURES

www.ti.com

- Input Voltage Protection at V<sub>BUS</sub> from –7 V to 30 V

- Low R<sub>DS(ON)</sub> N-CH FET Switch for High Efficiency

- Compliant with USB2.0 and USB3.0 OTG spec

- User Adjustable Current Limit From 250 mA to Beyond 1.2 A

- Built-in Soft-start

- Reverse Current Blocking

- Over Voltage Lock Out for V<sub>BUS</sub>

- Under Voltage Lock Out for VOTG IN

- Thermal Shutdown and Short Circuit

Protection

- Auto Retry on any Fault; no Latching off States

- Integrated V<sub>BUS</sub> Detection Circuit

- Low Capacitance TVS ESD Clamp for USB2.0 High Speed Data Rate

- Internal 16ms Startup Delay

- ESD Performance D+, D-, ID, V<sub>BUS</sub> PINS

- ±15-kV Contact Discharge (IEC 61000-4-2)

- ±15-kV Air Gap Discharge (IEC 61000-4-2)

- Space Saving WCSP (12-YFF) Package

#### **APPLICATIONS**

- Cell Phones

- Tablet, eBook

- Set-Top Box

- Portable Media Players

- Digital Camera

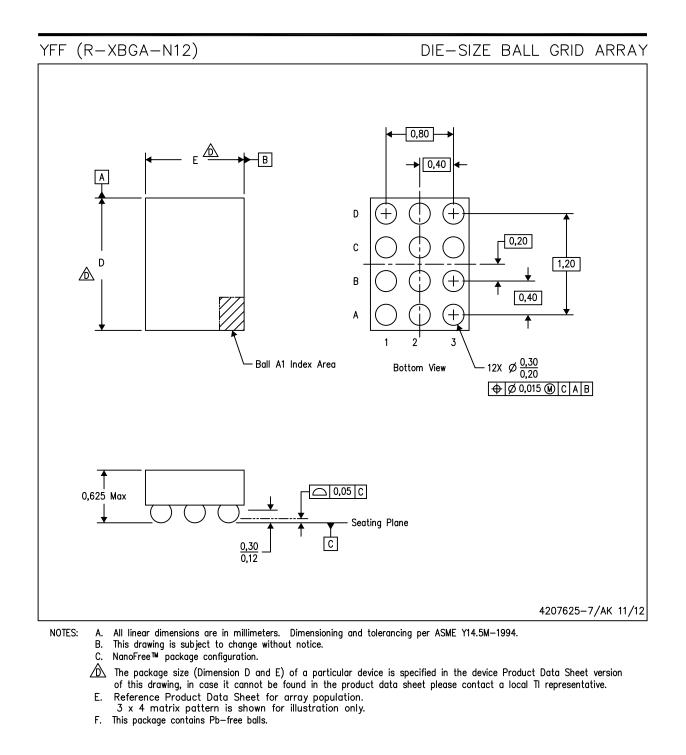

#### YFF PACKAGE (TOP SIDE/SEE-THROUGH VIEW)

|   | 12-YFF Pin Proposal |      |      |  |  |  |  |  |  |  |  |

|---|---------------------|------|------|--|--|--|--|--|--|--|--|

|   | 1                   | 2    | 3    |  |  |  |  |  |  |  |  |

| A | V <sub>OTG_IN</sub> | DET  | VBUS |  |  |  |  |  |  |  |  |

| в | V <sub>OTG_IN</sub> | FLT\ | VBUS |  |  |  |  |  |  |  |  |

| С | EN                  | GND  | ID   |  |  |  |  |  |  |  |  |

| D | ADJ                 | D-   | D+   |  |  |  |  |  |  |  |  |

### DESCRIPTION

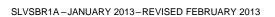

The TPD4S214 is a single-chip protection solution for USB On-the-Go and other current limited USB applications. This device includes an integrated low ( $R_{DS(ON)}$ ) N-channel current limited switch for OTG current supply to peripheral devices. TPD4S214 offers low capacitance TVS ESD clamps for the D+, D-, ID pins for both USB2.0 and USB3.0 applications. The VBUS pin can handle continuous voltage ranging from -7 V to 30 V. The over voltage lock-out (OVLO) at the VBUS pin ensures that if there is a fault condition at the V<sub>BUS</sub> line, the TPD4S214 is able to isolate it and protects the internal circuitry from damage. Similarly, the under voltage lock out (UVLO) at the V<sub>GTG\_IN</sub> pin ensures that there is no power drain from the internal OTG supply to external V<sub>BUS</sub> if V<sub>OTG\_IN</sub> droops below safe operating level.

When EN is high, the OTG switch is activated and the  $\overline{FLT}$  pin indicates whether there is a fault condition. The soft start feature waits 16 ms to turn on the OTG switch after all operating conditions are met. The  $\overline{FLT}$  pin asserts low during any one of the following fault conditions: OVLO (V<sub>BUS</sub> > V<sub>OVLO</sub>), UVLO condition (V<sub>OTG\_IN</sub> < V<sub>UVLO</sub>) over temperature, over current, short circuit condition, or reverse-current-condition (V<sub>BUS</sub> > V<sub>OTG\_IN</sub>). The OTG switch is turned off during any fault condition. Once the switch is turned off, the IC periodically rechecks the faults internally. If the IC returns to normal operating conditions, the switch turns back on and FLT is reset to high.

There is also a  $V_{BUS}$  detection feature for facilitating USB communication between USB host and peripheral device. See Table 2 for detection scheme. If this is not used, DET pin can be either floating or connected to ground.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **TPD4S214**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| T <sub>A</sub> |                           |               | ORDERABLE PART<br>NUMBER | TOP-SIDE MARKING |

|----------------|---------------------------|---------------|--------------------------|------------------|

| -40°C to 85°C  | WCSP – YFF (0.4-mm pitch) | Tape and reel | TPD4S214YFFR             | B3214            |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

#### CIRCUIT SCHEMATIC DIAGRAM

TEXAS INSTRUMENTS

www.ti.com

SLVSBR1A-JANUARY 2013-REVISED FEBRUARY 2013

#### Table 1. Device Operation

| EN | V <sub>OTG IN</sub>                                                                   | V <sub>BUS</sub>                                                                 | OCP | OTP | OTG SW | FLT | FAULT CONDITION                   |

|----|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|--------|-----|-----------------------------------|

| Х  | 0                                                                                     | 0                                                                                | F   | F   | OFF    | L   | SW Disabled                       |

| Х  | Х                                                                                     | х                                                                                | Х   | Т   | OFF    | L   | Over Temperature                  |

| н  | Х                                                                                     | X                                                                                | Т   | Х   | OFF    | L   | Over Current                      |

| Н  | V <sub>OTG_IN</sub> > V <sub>UVLO</sub>                                               | V <sub>BUS</sub> > V <sub>OTG_IN</sub>                                           | F   | F   | OFF    | L   | Reverse-current                   |

| Н  | Х                                                                                     | V <sub>BUS</sub> > V <sub>OVLO</sub>                                             | F   | F   | OFF    | L   | V <sub>BUS</sub> over-voltage     |

| Н  | V <sub>OTG_IN</sub> < V <sub>UVLO</sub>                                               | X                                                                                | F   | F   | OFF    | L   | V <sub>OTG_IN</sub> under-voltage |

| Н  | V <sub>OTG_IN</sub> > V <sub>BUS</sub> and<br>V <sub>OTG_IN</sub> > V <sub>UVLO</sub> | $V_{SHORT}$ < $V_{BUS}$ < $V_{OTG\_IN}$ and $V_{SHORT}$ < $V_{BUS}$ < $V_{OVLO}$ | F   | F   | ON     | Н   | Normal (SW Enabled)               |

# Table 2. $V_{BUS}$ Detection Scheme<sup>(1)</sup>

| EN | VOTG_IN (V <sub>BUS</sub> Detect Power) | V <sub>BUS</sub>                                               | DET | Condition                                                  |

|----|-----------------------------------------|----------------------------------------------------------------|-----|------------------------------------------------------------|

| Х  | Х                                       | $V_{BUS_VALID} < V_{BUS} < V_{BUS_VALID}$ +                    | н   | $V_{\text{BUS}}$ within $V_{\text{BUS}\_\text{VALID}}$     |

| Х  | Х                                       | $V_{BUS_VALID}$ + > $V_{BUS}$ or $V_{BUS}$ > $V_{BUS_VALID}$ + | L   | $V_{\text{BUS}}$ outside of $V_{\text{BUS}\_\text{VALID}}$ |

(1) X = Don't Care, H = Signal High, and L = Signal Low

#### **PIN FUNCTIONS**

|                     | F      | PIN            |        | DECODIDITION                                                                                     |

|---------------------|--------|----------------|--------|--------------------------------------------------------------------------------------------------|

| NAME                | YFF    | DRC            | TYPE   | DESCRIPTION                                                                                      |

| D-                  | D2     | TBD            | I/O    | USB data-                                                                                        |

| D+                  | D3     | TBD            | I/O    | USB data+                                                                                        |

| ID                  | C3     | TBD            | I/O    | USB ID signal                                                                                    |

| FLT                 | B2     | TBD            | 0      | Open-Drain Output. Connect a pullup resistor from FLT\ to the supply voltage of the host system. |

| ADJ                 | D1     | TBD            | I      | Attach external resistor to adjust the current limit                                             |

| EN                  | C1     | TBD            | I      | Enable Input. Drive EN high to enable the OTG switch.                                            |

| V <sub>BUS</sub>    | A3, B3 | TBD            | 0      | USB Power Output                                                                                 |

| V <sub>OTG_IN</sub> | A1, B1 | TBD            | I      | USB OTG Supply Input                                                                             |

| DET                 | A2     | TBD            | 0      | Open-Drain Output. Connect a pullup resistor from DET to the supply voltage of the host system.  |

| GND                 | C2     | Thermal<br>Pad | Ground | Connect to PCB ground plane                                                                      |

STRUMENTS

XAS

#### ABSOLUTE MAXIMUM RATINGS (1)(2)

over operating free-air temperature range (unless otherwise noted)

|                                      |                                                                | MIN  | MAX | UNIT |

|--------------------------------------|----------------------------------------------------------------|------|-----|------|

| V <sub>OTG_IN</sub> , ADJ, EN        | Input voltage                                                  | -0.5 | 7   | V    |

| V <sub>BUS</sub>                     | Output voltage to USB connector                                | -7   | 30  |      |

| FLT, DET                             | Output voltage                                                 | -0.5 | 7   |      |

|                                      | Input clamp current V <sub>1</sub> < 0                         |      | -50 | mA   |

|                                      | I <sub>OUT</sub> Continuous current through FLT and DET output |      | 10  | mA   |

|                                      | I <sub>GND</sub> Continuous current through GND                |      | 100 | mA   |

|                                      | T <sub>J(max)</sub> maximum junction temperature               | -65  | 150 | °C   |

| D+, D-, ID, V <sub>BUS</sub><br>pins | IEC 61000-4-2 Contact Discharge at 25°C                        |      | ±15 | kV   |

| D+, D-, ID, V <sub>BUS</sub><br>pins | IEC 61000-4-2 Air-gap Discharge at 25°C                        |      | ±15 | kV   |

| All pins                             | Human-Body Model at 25°C                                       |      | ±2  | kV   |

| D+, D-, ID pins                      | Peak Pulse Current (tp = 8/20 µs) at 25°C                      |      | 7.8 | А    |

| D+, D-, ID pins                      | Peak Pulse Power (tp = 8/20 µs) at 25°C                        |      | 84  | W    |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

#### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                         |                                                         |                                                               | MIN  | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------|---------------------------------------------------------------|------|-----|-----|------|

| T <sub>A</sub>          | Operating free-air temperature                          |                                                               | -40  |     | 85  | °C   |

| VIH                     | High-level input voltage EN                             |                                                               | 1.2  |     |     | V    |

| VIL                     | Low-level input voltage EN                              |                                                               |      |     | 0.4 | V    |

| t <sub>EN</sub>         | EN ramp rate for proper turn on                         | Valid ramp rate is between 10us and 100ms, rising and falling | 0.01 |     | 100 | ms   |

| t <sub>UVLO_SLEW</sub>  | V <sub>OTG_IN</sub> ramp rate for proper UVLO operation | Valid ramp rate is between 10us and 100ms, rising and falling | 0.01 |     | 100 | ms   |

| t <sub>OVLO_SLEW</sub>  | V <sub>BUS</sub> ramp rate for proper OVLO operation    | Valid ramp rate is between 10us and 100ms, rising and falling | 0.01 |     | 100 | ms   |

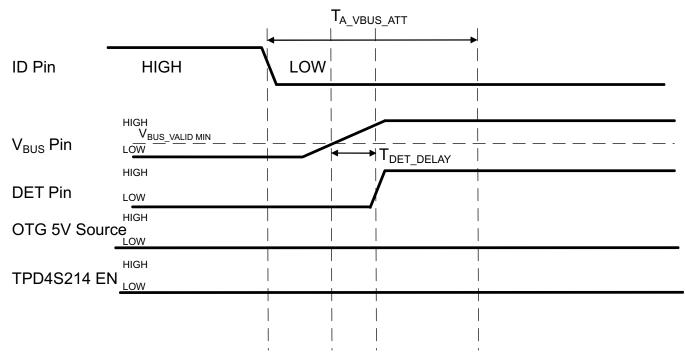

| T <sub>A_VBUS_ATT</sub> | Time to detect V <sub>BUS</sub> device attachme         | nt and turn on DET                                            |      |     | 200 | ms   |

#### THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                 | THERMAL METRICS <sup>(1)</sup> |                           | YFF  | UNITS |

|-----------------|--------------------------------|---------------------------|------|-------|

| θ <sub>JA</sub> | Package thermal impedance      | Package thermal impedance | 89.1 | °C/W  |

(1) The published θ<sub>JA</sub> was modeled assuming a 76mm x 114mm PCB with 4 copper layers and the exposed land pad of the PCB has thermal vias connecting the exposed center pad of the package to an internal GND plane for maximum heat dissipation. For more information about traditional and new thermal metrics, see the IC Package Metrics application report, SPRA953A.

www.ti.com

# ELECTRICAL CHARACTERISTICS FOR EN, FLT, DET, D+, D-, V<sub>BUS</sub>, ID Pins

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                   | TEST CONDITIONS                                                         | MIN | TYP | MAX  | UNIT |

|---------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL_EN</sub>  | EN pin input leakage current                                | EN = 3.3 V                                                              |     |     | 1    | μA   |

| I <sub>OL</sub>     | FLT DET pin output leakage current                          | FLT, DET = 3.6 V                                                        |     |     | 1    | μΑ   |

| V <sub>OL_FLT</sub> | Low-level output voltage FLT\                               | $V_{BUS}$ or $V_{OTG_{IN}} = 5 V$ or $0 V I_{OL} = 100 \mu A$           |     |     | 100  | mV   |

| V <sub>OL_DET</sub> | Low-level output voltage DET                                | $V_{BUS}$ and $V_{OTG_{IN}}$ = 5 V or 0 V I <sub>OL</sub> = 100 µA      |     |     | 100  | mV   |

| C <sub>EN</sub>     | Enable capacitance                                          | $V_{BIAS}$ = 1.8 V, f = 1 MHz, 30 mVpp ripple,<br>$V_{OTG_IN}$ = 5 V    |     | 4.5 |      | pF   |

| V <sub>D</sub>      | Diode forward voltage D+, D–, ID pins;<br>lower clamp diode | l <sub>O</sub> = 8 mA                                                   |     |     | 0.95 | V    |

| I <sub>L_D</sub>    | Leakage current on D+, D–, ID Pins                          | D+, D–, ID = 3.3 V                                                      |     |     | 100  | nA   |

| ΔC <sub>IO</sub>    | Differential capacitance between the D+, D– lines           | $V_{BIAS}$ = 1.8 V, f = 1 MHz, 30 mVpp ripple,<br>$V_{OTG_{-}IN}$ = 5 V |     |     | 0.04 | pF   |

| <u>^</u>            | Capacitance to GND for the D+, D- lines                     | V <sub>BIAS</sub> = 1.8 V, f = 1 MHz, 30 mVpp ripple,                   |     | 1.9 |      | - 5  |

| C <sub>IO</sub>     | Capacitance to GND for the ID lines                         | $V_{OTG_{IN}} = 5 V$                                                    |     | 1.9 |      | pF   |

| N/                  | Breakdown voltage D+, D–, ID pins                           | I <sub>br</sub> = 1 mA                                                  | 6   |     |      | V    |

| V <sub>BR</sub>     | Breakdown voltage on Vbus                                   | I <sub>br</sub> = 1 mA                                                  | 33  |     |      | V    |

| R <sub>DYN</sub>    | Dynamic on resistance D+, D–, ID clamps                     |                                                                         |     | 1   |      | Ω    |

### **ELECTRICAL CHARACTERISTICS FOR UVLO / OVLO**

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                                                        | MIN  | TYP  | MAX  | UNIT |

|------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| INPUT UNDE             | R-VOLTAGE LOCKOUT                                              |                                                                                                                                                                                        |      |      |      |      |

| V <sub>UVLO+</sub>     | Under-voltage lock-out, input power detected threshold rising  | $V_{\text{OTG\_IN}}$ increasing from 0 V to 5 V, No load on $V_{\text{BUS}}$ pin                                                                                                       | 3.4  | 3.6  | 3.8  | V    |

| V <sub>UVLO-</sub>     | Under-voltage lock-out, input power detected threshold falling | $V_{\text{OTG\_IN}}$ decreasing from 5 V to 0 V, No load on $V_{\text{BUS}}$ pin                                                                                                       | 3.0  | 3.2  | 3.5  | V    |

| V <sub>HYS-UVLO</sub>  | Hysteresis on UVLO                                             | $\Delta$ of V_UVLO+ and V_UVLO-                                                                                                                                                        |      | 260  |      | mV   |

| T <sub>RUVLO</sub>     | Recovery time from UVLO                                        | $V_{OTG_{-IN}}$ increasing from 0V to 5V, No load on $V_{BUS}$ pin;<br>time from $V_{OTG_{-IN}} = V_{UVLO+}$ to FLT toggles high                                                       |      | 18   |      | ms   |

| T <sub>RESP_UVLO</sub> | Response time for UVLO                                         | $V_{OTG_IN}$ decreasing from 5V to 0V, No load on $V_{BUS}$ pin;<br>time from $V_{OTG_IN} = V_{UVLO-}$ to FLT\ toggles low                                                             |      | 0.18 |      | μs   |

| OUTPUT OVE             | ERVOLTAGE LOCKOUT                                              |                                                                                                                                                                                        |      |      | •    |      |

| V <sub>OVP+</sub>      | OVLO rising threshold                                          | Both $V_{\text{OTG\_IN}}$ and $V_{\text{BUS}}$ increasing from 5 V to 7 V                                                                                                              | 5.55 | 6.15 | 6.45 | V    |

| V <sub>OVP-</sub>      | OVLO falling threshold                                         | Both $V_{\text{OTG}\_\text{IN}}$ and $V_{\text{BUS}}$ decreasing from 7 V to 5 V                                                                                                       | 5.4  | 6    | 6.3  | V    |

| V <sub>HYS-OVP</sub>   | Hysteresis on OVLO                                             | $\Delta$ of V_{UVLO+} and V_{UVLO-}                                                                                                                                                    |      | 100  |      | mV   |

| T <sub>ROVLO</sub>     | Recovery time from OVLO                                        | Both V <sub>OTG_IN</sub> and V <sub>BUS</sub> decreasing from 7 V to 5 V, V <sub>OTG_IN</sub> = 5 V;<br>time from V <sub>BUS</sub> = V <sub>OVP</sub> to $\overline{FLT}$ toggles high |      | 9    |      | ms   |

| T <sub>RESP_OVLO</sub> | Response time for OVLO                                         | Both $V_{OTG_{-}IN}$ and $V_{BUS}$ increasing from 5 V to 7<br>V, $V_{OTG_{-}IN} = 5$ V;<br>time from $V_{BUS} = V_{OVP+}$ to $\overline{FLT}$ toggles low                             |      | 17   |      | μs   |

TEXAS INSTRUMENTS

www.ti.com

### ELECTRICAL CHARACTERISTICS FOR DET CIRCUITS

over operating free-air temperature range (unless otherwise noted)

|                          | PARAMETER                             | TEST CONDITIONS                                                              | MIN | TYP | MAX | UNIT |

|--------------------------|---------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>BUS_VALID</sub> - | Valid V <sub>BUS</sub> voltage detect | $V_{BUS} = 7 V \text{ to } 0 V$                                              | 2.7 | 2.9 | 3   | V    |

| V <sub>BUS_VALID+</sub>  | Valid V <sub>BUS</sub> voltage detect | $V_{BUS} = 0 V to 7 V$                                                       | 5.3 | 5.4 | 5.6 | V    |

| T <sub>DET_DELAY</sub> - | VBUS detect propagation delay-        | VBUS 0 V to 4 V, 200 ns ramp; VBUS = $V_{BUS_VALID-MIN}$ to DET toggles high |     | 4.9 |     | μs   |

| T <sub>DET_DELAY+</sub>  | VBUS detect propagation delay+        | VBUS 6 V to 4 V, 200 ns ramp; VBUS = $V_{BUS_VALID+MAX}$ to DET toggles low  |     | 1.8 |     | μs   |

#### ELECTRICAL CHARACTERISTICS FOR OTG SWITCH

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER               |                                 | TEST CONDITIONS                                                                                            | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>DS_ON</sub>   | OTG switch resistance   | $V_{BUS} = 5 V, IOUT =$         | $V_{BUS} = 5 \text{ V}, \text{ IOUT} = 100 \text{ mA}, R_{ADJ} = 75 \text{ k}\Omega^{(1)}$                 |     |     | 290 | mΩ   |

| V <sub>DROP</sub>    | OTG switch voltage drop | $V_{BUS} = 5 V, IOUT =$         | $V_{\text{BUS}} = 5 \text{ V}, \text{ IOUT} = 100 \text{ mA}, \text{ R}_{\text{ADJ}} = 75 \text{ k}\Omega$ |     |     |     | mV   |

|                      | Lookage surrent at 201/ |                                 | $V_{BUS}$ = 30 V, EN = 5 V, $V_{OTG_{IN}}$ = 5 V                                                           |     | 6   |     | μA   |

| IOTG_OFF_30V         | Leakage current at 30V  |                                 | $V_{BUS} = 30 \text{ V}, \text{ EN} = 5 \text{ V}, V_{OTG_{IN}} = 0 \text{ V}$                             |     | 11  |     | nA   |

| IOTG_OFF_2V          | Leakage current at-2V   | V                               | $V_{BUS}$ = -2 V, EN = 5 V, $V_{OTG_{IN}}$ = 5 V                                                           |     | 30  |     | μA   |

| 1                    | Standby Laskage surrent |                                 | $V_{BUS} = 0 V, EN = 0 V, V_{OTG_{IN}} = 5 V$                                                              |     | 32  |     | μA   |

| I <sub>OTG_OFF</sub> | Standby Leakage current | VOIG_IN                         | $V_{BUS} = 5 \text{ V}, \text{ EN} = 0 \text{ V}, V_{OTG_{IN}} = 0 \text{ V}$                              |     | 10  |     | nA   |

|                      |                         |                                 | $V_{BUS} = 5 \text{ V}, \text{ EN} = 5 \text{ V}, V_{OTG_{IN}} = 0 \text{ V}$                              |     | 1   |     | nA   |

| BUS_REV              | Reverse Leakage current |                                 | $V_{BUS}$ = 5.5 V, EN = 5 V, $V_{OTG_{IN}}$ = 5 V                                                          |     | 6   |     | μA   |

| T <sub>ON</sub>      | Turn-ON time            | $R_L = 100 \ \Omega, \ C_L = 1$ | uF, R <sub>ADJ</sub> = 75 kΩ                                                                               |     | 16  |     | ms   |

| T <sub>OFF_EN</sub>  | Turn-OFF time           | $R_L = 100 \ \Omega, \ C_L = 1$ | uF, $R_{ADJ}$ = 75 kΩ, toggle EN                                                                           |     | 80  |     | μs   |

| T <sub>OFF_OTG</sub> | Turn-OFF time           | $R_L = 100 \ \Omega, \ C_L = 1$ | uF, $R_{ADJ}$ = 75 kΩ, toggle V <sub>OTG_IN</sub>                                                          |     | 0.5 |     | μs   |

| T <sub>RISE</sub>    | Output rise time        | $R_L = 100 \ \Omega, \ C_L = 1$ | uF, R <sub>ADJ</sub> = 75 kΩ                                                                               |     | 137 |     | μs   |

| T <sub>FALL</sub>    | Output fall time        | $R_L = 100 \ \Omega, \ C_L = 1$ | uF, R <sub>ADJ</sub> = 75 kΩ                                                                               |     | 1.6 |     | μs   |

(1)  $R_{DS_ON}$  is measured at 25°C

### **ELECTRICAL CHARACTERISTICS FOR CURRENT LIMIT and SHORT CIRCUIT PROTECTION**

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                             | TEST CO                                                                          | MIN                                                                                                        | TYP  | MAX  | UNIT |    |

|---------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|----|

|                     |                                                       |                                                                                  | $R_{ADJ} = 226 \ k\Omega^{(1)}$                                                                            | 235  | 255  | 281  |    |

|                     | Current-limit threshold                               |                                                                                  | $R_{ADJ} = 75 k\Omega^{(1)}$                                                                               | 735  | 792  | 830  | 1  |

| I <sub>OCP</sub>    | (maximum DC output current<br>IOUT delivered to load) | $V_{OTG_{IN}} = 5 V$                                                             | $R_{ADJ} = 62 k\Omega^{(1)}$                                                                               | 885  | 959  | 1005 | mA |

|                     |                                                       |                                                                                  | $R_{ADJ} = 45 \text{ k}\Omega^{(1)}$                                                                       | 1128 | 1200 | 1363 |    |

| T <sub>BLANK</sub>  | Blanking time after enable                            | V <sub>OTG_IN</sub> = 5 V                                                        | RL = 1 Ω, CL = 1 uF,<br>RADJ = 75 kΩ                                                                       | 4    |      |      | ms |

| T <sub>DEGL</sub>   | Deglitch time while enabled                           |                                                                                  |                                                                                                            |      | 9.4  |      | ms |

| T <sub>DET_SC</sub> | Response time to short circuit                        | - V <sub>OTG IN</sub> = 5 V, RL = 100 Ω,                                         |                                                                                                            |      | 10   |      | μs |

| T <sub>REG</sub>    | Short circuit regulation time                         | $CL = 1 \text{ uF}, \text{ RADJ} = 75 \text{ k}\Omega,$<br>apply short to ground | Hiccup pulse width; auto-<br>retry time                                                                    |      | 13   |      | ms |

| T <sub>OCP</sub>    | Short circuit over current<br>protection time         |                                                                                  | Hiccup pulse period                                                                                        | 153  |      | ms   |    |

| V <sub>SHORT</sub>  | Short circuit threshold                               |                                                                                  |                                                                                                            |      | 4    |      | V  |

| I <sub>INRUSH</sub> | Inrush current during a startup                       | See Figure 5 under test configuration                                            | $\label{eq:RL} \begin{array}{l} RL = 100 \; \Omega,  CL = 22 \; \muF, \\ RADJ = 75 \; k\Omega \end{array}$ |      | 726  |      | mA |

(1) External resistor tolerance is ±1%

#### SLVSBR1A-JANUARY 2013-REVISED FEBRUARY 2013

#### ELECTRICAL CHARACTERISTICS FOR REVERSE VOLTAGE PROTECTION

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                                           | TEST CONDITIONS                        | MIN | TYP  | MAX | UNIT |  |  |  |

|-------------------|-------------------------------------------------------------------------------------|----------------------------------------|-----|------|-----|------|--|--|--|

| V <sub>REV</sub>  | Reverse-voltage comparator trip point (at V <sub>BUS</sub> port)                    | V <sub>BUS</sub> > V <sub>OTG_IN</sub> |     | 50   |     | mV   |  |  |  |

| T <sub>RRVP</sub> | Time from reverse-voltage condition to MOSFET switch off and $\overline{FLG}$ = low |                                        |     | 17.5 |     | ms   |  |  |  |

| T <sub>RREV</sub> | Re-arming time                                                                      |                                        |     | 25   |     | μs   |  |  |  |

#### SUPPLY CURRENT CONSUMPTION

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                                    | TEST CONDITION                                                 | TYP           | MAX | UNIT |    |

|-------------------------|--------------------------------------------------------------|----------------------------------------------------------------|---------------|-----|------|----|

| I <sub>VOTG_IN</sub> ON | High-level V <sub>OTG_IN</sub> operating current consumption | $V_{OTG_{IN}} = 5 \text{ V}$ , No load on $V_{BUS}$ , EN = 5 V | RADJ = 75 kΩ  | 162 | 200  | μA |

|                         |                                                              |                                                                | RADJ = 226 kΩ | 150 | 200  | μA |

#### THERMAL SHUTDOWN

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                              | TEST CONDITIONS                                                                                                           | TYP | MAX  | UNIT |

|--------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| T <sub>SHDN+</sub> | Shutdown temp rising                   |                                                                                                                           | 141 |      | °C   |

| T <sub>SHDN-</sub> | Shutdown temp falling                  |                                                                                                                           | 125 |      | °C   |

| T <sub>HYST</sub>  | Thermal-shutdown Hysteresis            |                                                                                                                           | 16  |      | °C   |

| P <sub>MAX</sub>   | Maximum power dissipation              | $V_{OTG_{IN}} = 5 \text{ V}, \text{ R}_{load} = 5 \Omega, \text{ EN} = 5 \text{ V}, \text{ R}_{ADJ} = 75 \text{ K}\Omega$ |     | 0.16 | W    |

| T <sub>JMAX</sub>  | Junction Temp at max power dissipation |                                                                                                                           |     | 150  | °C   |

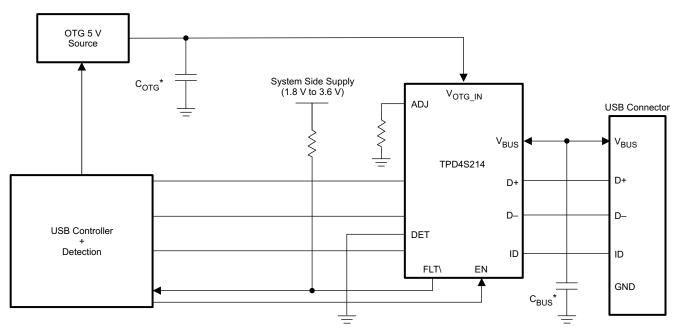

Figure 2. USB2.0 Application Diagram Without Using On-chip  $V_{\text{BUS}}$  Detect

TEXAS INSTRUMENTS

www.ti.com

SLVSBR1A-JANUARY 2013-REVISED FEBRUARY 2013

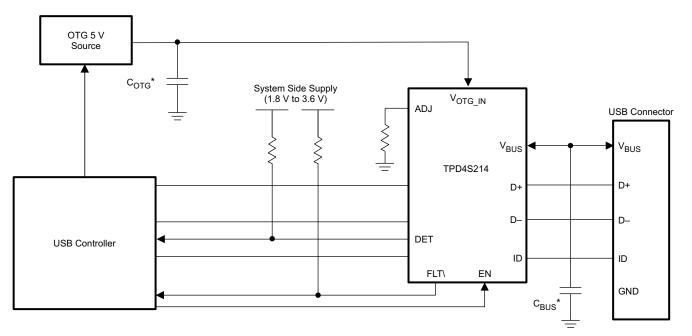

Figure 3. USB 2.0 Application Diagram Using On-chip V<sub>BUS</sub> Detect

$^*C_{\text{BUS}}$  and  $C_{\text{OTG}}$  have minimum recommended values of 1  $\mu\text{F}$  each

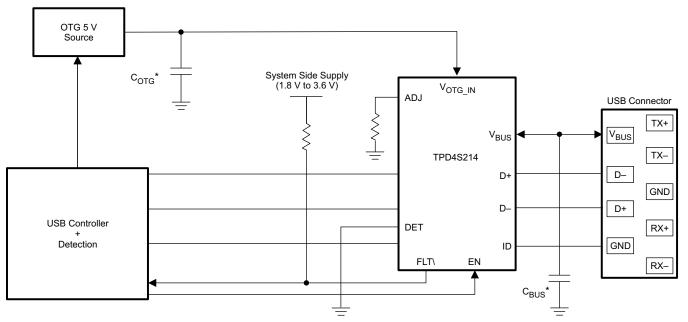

SLVSBR1A-JANUARY 2013-REVISED FEBRUARY 2013

#### **TEST CONFIGURATION**

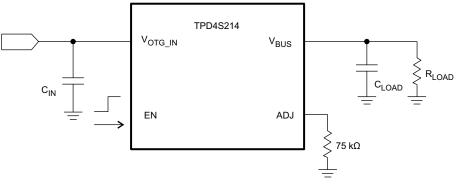

Figure 5. Inrush Current Test Configuration.

Enable is toggled from low to high. See the Application Information section for  $C_{\rm IN}$  and  $C_{\rm LOAD}$  value recommendations.

www.ti.com

INSTRUMENTS

Texas

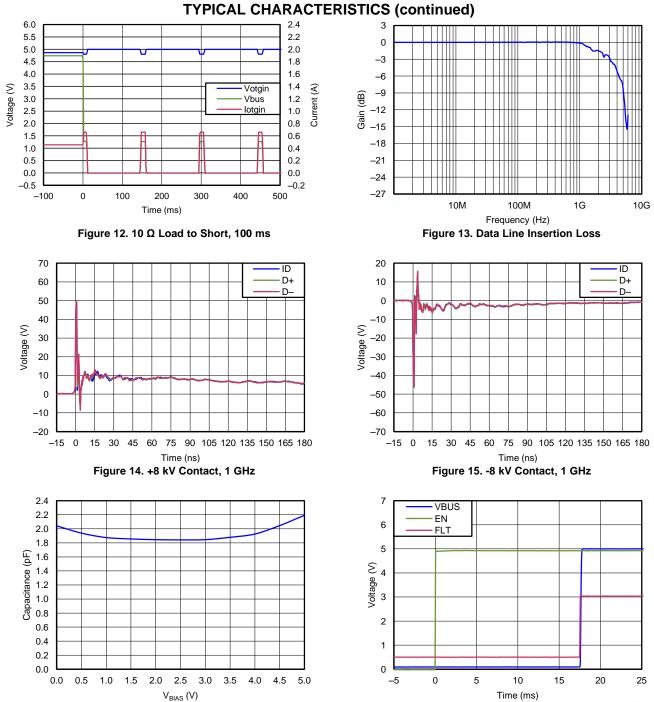

Figure 17. TPD4S214 Turn On Characteristics

Figure 16. C<sub>IO</sub> vs. V<sub>BIAS</sub>, f = 1 MHz

Figure 22. V<sub>BUS</sub> Valid Detect Lower

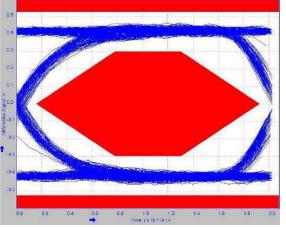

Figure 23. Eye Diagram with no EVM and no IC, Full USB2.0 Speed at 480 Mbps

# **TPD4S214**

www.ti.com

#### SLVSBR1A-JANUARY 2013-REVISED FEBRUARY 2013

#### **TYPICAL CHARACTERISTICS (continued)**

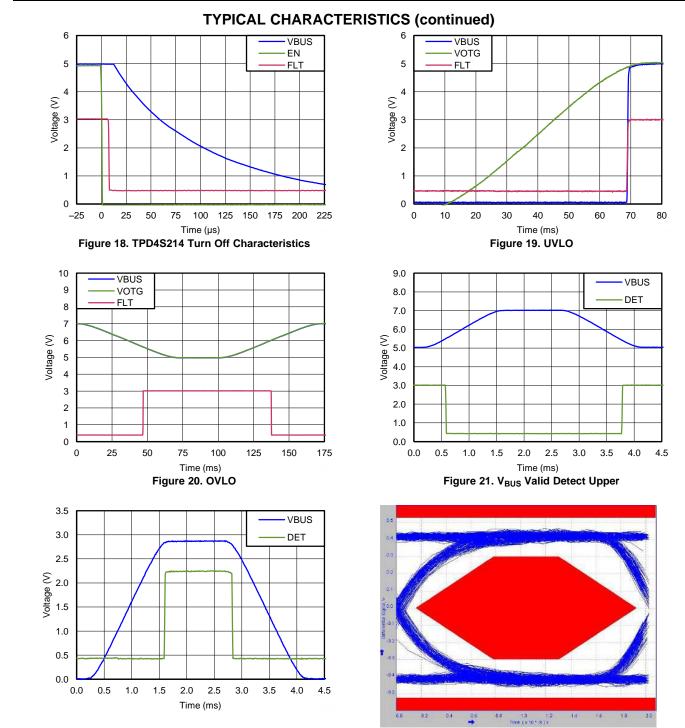

Figure 24. Eye Diagram with TPD4S214EVM but no IC, Full USB2.0 Speed at 480 Mbps

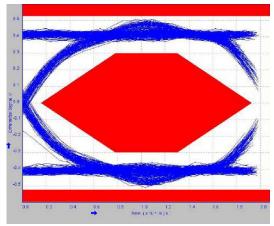

Figure 25. Eye Diagram with TPD4S214EVM and IC, Full USB2.0 Speed at 480 Mbps

#### APPLICATION INFORMATION

A USB OTG device's one and only connector is the AB receptacle, which accepts either an A or B plug. When an A-plug is inserted, the OTG device is called the A-device and when a B-plug is inserted it is called the Bdevice. A-device is often times referred to as "Targeted Host" and B-device as "USB peripheral". TPD4S214 supports an OTG device when TPD4S214's system is acting as an A-device and powering the USB interface. The TPD4S214 may also be used in non-OTG applications where it resides on the current source side.

#### Inrush Current Protection

As soon as TPD4S214 is enabled, its logic block detects the presence of any fault conditions highlighted in Table 1. In the absence of any fault condition, a counter waits for 16 ms, after which a trickle charge of 1 µA slowly turns on the main switch. During the inrush period, the peak inrush current will be limited to no more than the current limit set by the external resistor  $R_{ADJ}$ .

#### **INPUT CAPACITOR (OPTIONAL)**

To limit the voltage drop on the input supply caused by transient in-rush currents when the switch turns on into a discharged load capacitor or short-circuit, a capacitor needs to be placed between VOTG IN and GND. A 10-µF ceramic capacitor, C<sub>IN</sub>, placed close to the pins, is usually sufficient. Higher values of C<sub>IN</sub> can be used to further reduce the voltage drop during high-current application. When switching heavy loads, it is recommended to have an input capacitor about 10 times higher than the output capacitor to avoid excessive voltage drop.

#### **OUTPUT CAPACITOR (OPTIONAL)**

Due to the integrated body diode in the NMOS switch, a C<sub>IN</sub> greater than C<sub>LOAD</sub> is highly recommended. A C<sub>LOAD</sub> greater than CIN can cause VBUS to exceed VOTG IN when the system supply is removed. A CIN to CLOAD ratio of 10 to 1 is recommended for minimizing V<sub>OTG IN</sub> dip caused by inrush currents during startup.

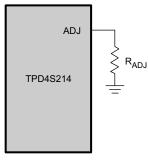

#### **Current Limit**

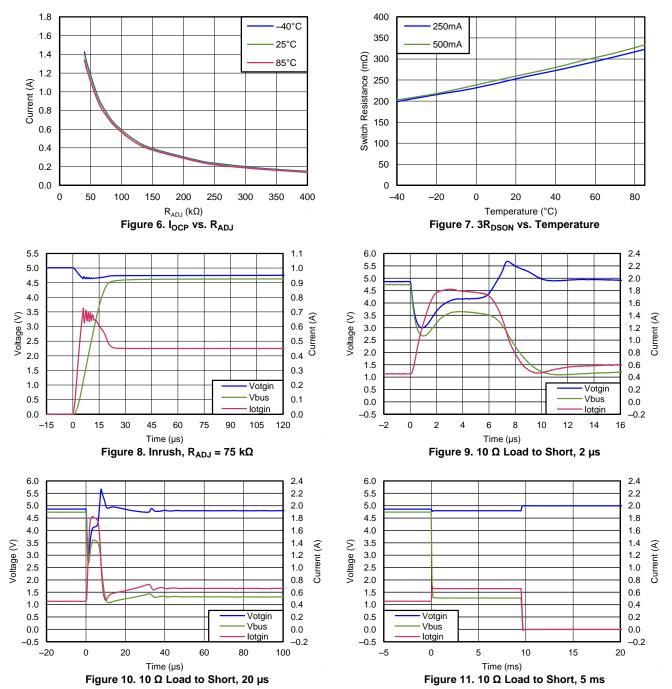

The TPD4S214 provides current limiting function, which is set by an external resistor connected from the ADJ pin to ground shown in Figure 26. The current limiting threshold I<sub>OCP</sub> is set by the external resistor R<sub>ADJ</sub>. Figure 6 shows the minimum, typical, and maximum current limit for a corresponding R<sub>ADJ</sub> value with ±1% tolerance.

Where:

14

$\mathsf{R}_{\mathsf{ADJ}} = \frac{55.358}{\mathsf{I}_{\mathsf{OCP}}}$

Submit Documentation Feedback

$R_{AD,I}$  = external resistor used to set the current limit (k $\Omega$ )

$I_{OCP}$  = current limit set by the external  $R_{ADJ}$  resistor (A)

R<sub>ADJ</sub> is placed between the ADJ pin and ground, shown in the figure above, providing a minimum current limit between 250 mA and 1.2 A.

Figure 26.

(1)

#### **V<sub>BUS</sub> Detection**

There are several important protocols defined in [OTG and EH Supplement] that governs communication between Targeted Hosts (A-device) and USB peripherals (B-device). Communication between host and peripheral is usually done on the ID pin only. In case when two OTG devices that could both act as either host or peripheral are connected, measuring voltage level on  $V_{BUS}$  will aid in the handshaking process. If an embedded host instead of a USB device is connected to the OTG device, OTG charging would not be required and the system's OTG source should remain off to conserve power. The TPD4S214  $V_{BUS}$  detection block aids power conservation and is powered from  $V_{BUS}$ . See figure 3. The DET pin is an open drain PMOS output with default state low.

In the event when an A-plug is attached, the system detects ID pin as FALSE, in which case ID pin resistance to ground is less than 10  $\Omega$ . For a B-plug, the system detects ID pin as TRUE and ID pin resistance to ground is greater than 100 k $\Omega$ . For the system to power a USB device through OTG switch once it is connected, voltage on V<sub>BUS</sub> should remain below V<sub>BUS\_VALID</sub> MIN within T<sub>A\_VBUS\_ATT</sub> of the ID pin becoming FALSE. After this event, the system confirms that the USB device requires power and enables both TPD4S214 and OTG source. However, if V<sub>BUS\_VALID</sub> is detected on V<sub>BUS</sub> within T<sub>A\_VBUS\_ATT</sub> of the ID pin becoming FALSE, there is either a system error or the device connected does not require charging. OTG source remains switched off and the entire sequence would restart when the system detects another FALSE on the ID pin.

#### Table 3. V<sub>BUS</sub> Detection scheme

| EN | V <sub>OTG_IN</sub> (V <sub>BUS</sub> Detect Power) | V <sub>BUS</sub>                                         | DET | Condition                                                  |

|----|-----------------------------------------------------|----------------------------------------------------------|-----|------------------------------------------------------------|

| Х  | х                                                   | $V_{BUS_VALID} < V_{BUS} < V_{BUS_VALID}$ +              | Н   | $V_{BUS}$ within $V_{BUS_VALID}$                           |

| Х  | Х                                                   | $V_{BUS_VALID} > V_{BUS}$ or $V_{BUS} > V_{BUS_VALID}$ + | L   | $V_{\text{BUS}}$ outside of $V_{\text{BUS}\_\text{VALID}}$ |

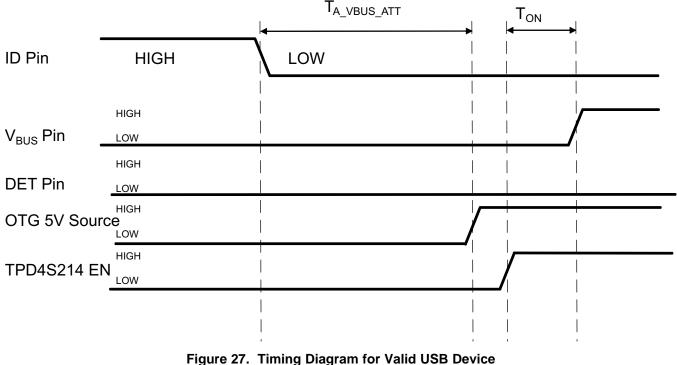

Figure 27 and Figure 28 shows suggested system level timing diagram for detecting  $V_{BUS}$  according to [OTG and EH Supplement]. Figure 3 shows the application diagram. In Figure 27, DET pin remains low after ID pin becomes FALSE, indicating there is not an active voltage source on  $V_{BUS}$ . The USB controller proceeds to turn on OTG 5V source and the TPD4S214 respectively; this sequence is recommended because TPD4S214 is powered through the OTG source. After a period of  $t_{ON}$ , current starts to flow through the OTG switch and  $V_{BUS}$  is ramped to the voltage level of  $V_{OTG IN}$ .

www.ti.com

In Figure 28, DET pin toggles high after an active voltage is detected on  $V_{BUS}$  within  $T_{A\_VBUS\_ATT}$ . This indicates that the USB device attached is not suitable for OTG charging and both OTV 5V source and TPD4S214 remain off.

Figure 28. System Level Timing Diagram for invalid USB Device

#### **Related Documents**

OTG and EH Supplement] On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification, July 14th, 2011. www.usb.org

27-Feb-2013

#### PACKAGING INFORMATION

| Orderable Device | Status  | Package Type | Package | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|---------|--------------|---------|------|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)     |              | Drawing |      |             | (2)                        |                  | (3)                |              | (4)               |         |

| TPD4S214AYFFR    | PREVIEW | DSBGA        | YFF     | 12   | 3000        | TBD                        | Call TI          | Call TI            | -40 to 85    |                   |         |

| TPD4S214YFFR     | ACTIVE  | DSBGA        | YFF     | 12   | 3000        | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    |                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

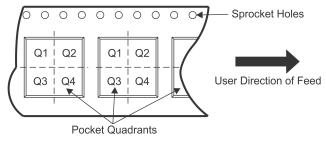

# PACKAGE MATERIALS INFORMATION

Pin1

Quadrant

Q1

www.ti.com

Texas Instruments

#### **TAPE AND REEL INFORMATION**

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

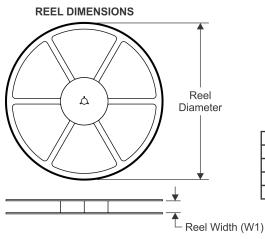

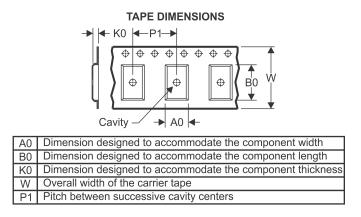

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) |

| TPD4S214YFFR                | DSBGA           | YFF                | 12 | 3000 | 180.0                    | 8.4                      | 1.48       | 1.78       | 0.69       | 4.0        | 8.0       |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

4-Mar-2013

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPD4S214YFFR | DSBGA        | YFF             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

NanoFree is a trademark of Texas Instruments

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated