# PM8851

## 1 A low-side gate driver with configurable asymmetric sink/source

#### Datasheet - production data

## Features

- Low-side MOSFET driver

- 1 A sink and 0.8 A source capability

- Complementary outputs for source and sink driving

- Ext. reference for input threshold

- Wide supply voltage range (10 V ÷ 18 V)

- Input and output pull-down resistors

- Short propagation delays

- Input and output UVLO

- Wide operating temperature range: -40 °C to 125 °C

- SOT23-6L package

## Applications

- SMPS

- Digital lighting

- Wireless battery chargers

- Digitally controlled MOSFETs

## Description

The PM8851 device is a high frequency single channel low-side MOSFET driver specifically designed to work with digital power conversion microcontrollers, such as the STMicroelectronics STLUX<sup>™</sup> family of products.

The PM8851 has complementary output pins to differentiate sink and source driving with a current capability of respectively 1 A and 0.8 A.

The input levels of the driver are derived by the voltage present at the IN\_TH pin (between 2 V and 5.5 V). This pin is typically connected at the same voltage of the microcontroller supply voltage.

The PM8851 includes both input and output pull-down resistors.

UVLO circuitry for input and output stages is present preventing the IC from driving external MOSFET in unsafe condition.

#### Table 1. Device summary

| Order code | Option              | Package  |  |

|------------|---------------------|----------|--|

| PM8851D    | Low input threshold | SOT23-6L |  |

DocID027090 Rev 1

This is information on a product in full production.

October 2014

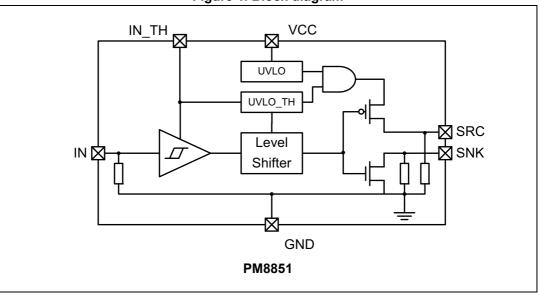

# 1 Block diagram

Figure 1. Block diagram

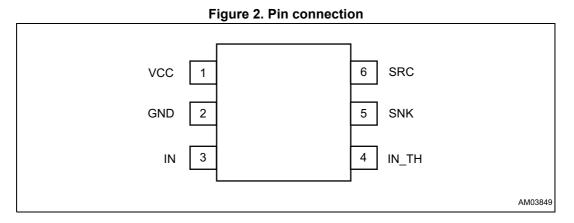

# 2 Pin connection

Table 2. Pinning

| Symbol | Pin | Description                                                                                                                     |

|--------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| VCC    | 1   | IC power supply. A voltage comprised between 10 V and 18 V can be connected between this pin and GND to supply the IC.          |

| GND    | 2   | Reference voltage connection.                                                                                                   |

| IN     | 3   | Digital input signal for driver. It is internally pulled down to GND with a 100 k $\Omega$ (typ.) equivalent resistor.          |

| IN_TH  | 4   | Input for IN pin's threshold definition: a voltage can be applied obtaining the values for VIH and VIL.                         |

| SNK    | 5   | MOSFET gate drive sinking output controlled by the IN pin. A pull-down equivalent resistor [100 k $\Omega$ (typ.)] is present.  |

| SRC    | 6   | MOSFET gate drive sourcing output controlled by the IN pin. A pull-down equivalent resistor [100 k $\Omega$ (typ.)] is present. |

# 3 Maximum ratings

| Symbol            | Parameter                                                                                              | Value      | Unit |

|-------------------|--------------------------------------------------------------------------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient<br>(2-layer FR4 PCB, T <sub>A</sub> = 27 °C natural convection) | 250        | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction to case                                                                    | 130        | °C/W |

| T <sub>MAX</sub>  | Maximum junction temperature                                                                           | 150        | °C   |

| T <sub>STG</sub>  | Storage temperature range                                                                              | -40 to 150 | °C   |

| Τ <sub>J</sub>    | Junction temperature range                                                                             | -40 to 150 | °C   |

| T <sub>A</sub>    | Operating ambient temperature range                                                                    | -40 to 125 | °C   |

| Symbol                 | Parameter                          | Value | Unit | Note                          |

|------------------------|------------------------------------|-------|------|-------------------------------|

| N                      | Maximum IC supply voltage          | 19    | V    | IN unconnected, IN_TH = 3.3 V |

| V <sub>VCC,max</sub>   | Max. negative allowed voltage      | - 0.3 | V    |                               |

| V                      | Max. positive voltage at IN_TH pin | 5.5   | V    |                               |

| V <sub>IN_TH,max</sub> | Max. negative allowed voltage      | - 0.3 | V    |                               |

| V                      | Maximum voltage at IN pin          | 5.5   | V    |                               |

| V <sub>IN,max</sub>    | Max. negative allowed voltage      | - 0.3 | V    |                               |

| I <sub>SRC,rms</sub>   | Maximum RMS output current         | 40    | mA   |                               |

| I <sub>SNK,rms</sub>   | Maximum RMS output current         | 60    | mA   |                               |

## 4 Electrical characteristics

(V\_{CC} = 12 V, V<sub>IN\_TH</sub> = 3.3 V, T<sub>J</sub> = - 40  $\div$  125 °C, unless otherwise specified).

| Symbol                 | Pin        | Parameter                             | Test condition                                                   | Min. | Тур. | Max. | Unit |

|------------------------|------------|---------------------------------------|------------------------------------------------------------------|------|------|------|------|

| IC SUPPLY              | 7          |                                       |                                                                  |      |      | I.   |      |

| V <sub>CC</sub>        | VCC        | Operating range                       |                                                                  | 10   |      | 18   | V    |

| V <sub>CC,on</sub>     | VCC        | Turn-on threshold                     |                                                                  | 9    | 10   | 11   | V    |

| V <sub>UVLO,hyst</sub> | VCC        | UVLO hysteresis                       |                                                                  | 0.5  | 1    |      | V    |

| I <sub>ST-UP</sub>     | VCC        | Start-up current                      | $V_{CC} = V_{CC,on} - 0.5 V$                                     |      |      | 40   | μA   |

| I <sub>CC,0</sub>      | VCC        | Static supply current                 | IN = 0 V                                                         |      |      | 40   | μA   |

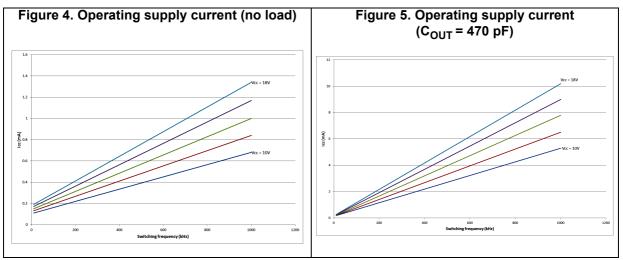

| I <sub>CC,op</sub>     | VCC        | Operating supply current              | See Figure 4 and Figure 5                                        |      |      |      |      |

| IN_TH                  |            |                                       |                                                                  |      |      |      |      |

| V <sub>IN_TH</sub>     | IN_TH      | Operating range                       |                                                                  | 2    |      | 5.5  | V    |

| V <sub>IN_TH,UV</sub>  | IN_TH      | IN_TH UVLO                            | IN_TH short with IN, rising edge                                 |      | 1.5  |      | V    |

| I <sub>IN_TH</sub>     | IN_TH      | IN_TH pin bias current <sup>(1)</sup> |                                                                  |      |      | 40   | μA   |

| INPUT                  |            |                                       |                                                                  |      |      |      |      |

| $V_{IH}/V_{IN_{TH}}$   | IN         | Relative input high level threshold   | (2)                                                              | 36   |      | 58   | %    |

| $V_{IL}/V_{IN_{TH}}$   | IN         | Relative input low level threshold    | (2)                                                              | 25   |      | 46   | %    |

| V <sub>IN_Hyst</sub>   | IN         | Hysteresis                            |                                                                  | 7    |      | 25   | %    |

| I <sub>IN</sub>        | IN         | IN pin bias current                   | VIN = 5 V                                                        |      | 50   |      | μA   |

| R <sub>INPD</sub>      | IN         | Input pull-down resistance            | VIN = V <sub>IN_TH</sub>                                         |      | 100  |      | kΩ   |

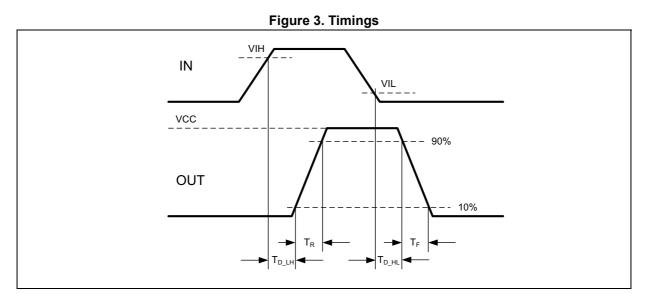

| T <sub>D_LH</sub>      | IN         | IN to GD propagation delay            | IN low to high, no load                                          |      |      | 30   | ns   |

| T <sub>D_HL</sub>      | IN         | IN to GD propagation delay            | IN high to low, no load                                          |      |      | 30   | ns   |

| OUTPUT                 |            |                                       |                                                                  |      |      |      |      |

| M                      | SRC        | SRC pin high level (when invoked      | Isrc = 100 mA, T <sub>J</sub> = 25°C                             |      | 11.4 |      | V    |

| V <sub>SRC,H</sub>     | SILC       | by IN pin)                            | Isrc = 100 mA, T <sub>J</sub> =- 40 $\div$ 125 °C <sup>(1)</sup> |      | 11.4 |      |      |

| V                      | SNK        | SRC pin low level (when invoked       | Isnk =100 mA, T <sub>J</sub> = 25°C                              |      | 0.53 |      | V    |

| V <sub>SNK,L</sub>     | ONIX       | by IN pin)                            | Isnk =100 mA, T <sub>J</sub> =- 40 ÷ 125 °C <sup>(1)</sup>       |      | 0.53 |      |      |

| I <sub>SRC</sub>       | SRC        | Source current <sup>(1)</sup>         | $V_{SRC} = V_{CC} / 2$                                           |      | 940  |      | mA   |

| I <sub>SNK</sub>       | SNK        | Sink current <sup>(1)</sup>           | $V_{SNK} = V_{CC} / 2$                                           |      | 1.1  |      | Α    |

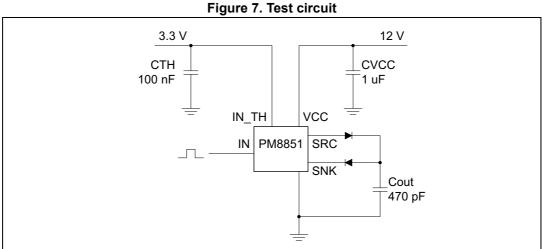

| t <sub>R</sub>         | SRC        | Rise time                             | C <sub>OUT</sub> = 470 pF                                        |      |      | 20   | ns   |

| t <sub>F</sub>         | SNK        | Fall time                             | C <sub>OUT</sub> = 470 pF                                        |      |      | 20   | ns   |

| R <sub>GPD</sub>       | SRC<br>SNK | Pull-down resistor                    |                                                                  |      | 100  |      | kΩ   |

#### Table 5. Electrical characteristics

1. Not tested in production.

2. Overlapping prevent by hysteresis  $V_{IN\_Hyst}$ .

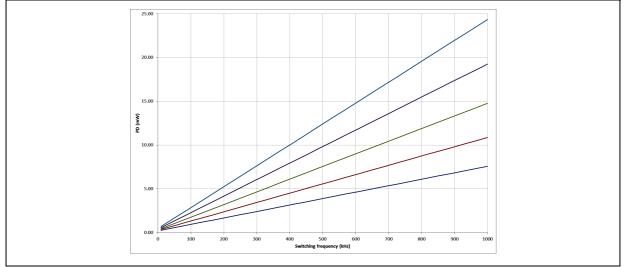

Figure 6.  $V_{CC}$  power dissipation (PD) when no load is applied

DocID027090 Rev 1

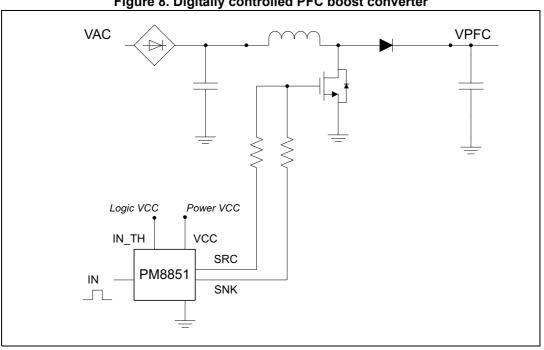

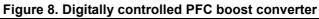

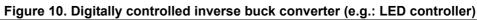

#### **Typical applications** 5

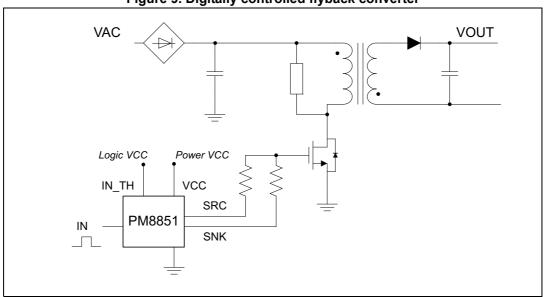

Figure 9. Digitally controlled flyback converter

## 6 Application guidelines

### 6.1 **Power supply**

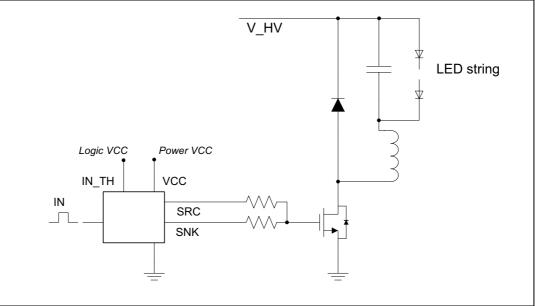

The PM8851 driver is intended to drive power MOSFETs used in power conversion topologies at high speed. The accurate supply voltage definition guarantees an effective driving in every condition. The voltage present at the IN\_TH pin is used for the threshold definition. It could be the same voltage used to supply the device providing the signal applied to the IN pin, or it can be derived by the VCC pin, eventually using a voltage divider. It is mainly suggested to provide IN\_TH voltage starting from VCC voltage.

For example, an auxiliary, unregulated voltage can be used to be connected to both PM8851 VCC pin and the input of a linear regulator that provides a well regulated supply voltage for logic circuitry. The same low voltage is then provided to the IN\_TH pin of the PM8851.

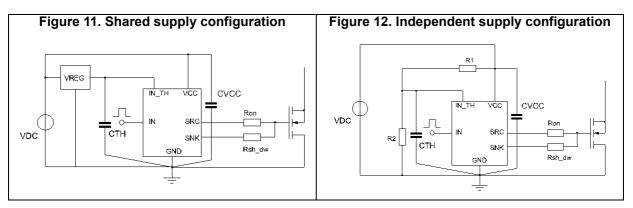

If the IN\_TH is derived directly by the VCC pin, the structure illustrated in *Figure 12* can be used.

It is mandatory to properly connect a 100 nF ceramic cap as close as possible to the VCC pin to bypass the current's spikes absorbed by VCC during the gate charging.

Also IN\_TH voltage should be filtered with a ceramic capacitor (10 nF to 100 nF), especially when long traces are used to supply it; when derived by VCC a lighter filtering is allowed.

### 6.2 Layout suggestions

The small package of the PM8851 allows to place it very close to the gate of the driven MOSFET: this reduces the risk of injecting high frequency noise produced by the driving current running between the OUT pin and the MOSFET's gate pin.

## 6.3 Driving switches

The IN pin truth table is reported in Table 6.

| Table 6. PM8851 truth table (levels refer to unloaded condition of SNK and | J SRC) |

|----------------------------------------------------------------------------|--------|

|----------------------------------------------------------------------------|--------|

| IN   | PM8851 |      |  |  |

|------|--------|------|--|--|

|      | SRC    | SNK  |  |  |

| High | Vcc    | Hi-Z |  |  |

| Low  | Hi-Z   | GND  |  |  |

Differential MOSFET's driving strength is seldom necessary in topologies such as flybacks or boost controlled in the peak current mode. A lower driving current is used to turn-on the MOSFET in order to reduce the EMI produced by the Miller capacitance activation, while a stronger turn-off action is suggested to minimize the turn-off delay and, consequently the deviation between theoretical and practical behaviors.

The same asymmetrical driving strength is required when the IGBT switch is used: in fact the driving strength control is mandatory to avoid latch-up phenomena intrinsically related with this kind of the switch. The asymmetrical driving can be realized using different values for the resistances placed between the MOSFET's gate and the SRC and SNK pins.

When low switching frequencies are required and propagation delays can be compensated, it is possible to drive contemporary the IN pin and the IN\_TH pin to exploit the relevant UVLO threshold of the device (typ. 1.5 V) using the PM8851 as a fixed threshold device without any external component: care has to be taken to consider additional propagation delay (typ. 300 ns) after the falling edge of the input signal.

## 6.4 **Power dissipation**

Overall power dissipation can be evaluated considering two main contributions: the device related consumption (PD) and the gate driving power demand (PG):

#### **Equation 1**

$P_{Tot} = P_D + P_G$

The device power consumption can be found in *Figure 6 on page 6*, it represents the power required by the device to supply internal structures and pull-downs resistors.

The gate driving power dissipation is the power required to deliver to and from the MOSFET's gate the required gate charge:

### Equation 2

$$P_G = Q_g \times V_{gs} \times f_{sw}$$

The  ${\rm Q}_g$  value can be found depicted into the MOSFET's datasheet for any applied  ${\rm V}_{gs}$ :  ${\rm V}_{gs}$  can be considered equal to VCC.

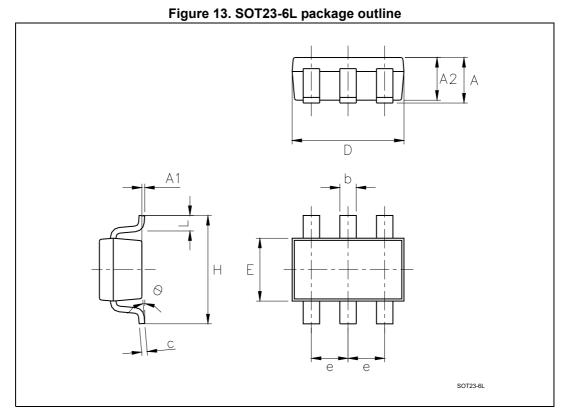

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK is an ST trademark.

|             | Dimensions <sup>(1)</sup> |      |      |       |       |        |

|-------------|---------------------------|------|------|-------|-------|--------|

| Symbol      | mm                        |      |      | inch  |       |        |

|             | Min.                      | Тур. | Max. | Min.  | Тур.  | Max.   |

| А           |                           | 0.9  | 1.45 |       | 0.035 | 0.057  |

| A1          |                           | 0    | 0.1  |       | 0     | 0.0039 |

| A2          |                           | 0.9  | 1.3  |       | 0.035 | 0.0512 |

| b           |                           | 0.35 | 0.5  |       | 0.014 | 0.02   |

| с           |                           | 0.09 | 0.2  |       | 0.004 | 0.008  |

| D           |                           | 2.8  | 3.05 |       | 0.11  | 0.120  |

| E           |                           | 1.5  | 1.75 |       | 0.059 | 0.0689 |

| e           | 0.95                      |      |      | 0.037 |       |        |

| Н           |                           | 2.6  | 3    |       | 0.102 | 0.118  |

| L           |                           | 0.1  | 0.6  |       | 0.004 | 0.024  |

| ⊖ (degrees) |                           | 0°   | 10°  |       | 0°    | 10°    |

1. Dimensions per JEDEC MO178AB.

# 8 Revision history

| Table 8 | Document | revision | history |

|---------|----------|----------|---------|

|---------|----------|----------|---------|

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 23-Oct-2014 | 1        | Initial release. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics – All rights reserved

DocID027090 Rev 1