#

## Integrated 8-Channel LED Drivers with Switch-Mode Boost and SEPIC Controller

### **General Description**

The MAX16807/MAX16808 are integrated, high-efficiency white or RGB LED drivers. They are designed for LCD backlighting and other LED lighting applications with multiple strings of LEDs. The MAX16807/ MAX16808's current-mode PWM controller regulates the necessary voltage to the LED array. Depending on the input voltage and LED voltage range, it can be used with boost or buck-boost (SEPIC) topologies. The MAX16807/MAX16808 feature an 8V to 26.5V input voltage range. A wide range of adjustable frequency (20kHz to 1MHz) allows design optimization for efficiency and minimum board space.

The MAX16807/MAX16808 LED drivers include eight open-drain, constant-current-sinking LED driver outputs rated for 36V continuous operation. The LED current-control circuitry achieves ±3% current matching among strings and enables paralleling of outputs for LED string currents higher than 55mA. The output-enable pin is used for simultaneous PWM dimming of all output channels. Dimming frequency range is 50Hz to 30kHz and dimming ratio is up to 5000:1. The constant-current outputs are single resistor programmable and the LED current can be adjusted up to 55mA per output channel.

The MAX16807/MAX16808 operate either in stand-alone mode or with a microcontroller ( $\mu$ C) using an industry-standard, 4-wire serial interface. The MAX16808 includes circuitry that automatically detects open-circuit LEDs.

The MAX16807/MAX16808 include overtemperature protection, operate over the full -40°C to +125°C temperature range, and are available in a thermally enhanced, 28-pin TSSOP exposed paddle package.

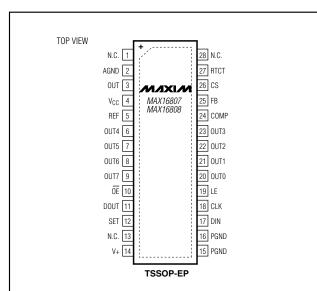

Pin Configurations appear at end of data sheet.

### Features

- Eight Constant-Current Output Channels (Up to 55mA Each)

- ♦ ±3% Current Matching Among Outputs

- Paralleling Channels Allows Higher Current per LED String

- Outputs Rated for 36V Continuous Voltage

- ♦ Output-Enable Pin for PWM Dimming (Up to 30kHz)

- One Resistor Sets LED Current for All Channels

- ♦ Wide Dimming Ratio Up to 5000:1

- Low Current-Sense Reference (300mV) for High Efficiency

- ♦ 8V to 26.5V Input Voltage or Higher with External Biasing Devices

- Open LED Detection (MAX16808)

- 4-Wire Serial Interface to Control Individual Output Channels

### \_Applications

LCD White or RGB LED Backlighting: LCD TVs, Desktop, and Notebook Panels Automotive Navigation, Heads-Up, and Infotainment Displays Industrial and Medical Displays

Ambient, Mood, and Accent Lighting

### Ordering Information

| PART          | TEMP<br>RANGE   | PIN-PACKAGE   | PKG<br>CODE |  |  |

|---------------|-----------------|---------------|-------------|--|--|

| MAX16807AUI+  | -40°C to +125°C | 28 TSSOP-EP** | U28ME-1     |  |  |

| MAX16808AUI+* | -40°C to +125°C | 28 TSSOP-EP** | U28ME-1     |  |  |

|               |                 |               |             |  |  |

+Denotes lead-free package.

\*Future product—contact factory for availability.

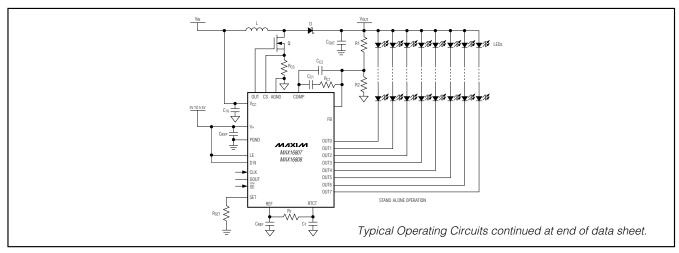

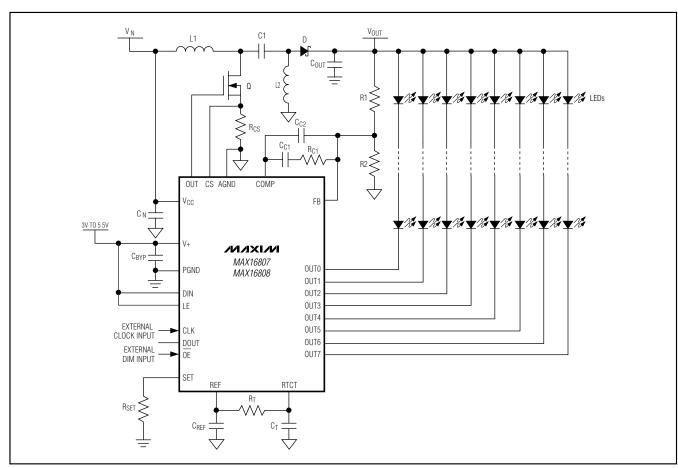

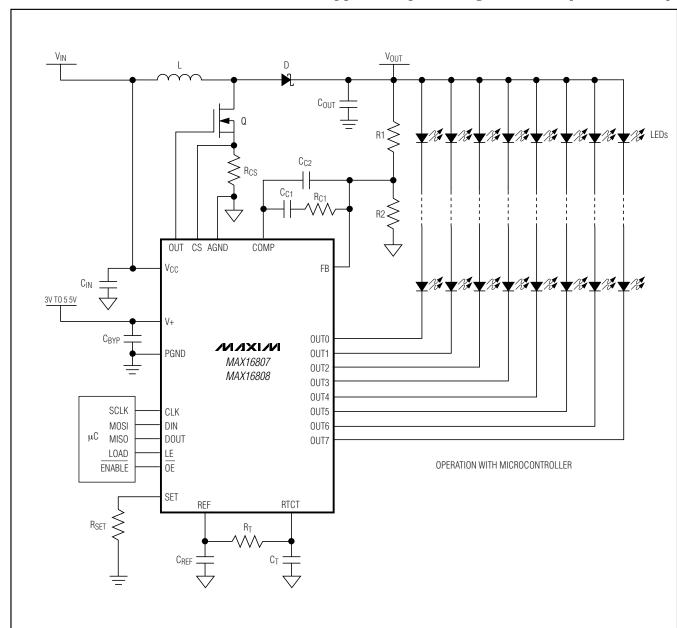

### **Typical Operating Circuits**

###

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>\*\*</sup>EP = Exposed paddle.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to AGND                              | 0.3V to +30V                     |

|------------------------------------------------------|----------------------------------|

| Current into V <sub>CC</sub> (V <sub>CC</sub> > 24V) | ±30mA                            |

| V+ to PGND                                           | 0.3V to +6V                      |

| OUT to AGND                                          | 0.3V to (V <sub>CC</sub> + 0.3V) |

| OUT Current (10µs duration)                          | ±1A                              |

| FB, COMP, CS, RTCT, REF to AGND                      |                                  |

| COMP Sink Current                                    | 10mA                             |

| OUT0-OUT7 to PGND                                    | 0.3V to +40V                     |

| DIN, CLK, LE, OE, SET to PGND                        | 0.3V to (V+ + 0.3V)              |

| DOUT Current                                         |                                  |

| OUT0-OUT7 Sink Current60m                             | ۱A |

|-------------------------------------------------------|----|

| Total PGND Current                                    | ٦A |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |    |

| 28-Pin TSSOP (derate 27mW/°C* above +70°C)2162m       | W  |

| Operating Temperature Range40°C to +125°              | °C |

| Junction Temperature+150                              | ъС |

| Storage Temperature Range65°C to +150°                | °C |

| Lead Temperature (soldering, 10s)+300                 | °C |

|                                                       |    |

\*Per JEDEC51 Standard (Multilayer Board).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS (PWM CONTROLLER)**

$(V_{CC} = +15V, V_{+} = +3V \text{ to } +5.5V \text{ referenced to PGND}, R_T = 10k\Omega, C_T = 3.3nF, REF = open, COMP = open, C_{REF} = 0.1\mu F, V_{FB} = 2V, CS = AGND, AGND = PGND = 0V; all voltages are measured with respect to AGND, unless otherwise noted. T_J = T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                      | SYMBOL             | CONDITIONS                                                        | MIN   | ТҮР   | MAX   | UNITS |

|--------------------------------|--------------------|-------------------------------------------------------------------|-------|-------|-------|-------|

| REFERENCE                      |                    |                                                                   | •     |       |       | •     |

| Output Voltage                 | V <sub>REF</sub>   | $I_{\text{REF}} = 1\text{mA}, T_{\text{J}} = +25^{\circ}\text{C}$ | 4.95  | 5     | 5.05  | V     |

| Line Regulation                | $\Delta V_{LINE}$  | 12V< V <sub>CC</sub> < 25V, I <sub>REF</sub> = 1mA                |       | 0.4   | 4     | mV    |

| Load Regulation                | $\Delta V_{LOAD}$  | 1mA < I <sub>REF</sub> < 20mA                                     |       | 6     | 50    | mV    |

| Total Output-Voltage Variation | VREFT              | (Note 2)                                                          | 4.875 |       | 5.125 | V     |

| Output Noise Voltage           | VNOISE             | 10Hz < f < 10kHz                                                  |       | 50    |       | μV    |

| Output Short-Circuit Current   | ISHORT             | $V_{REF} = 0V$                                                    | 30    |       | 180   | mA    |

| OSCILLATOR                     |                    |                                                                   |       |       |       |       |

| Initial Accuracy               |                    | $T_J = +25^{\circ}C$                                              | 51    | 54    | 57    | kHz   |

| Voltage Stability              |                    | 12V < V <sub>CC</sub> < 25V                                       |       | 0.2   | 0.5   | %     |

| Temperature Stability          |                    |                                                                   |       | 1     |       | %     |

| RTCT Ramp Peak-to-Peak         |                    |                                                                   |       | 1.7   |       | V     |

| RTCT Ramp Valley               |                    |                                                                   |       | 1.1   |       | V     |

| Diachargo Current              | le ve              | $V_{RTCT} = 2V, T_J = +25^{\circ}C$                               | 7.9   | 8.3   | 8.7   | mA    |

| Discharge Current              | IDIS               | $V_{RTCT} = 2V, -40^{\circ}C \le T_J \le +125^{\circ}C$           | 7.5   | 8.3   | 9.0   | MA    |

| Frequency Range                | fosc               |                                                                   | 20    |       | 1000  | kHz   |

| ERROR AMPLIFIER                |                    |                                                                   |       |       |       |       |

| FB Input Voltage               | V <sub>FB</sub>    | FB shorted to COMP                                                | 2.45  | 2.50  | 2.55  | V     |

| Input Bias Current             | I <sub>B(FB)</sub> |                                                                   |       | -0.01 | -0.1  | μA    |

| Open-Loop Gain                 | Avol               | $2V \le V_{COMP} \le 4V$                                          |       | 100   |       | dB    |

| Unity-Gain Bandwidth           | fgbw               |                                                                   |       | 1     |       | MHz   |

| Power-Supply Rejection Ratio   | PSRR               | $12V \le V_{CC} \le 25V$                                          | 60    | 80    |       | dB    |

| COMP Sink Current ISINK        |                    | $V_{FB} = 2.7V, V_{COMP} = 1.1V$                                  | 2     | 6     |       | mA    |

| COMP Source Current            | ISOURCE            | $V_{FB} = 2.3V, V_{COMP} = 5V$                                    | 0.5   | 1.2   | 1.8   | mA    |

| COMP Output-Voltage High       | VOH                | $V_{FB} = 2.3V, R_{COMP} = 15k\Omega$ to AGND                     | 5     | 5.8   |       | V     |

| COMP Output-Voltage Low        | Vol                | $V_{FB}$ = 2.7V, $R_{COMP}$ = 15k $\Omega$ to $V_{REF}$           |       | 0.1   | 1.1   | V     |

### ELECTRICAL CHARACTERISTICS (PWM CONTROLLER) (continued)

$(V_{CC} = +15V, V_{+} = +3V \text{ to } +5.5V \text{ referenced to PGND}, R_T = 10k\Omega, C_T = 3.3nF, REF = open, COMP = open, C_{REF} = 0.1\muF, V_{FB} = 2V, CS = AGND, AGND = PGND = 0V; all voltages are measured with respect to AGND, unless otherwise noted. T_J = T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                                  | CONDITIONS           | MIN                      | TYP                                                               | MAX   | UNITS |       |    |

|--------------------------------------------|----------------------|--------------------------|-------------------------------------------------------------------|-------|-------|-------|----|

| CURRENT-SENSE AMPLIFIER                    |                      | •                        |                                                                   | -     |       |       |    |

| Current-Sense Gain                         | Acs                  | 2.85                     | 3.00                                                              | 3.40  | V/V   |       |    |

| Maximum Current-Sense Signal               | VCS_MAX              | (Note 3)                 |                                                                   | 0.275 | 0.300 | 0.325 | V  |

| Power-Supply Rejection Ratio               | PSRR                 | $12V \le V_{CC} \le 25V$ | 1                                                                 |       | 70    |       | dB |

| Current-Sense Input Bias Current           | ICS                  | $V_{COMP} = 0V$          |                                                                   |       | -1    | -2.5  | μA |

| Current Sense to OUT Delay                 | tpwm                 | 50mV overdrive           |                                                                   |       | 60    |       | ns |

| MOSFET DRIVER                              |                      |                          |                                                                   |       |       |       |    |

| OUT Low-Side On-Resistance                 |                      | ISINK = 200mA            | $T_J = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Note 2)}$    |       | 4.5   | 10    | Ω  |

| OUT Low-Side On-Resistance                 | VRDS_ONL             | ISINK = 200MA            | $T_{\rm J} = -40^{\circ}{\rm C} \text{ to } + 125^{\circ}{\rm C}$ |       | 4.5   | 12    | 52 |

| OUT High-Side On-Resistance                |                      | ISOURCE =                | $T_J = -40^{\circ}C$ to $+85^{\circ}C$ (Note 2)                   |       | 3.5   | 7.5   | Ω  |

| OUT HIgh-Side On-Resistance                | V <sub>RDS_ONH</sub> | 100mA                    | $T_J = -40^{\circ}C \text{ to } + 125^{\circ}C$                   |       | 3.5   | 10    | 52 |

| Source Current (Peak)                      | ISOURCE              | $C_{LOAD} = 10nF$        |                                                                   |       | 2     |       | А  |

| Sink Current (Peak)                        | I <sub>SINK</sub>    | $C_{LOAD} = 10nF$        | $C_{LOAD} = 10 nF$                                                |       |       |       | А  |

| Rise Time                                  | t <sub>R</sub>       | $C_{LOAD} = 1nF$         |                                                                   | 15    |       | ns    |    |

| Fall Time                                  | tF                   | $C_{LOAD} = 1nF$         |                                                                   |       | 22    |       | ns |

| UNDERVOLTAGE LOCKOUT/ST                    | ARTUP                |                          |                                                                   |       |       |       |    |

| Startup Voltage Threshold                  | VCC_START            |                          |                                                                   | 7.98  | 8.4   | 8.82  | V  |

| Minimum Operating Voltage After<br>Turn-On | VCC_MIN              |                          |                                                                   | 7.1   | 7.6   | 8.0   | V  |

| Undervoltage-Lockout Hysteresis            | UVLOHYST             |                          |                                                                   |       | 0.8   |       | V  |

| PULSE-WIDTH MODULATION (P                  |                      | •                        |                                                                   |       |       |       |    |

| Maximum Duty Cycle                         | DMAX                 |                          |                                                                   | 94.5  | 96    | 97.5  | %  |

| Minimum Duty Cycle                         | D <sub>MIN</sub>     |                          |                                                                   | İ     |       | 0     | %  |

| SUPPLY CURRENT                             |                      | •                        |                                                                   | •     |       |       | •  |

| Startup Supply Current                     | ISTART               | $V_{CC} = 7.5V$          |                                                                   |       | 32    | 65    | μA |

| Operating Supply Current                   | ICC                  | $V_{FB} = V_{CS} = 0V$   |                                                                   |       | 3     | 5     | mA |

| V <sub>CC</sub> Zener Voltage              | Vz                   | I <sub>CC</sub> = 25mA   |                                                                   | 24    | 26.5  |       | V  |

### **ELECTRICAL CHARACTERISTICS (LED DRIVER)**

$(V + = +3V \text{ to } +5.5V, \text{ AGND} = \text{PGND} = 0V; \text{ all voltages are measured with respect to PGND, unless otherwise noted. } T_A = T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                                                 | SYMBOL             | CONDITIONS                                                                                                  | MIN          | ТҮР | MAX         | UNITS |

|---------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------|--------------|-----|-------------|-------|

| Operating Supply Voltage                                                  | V+                 |                                                                                                             | 3.0          |     | 5.5         | V     |

| Output Voltage                                                            | Vout_              |                                                                                                             |              |     | 36          | V     |

| Standby Current (Interface Idle, All<br>Output Ports High Impedance)      |                    | $R_{SET} = 360\Omega$ , DIN, LE, CLK = PGND or V+, $\overline{OE} = V+$ , DOUT unconnected                  |              | 3.6 | 4.5         | mA    |

| Standby Current<br>(Interface Active, All Output Ports<br>High Impedance) |                    | $R_{SET} = 360\Omega$ , $f_{CLK} = 5MHz$ , $\overline{OE} = V+$ ,<br>DIN, LE = PGND or V+, DOUT unconnected |              | 3.8 | 4.8         | mA    |

| Supply Current<br>(Interface Idle, All Output Ports<br>Active Low)        | 1+                 | $R_{SET} = 360\Omega, \overline{OE} = PGND, DIN,$<br>LE = V+, DOUT unconnected                              |              | 17  | 30          | mA    |

| INTERFACE (DIN, CLK, DOUT, LE                                             | , OE)              | •                                                                                                           | •            |     |             |       |

| Input-Voltage High<br>(DIN, CLK, LE, OE)                                  | VIH                |                                                                                                             | 0.7<br>x V+  |     |             | V     |

| Input-Voltage Low<br>(DIN, CLK, LE, OE)                                   | VIL                |                                                                                                             |              |     | 0.3<br>x V+ | V     |

| Hysteresis Voltage<br>(DIN, CLK, LE, OE)                                  | VHYST              |                                                                                                             |              | 0.8 |             | V     |

| Input Leakage Current<br>(DIN, CLK)                                       | ILEAK              |                                                                                                             | -1           |     | +1          | μA    |

| OE Pullup Current to V+                                                   | IOE                | $V + = 5.5V, \overline{OE} = PGND$                                                                          | 0.25         | 1.5 | 25.0        | μA    |

| LE Pulldown Current to PGND                                               | ILE                | V+ = 5.5V, LE = V+                                                                                          | 0.25         | 1.5 | 25.0        | μA    |

| Output-Voltage High (DOUT)                                                | V <sub>OH</sub>    | I <sub>SOURCE</sub> = 4mA                                                                                   | V+<br>- 0.5V |     |             | V     |

| Output-Voltage Low (DOUT)                                                 | V <sub>OL</sub>    | I <sub>SINK</sub> = 4mA                                                                                     |              |     | 0.5         | V     |

|                                                                           |                    | 0°C $\leq$ T <sub>A</sub> $\leq$ +125°C, V <sub>OUT</sub> = 1V to 2.5V, R <sub>SET</sub> = 360 $\Omega$     | 46.5         | 50  | 53.5        | m (   |

| OUT_ Output Current                                                       | IOUT_              | $T_{A} = -40^{\circ}C, V_{OUT} = 1V \text{ to } 2.5V,$<br>R <sub>SET</sub> = 360 $\Omega$                   | 43           |     | 57          | mA    |

| OUT_ Leakage Current                                                      |                    | $\overline{OE} = V+$                                                                                        |              |     | 1           | μA    |

| OUT_ Fault Detection Threshold<br>(MAX16808)                              | V <sub>OUTTH</sub> | $V + = 5.5V, \overline{OE} = V +$                                                                           |              | 0.8 |             | V     |

### **5V TIMING CHARACTERISTICS**

$(V + = +4.5V \text{ to } +5.5V, \text{AGND} = \text{PGND} = 0V; \text{ all voltages are measured with respect to PGND, unless otherwise noted. } T_A = T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Notes 1, 5)

| PARAMETER                        | SYMBOL            | CONDITION                            | MIN | ТҮР | МАХ | UNITS |

|----------------------------------|-------------------|--------------------------------------|-----|-----|-----|-------|

| INTERFACE TIMING CHARACTE        | RISTICS           | •                                    |     |     |     |       |

| CLK Clock Period                 | tCP               |                                      | 40  |     |     | ns    |

| CLK Pulse-Width High             | tсн               |                                      | 19  |     |     | ns    |

| CLK Pulse-Width Low              | tCL               |                                      | 19  |     |     | ns    |

| DIN Setup Time                   | tDS               |                                      | 4   |     |     | ns    |

| DIN Hold Time                    | tDH               |                                      | 8   |     |     | ns    |

| DOUT Propagation Delay           | t <sub>DO</sub>   |                                      | 12  |     | 50  | ns    |

| DOUT Rise Time                   | tDR               | C <sub>DOUT</sub> = 10pF, 20% to 80% |     |     | 10  | ns    |

| DOUT Fall Time                   | tDF               | C <sub>DOUT</sub> = 10pF, 80% to 20% |     |     | 10  | ns    |

| LE Pulse-Width High              | tLW               |                                      | 20  |     |     | ns    |

| LE Setup Time                    | tLS               |                                      | 15  |     |     | ns    |

| LE Rising to OUT_ Rising Delay   | tLRR              | (Note 6)                             |     |     | 110 | ns    |

| LE Rising to OUT_ Falling Delay  | tLRF              | (Note 6)                             |     |     | 325 | ns    |

| CLK Rising to OUT_ Rising Delay  | t <sub>CRR</sub>  | (Note 6)                             |     |     | 110 | ns    |

| CLK Rising to OUT_ Falling Delay | tCRF              | (Note 6)                             |     |     | 325 | ns    |

| OE Rising to OUT_ Rising Delay   | t <del>oe</del> r | (Note 6)                             |     |     | 110 | ns    |

| OE Falling to OUT_ Falling Delay | toef              | (Note 6)                             |     |     | 325 | ns    |

| OUT_ Turn-On Fall Time           | tF                | 80% to 20% (Note 6)                  |     |     | 210 | ns    |

| OUT_ Turn-Off Rise Time          | t <sub>R</sub>    | 20% to 80% (Note 6)                  |     |     | 130 | ns    |

### **3.3V TIMING CHARACTERISTICS**

$(V + = +3V \text{ to} < +4.5V, \text{ AGND} = \text{PGND} = 0V; \text{ all voltages are measured with respect to PGND, unless otherwise noted. TA = TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Notes 1, 5)$

| PARAMETERS                       | PARAMETERS SYMBOL CONDITIONS |                                      |    |  |     | UNITS |

|----------------------------------|------------------------------|--------------------------------------|----|--|-----|-------|

| INTERFACE TIMING CHARACTE        | RISTICS                      |                                      |    |  |     |       |

| CLK Clock Period                 | tCP                          |                                      | 52 |  |     | ns    |

| CLK Pulse-Width High             | tсн                          |                                      | 24 |  |     | ns    |

| CLK Pulse-Width Low              | tCL                          |                                      | 24 |  |     | ns    |

| DIN Setup Time                   | tDS                          |                                      | 4  |  |     | ns    |

| DIN Hold Time                    | tDH                          |                                      | 8  |  |     | ns    |

| DOUT Propagation Delay           | tDO                          |                                      | 12 |  | 70  | ns    |

| DOUT Rise Time                   | tDR                          | C <sub>DOUT</sub> = 10pF, 20% to 80% |    |  | 12  | ns    |

| DOUT Fall Time                   | tDF                          | C <sub>DOUT</sub> = 10pF, 80% to 20% |    |  | 12  | ns    |

| LE Pulse-Width High              | tLW                          |                                      | 20 |  |     | ns    |

| LE Setup Time                    | tLS                          |                                      | 15 |  |     | ns    |

| LE Rising to OUT_ Rising Delay   | t <sub>LRR</sub>             | (Note 6)                             |    |  | 140 | ns    |

| LE Rising to OUT_ Falling Delay  | tLRF                         | (Note 6)                             |    |  | 350 | ns    |

| CLK Rising to OUT_ Rising Delay  | tCRR                         | (Note 6)                             |    |  | 140 | ns    |

| CLK Rising to OUT_ Falling Delay | tCRF                         | (Note 6)                             |    |  | 350 | ns    |

| OE Rising to OUT_ Rising Delay   | t <u>oe</u> r                | (Note 6)                             |    |  | 140 | ns    |

| OE Falling to OUT_ Falling Delay | toef                         | (Note 6)                             |    |  | 350 | ns    |

| OUT_ Turn-On Fall Time           | tF                           | 80% to 20% (Note 6)                  |    |  | 275 | ns    |

| OUT_Turn-Off Rise Time           | t <sub>R</sub>               | 20% to 80% (Note 6)                  |    |  | 150 | ns    |

Note 1: All devices are 100% production tested at  $T_J = +25^{\circ}C$  and  $+125^{\circ}C$ . Limits to  $-40^{\circ}C$  are guaranteed by design.

Note 2: Guaranteed by design, not production tested.

**Note 3:** Parameter is measured at trip point of latch with  $V_{FB} = 0V$ .

**Note 4:** Gain is defined as  $A = \Delta V_{COMP} / \Delta V_{CS}$ ,  $0.05V \le V_{CS} \le 0.25V$ .

Note 5: See Figures 3 and 4.

Note 6: A 65Ω pullup resistor is connected from OUT\_ to 5.5V. Rising refers to V<sub>OUT</sub> when current through OUT\_ is turned off and falling refers to V<sub>OUT</sub> when current through OUT\_ is turned on.

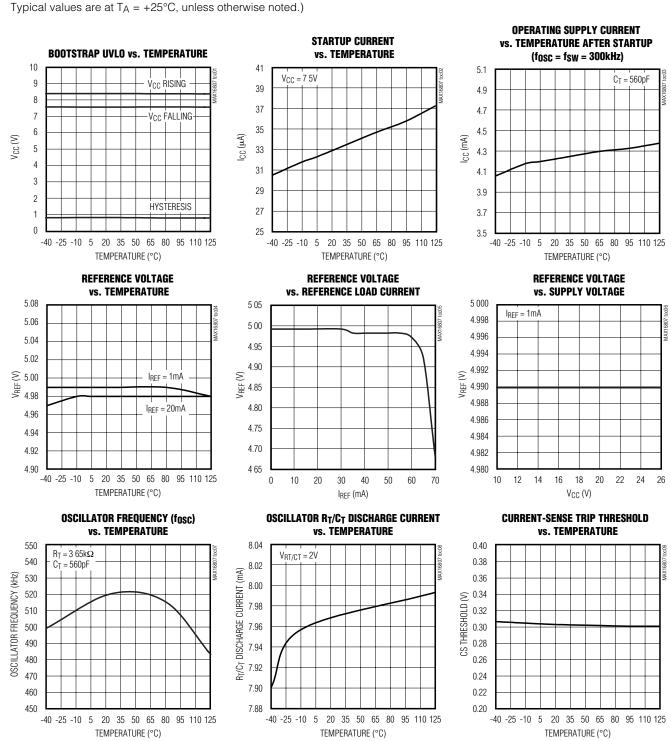

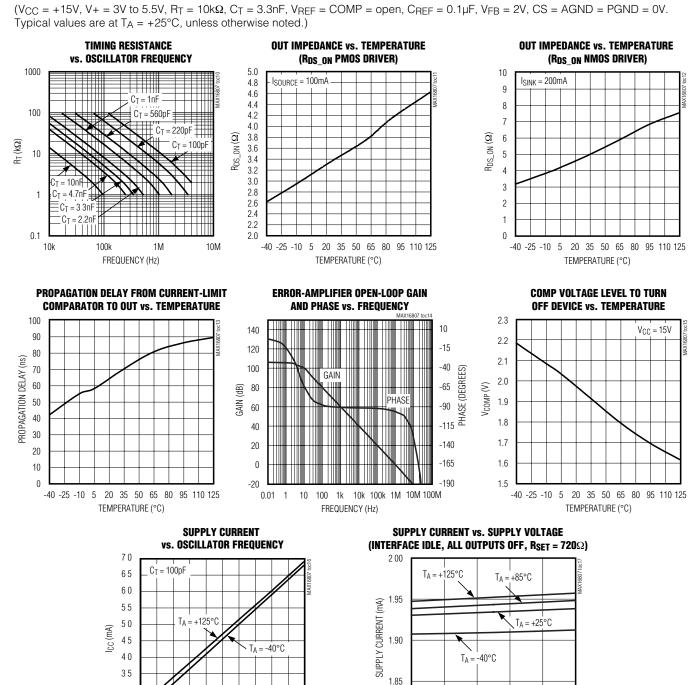

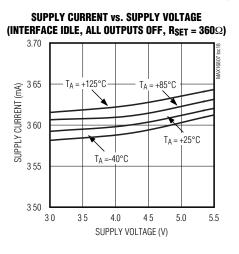

$(V_{CC} = +15V, V_{} + = 3V \text{ to } 5.5V, R_{T} = 10k\Omega, C_{T} = 3.3nF, V_{REF} = COMP = \text{open}, C_{REF} = 0.1\mu\text{F}, V_{FB} = 2V, CS = AGND = PGND = 0V.$

**Typical Operating Characteristics**

///XI///

MAX16807/MAX16808

7

1.85

1.80

3.0

35

40

4.5

**Typical Operating Characteristics (continued)**

MAX16807/MAX16808

8

35

30 25 20

20 120 220 320 420 520 620 720 820 920 1020

FREQUENCY (kHz)

50 5.5 SUPPLY VOLTAGE (V)

MIXIM

### **Typical Operating Characteristics (continued)**

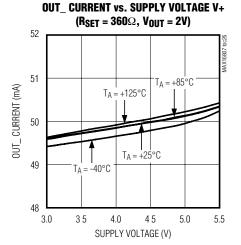

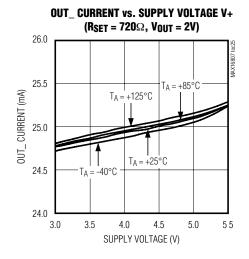

$(V_{CC} = +15V, V_{+} = 3V \text{ to } 5.5V, R_T = 10k\Omega, C_T = 3.3nF, V_{REF} = COMP = open, C_{REF} = 0.1\mu F, V_{FB} = 2V, CS = AGND = PGND = 0V.$ Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

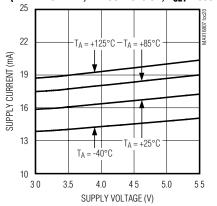

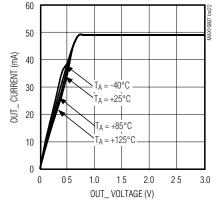

SUPPLY CURRENT vs. SUPPLY VOLTAGE (INTERFACE IDLE, ALL OUTPUTS ON,  $R_{SET} = 360\Omega$ )

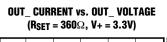

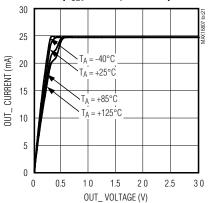

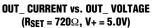

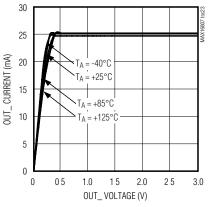

OUT\_ CURRENT vs. OUT\_ VOLTAGE ( $R_{SET} = 720\Omega$ , V+ = 3.3V)

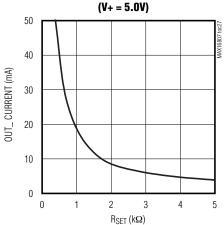

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +15V, V_{+} = 3V \text{ to } 5.5V, R_{T} = 10k\Omega, C_{T} = 3.3nF, V_{REF} = COMP = open, C_{REF} = 0.1\mu F, V_{FB} = 2V, CS = AGND = PGND = 0V.$ Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

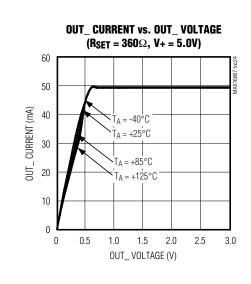

OUT\_CURRENT vs. SET RESISTANCE

### Pin Description

| PIN       | NAME      | FUNCTION                                                                                                                                                                                                                     |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 13, 28 | N.C.      | No Connection. Not internally connected. Leave unconnected.                                                                                                                                                                  |

| 2         | AGND      | Analog Ground                                                                                                                                                                                                                |

| 3         | OUT       | MOSFET Driver Output OUT. Connects to the gate of the external n-channel MOSFET.                                                                                                                                             |

| 4         | VCC       | Power-Supply Input. Bypass $V_{CC}$ to AGND with a 0.1µF ceramic capacitor or a parallel combination of a 0.1µF and a higher value ceramic capacitor.                                                                        |

| 5         | REF       | 5V Reference Output. Bypass REF to AGND with a 0.1µF ceramic capacitor.                                                                                                                                                      |

| 6–9       | OUT4-OUT7 | LED Driver Outputs. OUT4–OUT7 are open-drain, constant-current-sinking outputs rated for 36V.                                                                                                                                |

| 10        | ŌĒ        | Active-Low Output Enable Input. Drive $\overline{OE}$ low to PGND to enable the OUT0–OUT7. Drive $\overline{OE}$ high to disable OUT0–OUT7.                                                                                  |

| 11        | DOUT      | Serial-Data Output. Data is clocked out of the 8-bit internal shift register to DOUT on CLK's rising edge.                                                                                                                   |

| 12        | SET       | LED Current Setting. Connect R <sub>SET</sub> from SET to PGND to set the LED current.                                                                                                                                       |

| 14        | V+        | LED Driver Positive Supply Voltage. Bypass V+ to PGND with a 0.1µF ceramic capacitor.                                                                                                                                        |

| 15, 16    | PGND      | Power Ground                                                                                                                                                                                                                 |

| 17        | DIN       | Serial-Data Input                                                                                                                                                                                                            |

| 18        | CLK       | Serial-Clock Input                                                                                                                                                                                                           |

| 19        | LE        | Latch-Enable Input. Data is loaded transparently from the internal shift register(s) to the output latch(es) while LE is high. Data is latched into the output latch(es) on LE's falling edge, and retained while LE is low. |

| 20–23     | OUT0-OUT3 | LED Driver Outputs. OUT0-OUT3 are open-drain, constant-current-sinking outputs rated for 36V.                                                                                                                                |

| 24        | COMP      | Error-Amplifier Output                                                                                                                                                                                                       |

| 25        | FB        | Error-Amplifier Inverting Input                                                                                                                                                                                              |

| 26        | CS        | PWM Controller Current-Sense Input                                                                                                                                                                                           |

| 27        | RTCT      | PWM Controller Timing Resistor/Capacitor Connection. A resistor $R_T$ from RTCT to REF and a capacitor $C_T$ from RTCT to AGND set the oscillator frequency.                                                                 |

| _         | EP        | Exposed Paddle. Connect to the ground plane for improved power dissipation. Do not use as the only ground connection for the part.                                                                                           |

### **Detailed Description**

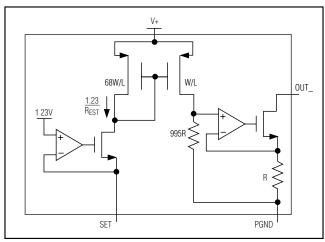

The MAX16807/MAX16808 LED drivers include an internal switch-mode controller that can be used as boost or buck-boost (SEPIC) converters to generate the voltage necessary to drive the multiple strings of LEDs. These devices incorporate an integrated low-side driver, a programmable oscillator (20kHz to 1MHz), an error amplifier, a low-voltage (300mV) current sense for higher efficiency, and a 5V reference to power up external circuitry (see Figures 1a, 1b, and 1c).

The MAX16807/MAX16808 LED drivers include a 4-wire serial interface and a current-mode PWM controller to generate the necessary voltage for driving eight opendrain, constant-current-sinking output ports. The drivers use current-sensing feedback circuitry (not simple current mirrors) to ensure very small current variations over the full allowed range of output voltage (see the *Typical Operating Characteristics*). The 4-wire serial interface comprises an 8-bit shift register and an 8-bit transparent latch. The shift register is written through a clock input, CLK, and a data input, DIN, and the data propagates to a data output, DOUT. The data output allows multiple drivers to be cascaded and operated together. The contents of the 8-bit shift register are loaded into the transparent latch through a latch-enable input, LE. The latch is transparent to the shift register outputs when high and latches the current state on the falling edge of LE. Each driver output is an open-drain, constant-current sink that should be connected to the cath-

ode of a string of LEDs connected in series. The constant-current capability is up to 55mA per output, set for all 8 outputs by an external resistor, R<sub>SET</sub>. The devices can operate in a stand-alone mode (see the *Typical Operating Circuits*.) The MAX16808 includes circuitry that automatically detects open-circuit LEDs. Fault status is loaded into the serial-interface shift register when LE goes high and is automatically shifted out on DOUT when the next data transmission is shifted in. The number of channels can be expanded by using the MAX6970 and MAX6971 family in conjunction with the MAX16807 and MAX16808.

Figure 1a. Internal Block Diagram (MAX16807)

Figure 1b. Internal Block Diagram (MAX16808)

MAX16807/MAX16808

Figure 1c. OUT\_ Driver Internal Diagram

#### Switch-Mode Controller

#### **Current-Mode Control Loop**

The advantages of current-mode control over voltagemode control are twofold. First, there is the feed-forward characteristic brought on by the controller's ability to adjust for variations in the input voltage on a cycleby-cycle basis. Second, the stability requirements of the current-mode controller are reduced to that of a sinale pole system unlike the double pole in the voltagemode control scheme. The MAX16807/MAX16808 use a current-mode control loop where the output of the error amplifier is compared to the current-sense voltage (V<sub>CS</sub>). When the current-sense signal is lower than the inverting input of the CPWM comparator, the output of the comparator is low and the switch is turned on at each clock pulse. When the current-sense signal is higher than the inverting input of the CPWM comparator, the output is high and the switch is turned off.

#### Undervoltage Lockout (UVLO)

The turn-on supply voltage for the MAX16807/ MAX16808 is 8.4V (typ). Once V<sub>CC</sub> reaches 8.4V, the reference powers up. There is a 0.8V of hysteresis from the turn-on voltage to the UVLO threshold. Once V<sub>CC</sub> reaches 8.4V, the MAX16807/MAX16808 operate with V<sub>CC</sub> down to 7.6V (typ). Once V<sub>CC</sub> goes below 7.6V, the device is in UVLO. When in UVLO, the quiescent supply current into V<sub>CC</sub> falls back to  $32\mu$ A (typ), and OUT and REF are pulled low.

#### **MOSFET Driver**

OUT drives an external n-channel MOSFET and swings from AGND to  $V_{CC}$ . Ensure that  $V_{CC}$  remains below the absolute maximum  $V_{GS}$  rating of the external MOSFET.

OUT is a push-pull output with the on-resistance of the pMOS typically  $3.5\Omega$  and the on-resistance of the nMOS typically  $4.5\Omega$ . The driver can source 2A and sink 1A typically. This allows for the MAX16807/MAX16808 to quickly turn on and off high gate-charge MOSFETs. Bypass V<sub>CC</sub> with one or more  $0.1\mu$ F ceramic capacitors to AGND, placed close to the V<sub>CC</sub> pin. The average current sourced to drive the external MOSFET depends on the total gate charge (QG) and operating frequency of the converter. The power dissipation in the MAX16807/MAX16808 is a function of the average output drive current (I<sub>DRIVE</sub>). Use the following equation to calculate the power dissipation in the device due to I<sub>DRIVE</sub>:

$$I_{DRIVE} = (Q_G \times f_{SW})$$

PD = (I\_{DRIVE} + I\_{CC}) \times V\_{CC}

where I<sub>CC</sub> is the operating supply current. See the *Typical Operating Characteristics* for the operating supply current at a given frequency.

#### **Error Amplifier**

The MAX16807/MAX16808 include an internal error amplifier. The inverting input is at FB and the noninverting input is internally connected to a 2.5V reference. Set the output voltage using a resistive divider between output of the converter  $V_{OUT}$ , FB, and AGND. Use the following formula to set the output voltage:

$$V_{OUT} = \left(1 + \frac{R1}{R2}\right) \times V_{FB}$$

where  $V_{FB} = 2.5V$ .

#### Oscillator

The oscillator frequency is programmable using an external capacitor and a resistor at RTCT (see R<sub>T</sub> and C<sub>T</sub> in the *Typical Operating Circuits*). R<sub>T</sub> is connected from RTCT to the 5V reference (REF), and C<sub>T</sub> is connected from RTCT to AGND. REF charges C<sub>T</sub> through R<sub>T</sub> until its voltage reaches 2.8V. C<sub>T</sub> then discharges through an 8.3mA internal current sink until C<sub>T</sub>'s voltage reaches 1.1V, at which time C<sub>T</sub> is allowed to charge through R<sub>T</sub> again. The oscillator's period is the sum of the charge and discharge times of C<sub>T</sub>. Calculate the charge time as follows:

$$t_{\rm C} = 0.57 \times R_{\rm T} \times C_{\rm T}$$

where tc is in seconds, RT in ohms ( $\Omega$ ), and CT in Farads (F).

The discharge time is then:

$t_D = (R_T \times C_T \times 1000) / [(4.88 \times R_T) - (1.8 \times 1000)]$

where t\_D is in seconds, R\_T in ohms ( $\Omega$ ), and C\_T in Farads (F).

The oscillator frequency is then:

$$f_{OSC} = \frac{1}{(t_{C} + t_{D})}$$

#### **Reference Output**

REF is a 5V reference output that can source 20mA. Bypass REF to AGND with a  $0.1\mu$ F capacitor.

#### **Current Limit**

The MAX16807/MAX16808 include a fast current-limit comparator to terminate the on cycle during an overload or a fault condition. The current-sense resistor, R<sub>CS</sub>, connected between the source of the external MOSFET and AGND, sets the current limit. The CS input has a voltage trip level (V<sub>CS</sub>) of 0.3V. Use the following equation to calculate R<sub>CS</sub>:

$$R_{CS} = \frac{V_{CS}}{I_{P-P}}$$

IP-P is the peak current that flows through the MOSFET. When the voltage produced by this current (through the current-sense resistor) exceeds the current-limit comparator threshold, the MOSFET driver (OUT) turns the switch off within 60ns. In most cases, a small RC filter is required to filter out the leading-edge spike on the sense waveform. Set the time constant of the RC filter at 50ns.

#### **Buck-Boost (SEPIC) Operation**

Figure 2 shows a buck-boost application circuit using the MAX16807/MAX16808 in a stand-alone mode of operation. SEPIC topology is necessary when the total forward voltage of the LEDs in a string is such that  $V_{OUT}$  can be below or above  $V_{IN}$ .

Figure 2. Buck-Boost (SEPIC) Configuration

### **LED** Driver

#### **4-Wire Interface**

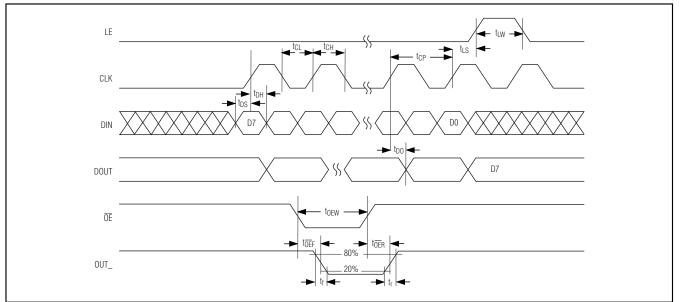

The MAX16807/MAX16808 also operate in a standalone mode (see the *Typical Operating Circuits*). For use with a microcontroller, the MAX16807/MAX16808 feature a 4-wire serial interface using DIN, CLK, LE, OE inputs and DOUT as a data output. This interface is used to write the LED channels' data to the MAX16807/ MAX16808. The serial-interface data word length is 8 bits, D0–D7. See Figure 3.

The functions of the five interface pins are as follows:

DIN is the serial-data input, and must be stable when it is sampled on the rising edge of CLK. Data is shifted in MSB first. This means that data bit D7 is clocked in first, followed by 7 more data bits, finishing with the LSB, D0.

CLK is the serial-clock input that shifts data at DIN into the MAX16807/MAX16808's 8-bit shift register on its rising edge.

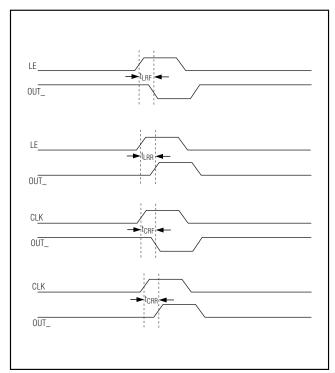

LE is the latch enable input of the MAX16807/ MAX16808 that transfers data from the 8-bit shift register to its 8-bit output latch (transparent latch). The data is latched on the falling edge of LE (Figure 4). The fourth input (OE) provides output-enable control of the output drivers. When  $\overline{OE}$  is driven high, the outputs (OUT0-OUT7) are forced to high impedance without altering the contents of the output latches. Driving  $\overline{OE}$ low enables the outputs to follow the state of the output latches. OE is independent of the operation of the serial interface operation. Data can be shifted into the serialinterface shift register and latched, regardless of the state of OE. DOUT is the serial-data output that shifts data out from the MAX16807/MAX16808's 8-bit shift register on the rising edge of CLK. Data at DIN propagates through the shift register and appears at DOUT eight clock cycles later. Table 1 shows the 4-wire serial-interface truth table.

| SERIAL<br>DATA | CLOCK<br>INPUT | SHIEL REGISTER CONTENTS |    |    |  |      |      | LOAD<br>INPUT | LATCH CONTENTS |    |    |   |      | BLANKING<br>INPUT | OUTPUT CONTENTS<br>CURRENT AT OUT_ |    |    |    |  |      |    |

|----------------|----------------|-------------------------|----|----|--|------|------|---------------|----------------|----|----|---|------|-------------------|------------------------------------|----|----|----|--|------|----|

| INPUT<br>DIN   | CLK            | D0                      | D1 | D2 |  | Dn-1 | Dn   | LE            | D0             | D1 | D2 |   | Dn-1 | Dn                | ŌĒ                                 | D0 | D1 | D2 |  | Dn-1 | Dn |

| Н              |                | Н                       | R0 | R1 |  | Rn-2 | Rn-1 |               |                |    |    |   |      |                   |                                    |    |    |    |  |      |    |

| L              |                | L                       | R0 | R1 |  | Rn-2 | Rn-1 |               |                |    |    |   |      |                   |                                    |    |    |    |  |      |    |

| Х              | 1              | R0                      | R1 | R2 |  | Rn-1 | Rn   |               |                |    |    |   |      |                   |                                    |    |    |    |  |      |    |

|                |                | Х                       | Х  | Х  |  | Х    | Х    | L             | R0             | R1 | R2 |   | Rn-1 | Rn                |                                    |    |    |    |  |      |    |

|                |                | P0                      | P1 | P2 |  | Pn-1 | Pn   | H             | P0             | P1 | P2 | : | Pn-1 | Pn                | L                                  | P0 | P1 | P2 |  | Pn-1 | Pn |

|                |                |                         |    |    |  |      |      |               | Х              | Х  | Х  |   | Х    | Х                 | Н                                  | L  | L  | L  |  | L    | L  |

#### Table 1. 4-Wire Serial-Interface Truth Table

L = Low Logic Level

H = High Logic Level

X = Don't Care

P = Present State (Shift Register)

R = Previous State (Latched)

Figure 3. 4-Wire Serial-Interface Timing Diagram

Figure 4. LE and CLK to OUT\_ Timing

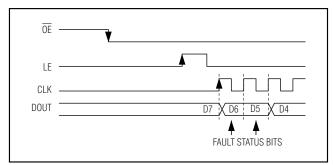

#### **LED Fault Detection (MAX16808)**

The MAX16808 includes circuitry that detects open-circuit LEDs automatically. An open-circuit fault occurs when an output is sinking current less than approximately 50% of the programmed current flows. Open circuits are checked just after the falling edge of  $\overline{OE}$ . The fault data is latched on the rising edge of LE and is shifted out when new LED data is loaded into the output latches from the shift register. If one or more output ports are detected with an open-circuit fault, the D6 and D5 bits of DOUT go high. If no open-circuit faults are detected, D6 and D5 are set to low. The data in the other 6 bit positions in DOUT are not altered. Fault status is shifted out on DOUT for the first two rising edges of the clock after the falling edge of LE (see Figure 5). LE is normally taken high after all 8 bits of new LED

Figure 5. Fault Timing

data have been clocked into the shift register(s), and then DOUT outputs data bit D7. A typical fault-detecting application tests all the shifted out data. Bits D0–D4 and D7 are checked against the originally transmitted data to check data-link integrity. Bits D5 and D6 are checked first to see that they contain the same data (validating the status), and second, whether faults are reported or not by the actual logic level.

#### Selecting External Component RSET to Set LED Output Current

The MAX16807/MAX16808 use an external resistor, RSET, to set the LED current for outputs OUT0–OUT7. The minimum allowed value of RSET is 330 $\Omega$ , which sets the output currents to 55mA. The maximum allowed value of RSET is 5k $\Omega$  (I<sub>OUT</sub> = 3.6mA) and maximum allowed capacitance at SET is 100pF.

Use the following formula to set the output current:

$$R_{\text{SET}} = \frac{18,000}{I_{\text{OUT}}}$$

where  $I_{OUT\_}$  is the desired output current in milliamps and the value for  $R_{SET}$  is in ohms.

#### **Overtemperature Cutoff**

The MAX16807/MAX16808 contain an internal temperature sensor that turns off all outputs when the die temperature exceeds +165°C. The outputs are enabled again when the die temperature drops below +140°C. Register contents are not affected, so when a driver is overdissipating, the external symptom is the load LEDs cycling on and off as the driver repeatedly overheats and cools, alternately turning itself off and then back on again.

#### **Stand-Alone Operation**

In stand-alone operation, the MAX16807/MAX16808 does not use the 4-wire interface (see the *Typical Operating Circuits*). Connect DIN and LE to V+ provide at least 8 external clock pulses to CLK to enable 8 outputs. This startup pulse sequence can be provided either using an external clock or the PWM signal. The external clock can also be generated using the signal at RTCT and an external comparator.

### LED Dimming

#### **PWM Dimming**

All the output channels can be dimmed simultaneously by applying a PWM signal (50Hz to 30kHz) to  $\overline{OE}$ . This allows for a wide range of dimming up to a 5000:1 ratio. Each channel can be independently turned on and off using a 4-wire serial interface. The dimming is proportional to the PWM duty cycle.

#### **LED Current Amplitude Adjustment**

Using an analog or digital potentiometer as R<sub>SET</sub> allows for LED current amplitude adjustment and linear dimming.

#### **Computing Power Dissipation**

Use the following equation to estimate the upper limit power dissipation (PD) for the MAX16807/MAX16808:

$$PD = DUTY \times \left[ (V + x + ) + \sum_{i=0}^{i=7} V_{OUTi} \times I_{OUTi} \right] + (V_{CC} \times I_{CC})$$

where:

V+ = supply voltage

I+ = operating supply current

DUTY = PWM duty cycle applied to  $\overline{OE}$

$V_{OUTi} = MAX16807/MAX16808$  port output voltage when driving load LED(s)

$I_{OUTi}$  = LED drive current programmed by R<sub>SET</sub>

PD = power dissipation.

#### **PCB** Layout Guidelines

Careful PCB layout is critical to achieve low switching losses and clean, stable operation. Use a multilayer board whenever possible for better noise immunity. Protect sensitive analog grounds by using a star ground configuration. Minimize ground noise by connecting AGND, PGND, the input bypass-capacitor ground lead, and the output-filter ground lead to a single point (star ground configuration). Also, minimize trace lengths to reduce stray capacitance, trace resistance, and radiated noise. The trace between the output voltage-divider and the FB pin must be kept short, as well as the trace between AGND and PGND.

### **Pin Configuration**

PROCESS: BICMOS

**Typical Operating Circuits (continued)**

MAX16807/MAX16808

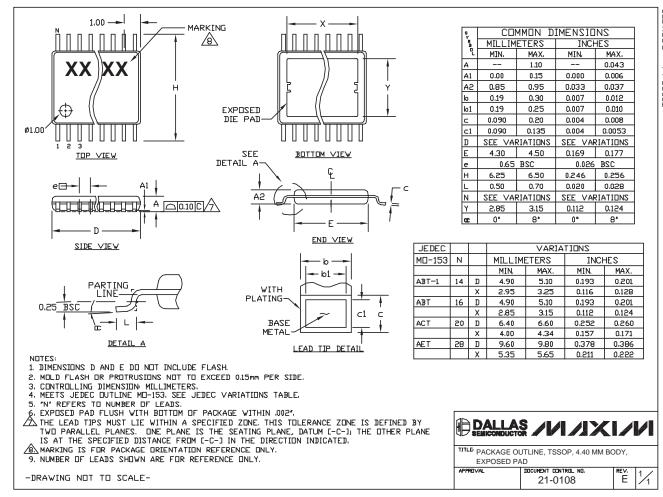

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

is a registered trademark of Maxim Integrated Products, Inc.