Sample &

Buy

LMF100

SNOSBG9B-JULY 1999-REVISED JUNE 2015

Support &

Community

20

# LMF100 Dual High-Performance Switched Capacitor Filters Not Recommended for New Designs

Technical

Documents

#### Features 1

- Wide 4-V to 15-V Power Supply Range

- Operation up to 100 kHz

- Low Offset Voltage:

- Typically (50:1 or 100:1 mode):

- Vos1 =  $\pm$ 5 mV

- Vos2 = ±15 mV

- Vos3 = ±15 mV

- Low Crosstalk: -60 dB

- Clock to Center Frequency Ratio Accuracy ±0.2% (Typical)

- $f_0 \times Q$  Range up to 1.8 MHz

- Pin-Compatible With MF10

# 2 Applications

- Replacing Active RC Filters With Reduced Form Factors and Higher Accuracy and Tunability

- An Alternative to Integrated Continuous Time Filters

# 3 Description

Tools &

Software

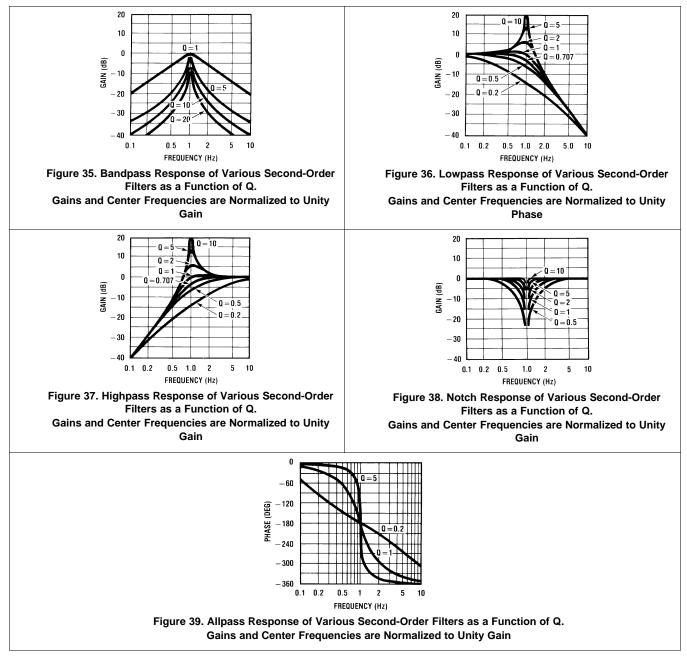

The LMF100 device consists of two independent high-performance general-purpose, switched capacitor filters. With an external clock and two to four resistors, each filter block can realize various second-order and first-order filtering functions. Each block has three outputs. One output can be configured to perform either an allpass, highpass, or notch function. The other two outputs perform bandpass and lowpass functions. The center frequency of each filter stage is tuned by using an external clock or a combination of a clock and resistor ratio. Up to a fourth-order biquadratic function can be realized with one LMF100. Higher order filters are simply implemented by cascading additional packages, and all the classical filters (such as Butterworth, Bessel, Elliptic, and Chebyshev) can be realized.

The LMF100 is fabricated on TI's high-performance analog silicon gate CMOS process, LMCMOS™. This allows for the production of a very low-offset, highfrequency filter building block. The LMF100 is pincompatible with the industry standard MF10, but provides greatly improved performance.

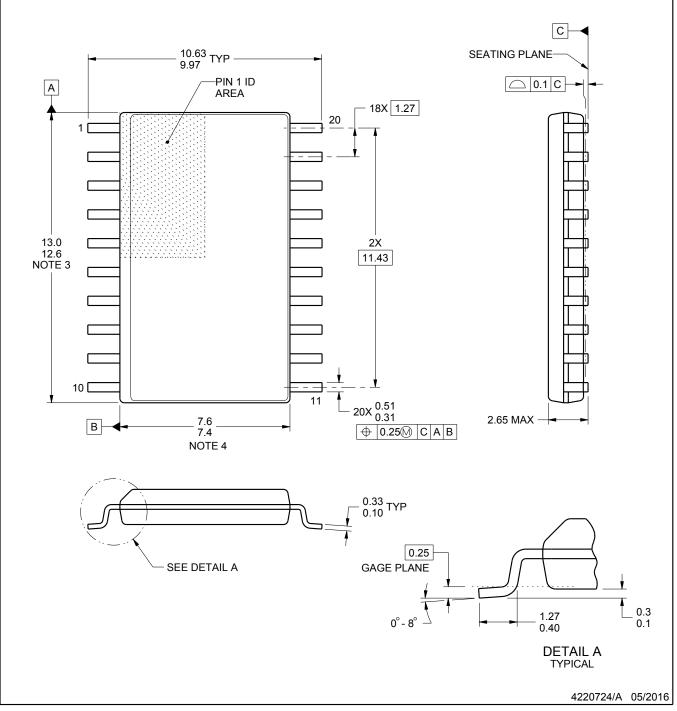

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

|             | SOIC (20) | 12.60 mm × 10.00 mm |

| LMF100      | PDIP (20) | 24.33 mm × 6.35 mm  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

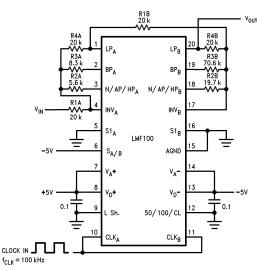

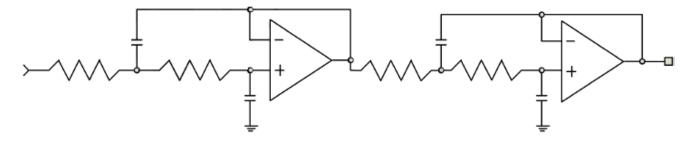

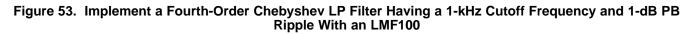

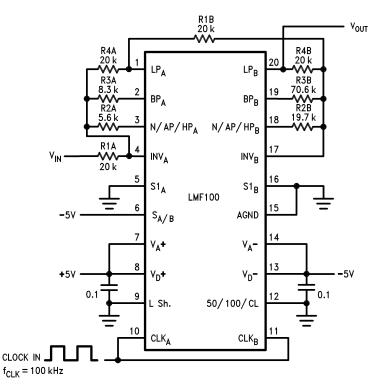

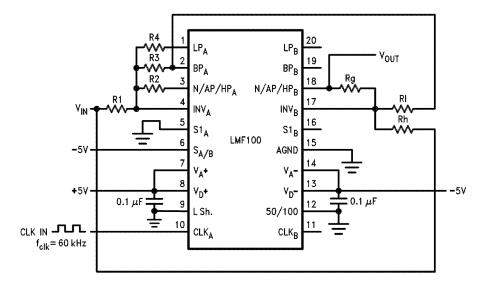

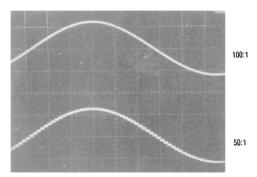

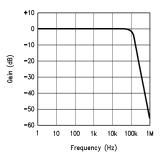

## Fourth-Order 100-kHz Butterworth Lowpass Filter

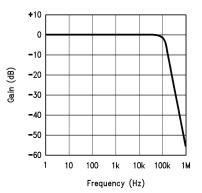

#### Transfer Curve of Butterworth LP Filter Roll-Off Magnitude vs Frequency

Functional Block Diagram ..... 16

Device Support ..... 33

Mechanical, Packaging, and Orderable

Application and Implementation ...... 24 11 Layout...... 32 11.1 Layout Guidelines ...... 32 12 Device and Documentation Support ...... 33

www.ti.com

# Table of Contents

8.1

8.2

8.3

12.1

12.2

12.3

13

9

| 1 | Fea  | tures 1                                                                              |

|---|------|--------------------------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                                          |

| 3 | Des  | cription1                                                                            |

| 4 | Rev  | ision History 2                                                                      |

| 5 | Pin  | Configuration and Functions 3                                                        |

| 6 | Spe  | cifications 4                                                                        |

|   | 6.1  | Absolute Maximum Ratings 4                                                           |

|   | 6.2  | ESD Ratings 4                                                                        |

|   | 6.3  | Recommended Operating Conditions 4                                                   |

|   | 6.4  | Thermal Information 5                                                                |

|   | 6.5  | Electrical Characteristics for V <sup>+</sup> = +5 V and V <sup>-</sup> = -5 V       |

|   | 6.6  | Electrical Characteristics for V <sup>+</sup> = +2.5 V and V <sup>-</sup> = $-2.5$ V |

|   | 6.7  | Logic Input Characteristics 8                                                        |

|   | 6.8  | Typical Characteristics 10                                                           |

| 7 | Para | ameter Measurement Information 14                                                    |

|   | 7.1  | Definition of Terms Graphics 14                                                      |

| 8 | Deta | ailed Description 16                                                                 |

# 4 Revision History

## Changes from Revision A (July 1999) to Revision B

Page

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. .....1

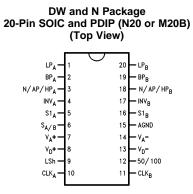

# 5 Pin Configuration and Functions

#### **Pin Functions**

|                                                            | PIN               | 1/0   | DECODIDION                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|------------------------------------------------------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| NAME                                                       | NO.               | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| LP                                                         | 1                 |       |                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| LF                                                         | 20                |       |                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| BP                                                         | 2                 | 1/0   | The second order lowpass, bandpass and notch, allpass and highpass outputs. These outputs can typically swing to within 1 V of each supply when driving a 5-k $\Omega$ load. For optimum performance, capacitive loading on these outputs                                                                                                   |  |  |  |  |  |  |  |

| DF                                                         | 19                | 1/0   | should be minimized. For signal frequencies above 15 kHz, the capacitance loading should be kept below 30 pF.                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| N/AP/HP                                                    | 3                 |       |                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| N/AL/III                                                   | 18                |       |                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| INV                                                        | 4                 |       | The inverting input of the summing op-amp of each filter. These are high impedance inputs. The noninverting input is                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| IINV                                                       | 17                | 1     | internally tied to AGND so the opamp can be used only as an inverting amplifier.                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| S1                                                         | 5                 |       | S1 is a signal input pin used in modes 1b, 4, and 5. The input impedance is 1/f <sub>CLK</sub> x 1 pF. The pin should be driven with                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 51                                                         | 16                | 1     | a source impedance of less than 1 k $\Omega$ . If S1 is not driven with a signal it should be tied to AGND (mid-supply).                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| S <sub>A/B</sub>                                           | 6                 | I     | This pin activates a switch that connects one of the inputs of each filter's second summer either to AGND ( $S_{A/B}$ tied to $V^-$ ) or to the lowpass (LP) output ( $S_{A/B}$ tied to $V^+$ ). This offers the flexibility needed for configuring the filter in its various modes of operation.                                           |  |  |  |  |  |  |  |

| V <sub>A</sub> +                                           | 7 <sup>(1)</sup>  | I     | This is both the analog and digital positive supply.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| V <sub>D</sub> <sup>+</sup>                                | 8(1)              | I     | Analog and digital negative supplies. $V_A^-$ and $V_D^-$ should be derived from the same source. They have been brought out separately so they can be bypassed by separate capacitors, if desired. They can also be tied together externally and bypassed with a single capacitor.                                                         |  |  |  |  |  |  |  |

| V <sub>A</sub> <sup>-</sup><br>V <sub>D</sub> <sup>-</sup> | 14<br>13          | - 1   | Analog and digital negative supplies. $V_A^-$ and $V_D^-$ should be derived from the same source. They have been brought out separately so they can be bypassed by separate capacitors, if desired. They can also be tied together externally and bypassed with a single capacitor.                                                         |  |  |  |  |  |  |  |

|                                                            |                   |       | Level shift pin. This is used to accommodate various clock levels with dual or single supply operation. With dual ±5-V supplies and CMOS (±5 V) or TTL (0 V–5 V) clock levels, LSh should be tied to system ground.                                                                                                                         |  |  |  |  |  |  |  |

| LSh                                                        | 9                 | I     | For 0-V to 10-V single-supply operation the AGND pin should be biased at +5 V and the LSh pin should be tied to the system ground for TTL clock levels. LSh should be biased at +5 V for $\pm$ 5-V CMOS clock levels.                                                                                                                       |  |  |  |  |  |  |  |

|                                                            |                   |       | The LSh pin is tied to system ground for $\pm 2.5V$ operation. For single 5V operation the LSh and $V_D^+$ pins are tied to system ground for TTL clock levels.                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                                            | 10                |       | Clock inputs for the two switched capacitor filter sections. Unipolar or bipolar clock levels may be applied to the CLK                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| CLK                                                        | 11                | I     | inputs according to the programming voltage applied to the LSh pin. The duty cycle of the clock should be close to 50%, especially when clock frequencies above 200 kHz are used. This allows the maximum time for the internal opamps to settle, which yields optimum filter performance.                                                  |  |  |  |  |  |  |  |

| 50/100                                                     | 12 <sup>(1)</sup> | I     | By tying this pin to V+ a 50:1 clock to filter center frequency ratio is obtained. Tying this pin at mid-supply (i.e., system ground with dual supplies) or to V <sup>-</sup> allows the filter to operate at a 100:1 clock to center frequency ratio.                                                                                      |  |  |  |  |  |  |  |

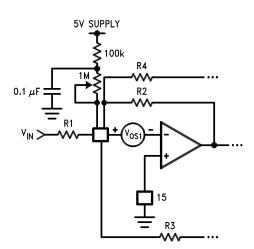

| AGND                                                       | 15                | I     | This is the analog ground pin. This pin should be connected to the system ground for dual supply operation or biased to mid-supply for single-supply operation. For a further discussion of mid-supply biasing techniques see the Applications Information (Section 3.2). For optimum filter performance a "clean" ground must be provided. |  |  |  |  |  |  |  |

(1) This device is pin-for-pin compatible with the MF10 except for the following changes:

(a) Unlike the MF10, the LMF100 has a single positive supply pin ( $V_A^+$ ).

(b) On the LMF100  $V_D^+$  is a control pin and is not the digital positive supply as on the MF10. (c) Unlike the MF10, the LMF100 does not support the current limiting mode. When the 50/100 pin is tied to V<sup>-</sup> the LMF100 will remain in the 100:1 mode.

www.ti.com

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                   |                                                           |                   | MIN | MAX | UNIT |  |

|---------------------------------------------------|-----------------------------------------------------------|-------------------|-----|-----|------|--|

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) |                                                           |                   |     | 16  | V    |  |

| Valtage at any nin                                | altage at any pin                                         |                   |     |     |      |  |

| Voltage at any pin                                | onage at any pin                                          |                   |     |     |      |  |

| Input current at any pin <sup>(2)</sup>           |                                                           |                   |     | 5   | mA   |  |

| Package input current <sup>(2)</sup>              |                                                           |                   |     | 20  | mA   |  |

| Power dissipation <sup>(3)</sup>                  |                                                           |                   |     | 500 | mW   |  |

|                                                   | N Package: 10 sec.                                        |                   |     | 250 |      |  |

| Soldering information <sup>(4)</sup>              | Soldering information <sup>(4)</sup> Vapor Phase (60 sec) |                   |     |     | °C   |  |

|                                                   | SOIC Package                                              | Infrared (15 sec) |     | 220 |      |  |

| Storage temperature, T <sub>stg</sub>             |                                                           |                   |     | 150 | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supply rails (V<sub>IN</sub> < V<sup>−</sup> or the absolute value of current at that pin should be limited to 5 mA or less. The sum of the currents at all pins that are driven beyond the power supply voltages should not exceed 20 mA.V<sub>IN</sub><sup>+</sup>)

- (3) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, R<sub>eJA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/R<sub>eJA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower. For this device, T<sub>JMAX</sub> = 125°C, and the typical junction-to-ambient thermal resistance of the LMF100CIN when board mounted is 55°C/W. For the LMF100CIWM this number is 66°C/W.

- (4) See AN-450Surface Mounting Methods and Their Effect on Product Reliability(Appendix D) for other methods of soldering surface mount devices.

## 6.2 ESD Ratings

|                    |                         |                                                                      | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)(2)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) A military RETS specification is available upon request.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |            | MIN  | NOM MAX                              | UNIT |

|-----------------------|------------|------|--------------------------------------|------|

| Temperature LMF100CCN |            | 0    | 70                                   | °C   |

| remperature           | LMF100CIWM | -40  | 85                                   |      |

| Supply voltage        |            | 4 ≤\ | / <sup>+</sup> – V <sup>−</sup> ≤ 15 | V    |

# 6.4 Thermal Information

|                       |                                              | LMF       | 100      |      |

|-----------------------|----------------------------------------------|-----------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DW (SOIC) | N (PDIP) | UNIT |

|                       |                                              | 20 PINS   | 20 PINS  |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 63.8      | 49.5     | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 27.2      | 41.1     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 31.8      | 30.4     | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 5.7       | 18.3     | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 31.3      | 30.3     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -         | —        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics for V<sup>+</sup> = +5 V and V<sup>-</sup> = -5 V

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100 \text{ k}$ ,  $R_2 = 10 \text{ k}$ ),  $V^+ = +5 \text{ V}$  and  $V^- = -5 \text{ V}$  unless otherwise specified. All limits are  $T_A = T_J = 25^{\circ}C$  unless otherwise specified.

| PARAMETER           |                                  |                                                         | TEATO                          |                                      | LMF | 100CCN |             | LM  | F100CIWN | 1       | UNIT |

|---------------------|----------------------------------|---------------------------------------------------------|--------------------------------|--------------------------------------|-----|--------|-------------|-----|----------|---------|------|

|                     | PARAMETER                        |                                                         | TESTC                          | ONDITIONS                            | MIN | TYP    | MAX         | MIN | TYP      | MAX     | UNIT |

|                     |                                  |                                                         |                                |                                      |     | 9      |             |     | 9        |         |      |

|                     |                                  | f <sub>CLK</sub> = 250 kHz,                             | Tested                         |                                      |     |        | 13          |     |          |         |      |

| l <sub>s</sub>      | Maximum supply current           | No Input Signal                                         | Limit <sup>(1)</sup>           | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        |             |     |          | 13      | mA   |

|                     |                                  |                                                         | Design<br>Limit <sup>(2)</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        | 13          |     |          |         |      |

| f <sub>0</sub>      | Center frequency                 |                                                         |                                |                                      | 0.1 |        | 10000<br>0  | 0.1 |          | 100000  | Hz   |

| f <sub>CLK</sub>    | Clock frequency                  |                                                         |                                |                                      | 5   |        | 35000<br>00 | 5   |          | 3500000 | Hz   |

|                     |                                  |                                                         |                                |                                      |     | ±0.2%  |             |     | ±0.2%    |         |      |

|                     | Clock to center frequency ratio  |                                                         | Tested                         |                                      |     |        | ±0.8%       |     |          |         |      |

| f <sub>CLK</sub> /f | deviation                        | $V_{Pin12} = 5 V \text{ or } 0$<br>V, $f_{CLK} = 1 MHz$ | Limit <sup>(1)</sup>           | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        |             |     |          | ±0.8%   |      |

|                     |                                  |                                                         | Design<br>Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        | ±0.8%       |     |          |         |      |

|                     |                                  |                                                         |                                |                                      |     | ±0.5%  |             |     | ±0.5%    |         |      |

| ΔQ                  |                                  | Q = 10, Mode 1,<br>V <sub>Pin12</sub> = 5 V or 0        | Tested                         |                                      |     |        | ±5%         |     |          |         |      |

| Q                   | Q Error (MAX) <sup>(3)</sup>     | ν,                                                      | Limit <sup>(1)</sup>           | $\rm T_{MIN}$ to $\rm T_{MAX}$       |     |        |             |     | ±6%      |         |      |

| Q                   |                                  | f <sub>CLK</sub> = 1 MHz                                | Design<br>Limit <sup>(2)</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        | ±6%         |     |          |         |      |

|                     |                                  |                                                         |                                |                                      |     | 0      |             |     | 0        |         |      |

|                     |                                  |                                                         | Tested                         |                                      |     |        | ±0.4        |     |          |         |      |

| H <sub>OBP</sub>    | Bandpass gain at $f_0$           | $f_{CLK} = 1 MHz$                                       | Limit <sup>(1)</sup>           | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        |             |     |          | ±0.4    | dB   |

|                     |                                  |                                                         | Design<br>Limit <sup>(2)</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        | ±0.4        |     |          |         |      |

|                     |                                  |                                                         |                                |                                      |     | 0      |             |     | 0        |         |      |

|                     |                                  | $R_1 = R_2 = 10 \text{ k},$                             | Tested                         |                                      |     |        | ±0.2        |     |          |         |      |

| H <sub>OLP</sub>    | DC Lowpass gain                  | $f_{CLK} = 250 \text{ kHz}$                             | Limit <sup>(1)</sup>           | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        |             |     |          | ±0.2    | dB   |

|                     |                                  |                                                         | Design<br>Limit <sup>(2)</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |        | ±0.2        |     |          |         |      |

|                     |                                  |                                                         |                                |                                      |     | ±5     |             |     | ±5       |         |      |

|                     |                                  |                                                         | Tested                         |                                      |     |        | ±15         |     |          |         |      |

| V <sub>OS1</sub>    | DC Offset voltage <sup>(4)</sup> | $f_{CLK} = 250 \text{ kHz}$                             | Limit <sup>(1)</sup>           | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        |             |     |          | ±15     | mV   |

|                     |                                  |                                                         | Design<br>Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        | ±15         |     |          |         |      |

Tested limits are specified to Texas Instruments AOQL (Average Outgoing Quality Level). (1)

- (2)

- Design limits are specified to Texas Instruments AOQL (Average Outgoing Quality Level) but are not 100% tested. The accuracy of the Q value is a function of the center frequency (f<sub>0</sub>). This is illustrated in the curves under the heading *Typical* (3)Characteristics.

- Vos1, Vos2, and Vos3 refer to the internal offsets as discussed in Application Information. (4)

SNOSBG9B-JULY 1999-REVISED JUNE 2015

www.ti.com

# Electrical Characteristics for $V^+ = +5 V$ and $V^- = -5 V$ (continued)

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100 \text{ k}$ ,  $R_2 = 10 \text{ k}$ ),  $V^+ = +5 \text{ V}$  and  $V^- = -5 \text{ V}$  unless otherwise specified. All limits are  $T_A = T_J = 25^{\circ}$ C unless otherwise specified.

| PARAMETER              |                                                   |               |                                       | TEST                              | NUDITIONS                                                   |                                      | LMF1 | 00CCN                                                                                                  |      | LMF  | 100CIWM |                            |      |

|------------------------|---------------------------------------------------|---------------|---------------------------------------|-----------------------------------|-------------------------------------------------------------|--------------------------------------|------|--------------------------------------------------------------------------------------------------------|------|------|---------|----------------------------|------|

|                        |                                                   |               |                                       | TEST CC                           | ONDITIONS                                                   |                                      | MIN  | ТҮР                                                                                                    | MAX  | MIN  | TYP     | MAX                        | UNIT |

|                        |                                                   |               |                                       |                                   |                                                             |                                      |      | ±30                                                                                                    |      |      | ±30     |                            |      |

|                        |                                                   |               |                                       | o )#                              | Tested Limit <sup>(1)</sup>                                 |                                      |      |                                                                                                        | ±80  |      |         |                            |      |

|                        |                                                   |               |                                       | $S_{A/B} = V^+$                   | S <sub>A/B</sub> = V <sup>+</sup> Tested Limit <sup>+</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |      |                                                                                                        |      |      |         | ±80                        | mV   |

| V <sub>OS2</sub> DC C  | Offset voltage <sup>(4)</sup>                     |               | f <sub>CLK</sub> = 250 kHz            |                                   | Design Limit <sup>(2)</sup>                                 | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |      |                                                                                                        | ±80  |      |         |                            |      |

| V <sub>OS2</sub> DCC   | Onset voltage                                     |               | 1 <sub>CLK</sub> – 230 KHZ            |                                   |                                                             |                                      |      | ±15                                                                                                    |      |      | ±15     | P         MAX           30 |      |

|                        |                                                   |               |                                       | S <sub>A/B</sub> = V <sup>-</sup> | Tested Limit <sup>(1)</sup>                                 |                                      |      |                                                                                                        | ±70  |      |         |                            | mV   |

|                        |                                                   |               |                                       | S <sub>A/B</sub> = v              |                                                             | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |      | ±15       ±70       ±70       ±15       ±40       ±40       ±60       -60       40       320       300 |      |      | ±70     | iiiv                       |      |

|                        |                                                   |               |                                       | Design Limit <sup>(2)</sup>       | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                        |                                      |      | ±70                                                                                                    |      |      |         |                            |      |

|                        |                                                   |               |                                       |                                   | 1                                                           |                                      |      | ±15                                                                                                    |      |      | ±15     |                            |      |

|                        | / <sub>OS3</sub> DC Offset voltage <sup>(4)</sup> |               |                                       | Tested                            |                                                             |                                      |      |                                                                                                        | ±40  |      |         |                            |      |

| V <sub>OS3</sub> DC C  |                                                   |               | $f_{CLK} = 250 \text{ kHz}$           | Limit <sup>(1)</sup>              | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                        |                                      |      |                                                                                                        |      |      |         | ±60                        | mV   |

|                        |                                                   |               | Design<br>Limit <sup>(2)</sup>        |                                   | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                        |                                      |      |                                                                                                        | ±60  |      |         |                            |      |

| Cros                   | sstalk <sup>(5)</sup>                             |               | A Side to B Side or                   | B Side to A                       | A Side                                                      |                                      |      | -60                                                                                                    |      |      | -60     |                            | dB   |

|                        |                                                   |               | f <sub>CLK</sub> = 250 kHz            | N                                 |                                                             |                                      |      | 40                                                                                                     |      |      | 40      |                            |      |

| Outp                   | put noise <sup>(6)</sup>                          |               | 20 kHz Bandwidth                      | BP                                | 3P                                                          |                                      |      | 320                                                                                                    |      |      | 320     |                            | μV   |

|                        |                                                   |               | 100:1 Mode                            | LP                                |                                                             |                                      |      | 300                                                                                                    |      |      | 300     |                            |      |

| Cloc                   | ck feedthrough(7)                                 |               | f <sub>CLK</sub> = 250 kHz 100:       |                                   | 6                                                           |                                      |      | 6                                                                                                      |      | mV   |         |                            |      |

|                        |                                                   |               |                                       |                                   |                                                             |                                      |      | 4                                                                                                      |      |      |         |                            |      |

|                        |                                                   |               |                                       |                                   | 1                                                           |                                      |      | -4.7                                                                                                   |      |      | -4.7    |                            |      |

|                        |                                                   |               | R <sub>L</sub> = 5 k<br>(All Outputs) | Tested<br>Limit <sup>(1)</sup>    |                                                             |                                      |      |                                                                                                        | ±3.8 |      |         |                            |      |

| V <sub>OUT</sub> Minir | imum output voltage                               | swing         | (All Outputs)                         |                                   | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                        |                                      |      |                                                                                                        |      |      |         | ±3.7                       | V    |

|                        |                                                   |               |                                       | Design<br>Limit <sup>(2)</sup>    | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                        |                                      |      |                                                                                                        | ±3.7 |      |         |                            |      |

|                        |                                                   |               | R <sub>L</sub> = 3.5 k                |                                   |                                                             |                                      |      | 3.9                                                                                                    |      |      | 3.9     |                            |      |

|                        |                                                   | (All Outputs) |                                       |                                   |                                                             |                                      | -4.6 |                                                                                                        |      | -4.6 |         |                            |      |

| GB Oper<br>W prod      | erational amplifier ga<br>duct                    | IIN BVV       |                                       |                                   |                                                             |                                      |      | 5                                                                                                      |      |      | 5       |                            | MHz  |

| SR Oper                | erational amplifier sle                           | ew rate       |                                       |                                   |                                                             |                                      |      | 20                                                                                                     |      |      | 20      |                            | V/µs |

| I <sub>sc</sub> Maxi   | kimum output,                                     | Source        | All Outputs                           |                                   |                                                             |                                      |      | 12                                                                                                     |      |      | 12      |                            | mA   |

| 'sc Shor               | ort circuit current <sup>(8)</sup>                | Sink          | All Outputs                           |                                   |                                                             |                                      |      | 45                                                                                                     |      |      | 45      |                            | mA   |

|                        | ut current on Pins: 4,                            | , 5, 6, 9,    | Tested Limit <sup>(1)</sup>           |                                   | 1                                                           |                                      |      |                                                                                                        | 10   |      |         |                            | μA   |

| 10, 1                  | 11, 12, 16, 17                                    |               | Design Limit <sup>(2)</sup>           |                                   | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                        |                                      |      |                                                                                                        |      |      |         | 10                         | н, , |

(5) Crosstalk between the internal filter sections is measured by applying a 1 V<sub>RMS</sub> 10-kHz signal to one bandpass filter section input and grounding the input of the other bandpass filter section. The crosstalk is the ratio between the output of the grounded filter section and the 1 V<sub>RMS</sub> input signal of the other section.

(6) In 50:1 mode the output noise is 3 dB higher.

(7) In 50:1 mode the clock feed through is 6 dB higher.

(8) The short circuit source current is measured by forcing the output that is being tested to its maximum positive voltage swing and then shorting that output to the negative supply. The short circuit sink current is measured by forcing the output that is being tested to its maximum negative voltage swing and then shorting that output to the positive supply. These are the worst case conditions.

# 6.6 Electrical Characteristics for V<sup>+</sup> = +2.5 V and V<sup>-</sup> = -2.5 V

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100 \text{ k}$ ,  $R_2 = 10 \text{ k}$ ), V<sup>+</sup> = +2.50 V and V<sup>-</sup> = -2.50 V unless otherwise specified. All limits are  $T_A = T_J = 25^{\circ}$ C unless otherwise specified.

|                | PARAMETER              |                                                | TEST                           | ONDITIONS                            | LMF1 | 00CCN |       | LMF | 100CIWM |       | UNIT |

|----------------|------------------------|------------------------------------------------|--------------------------------|--------------------------------------|------|-------|-------|-----|---------|-------|------|

|                | PARAMETER              |                                                |                                |                                      | MIN  | TYP   | MAX   | MIN | TYP     | MAX   | UNIT |

|                |                        |                                                |                                |                                      |      | 8     |       |     | 8       |       |      |

|                |                        | 6 050 111-                                     | Tested                         |                                      |      |       | 12    |     |         | 12    |      |

| I <sub>s</sub> | Maximum supply current | f <sub>CLK</sub> = 250 kHz,<br>No Input Signal | Limit <sup>(1)</sup>           | T <sub>MIN</sub> to T <sub>MAX</sub> |      |       |       |     |         |       | mA   |

|                |                        |                                                | Design<br>Limit <sup>(2)</sup> |                                      |      | 12    |       |     |         |       |      |

| $\mathbf{f}_0$ | Center frequency       |                                                |                                |                                      | 0.1  |       | 50000 | 0.1 |         | 50000 | Hz   |

(1) Tested limits are specified to Texas Instruments AOQL (Average Outgoing Quality Level).

(2) Design limits are specified to Texas Instruments AOQL (Average Outgoing Quality Level) but are not 100% tested.

# Electrical Characteristics for $V^+ = +2.5 V$ and $V^- = -2.5 V$ (continued)

The following specifications apply for Mode 1, Q = 10 ( $R_1 = R_3 = 100 \text{ k}$ ,  $R_2 = 10 \text{ k}$ ),  $V^+ = +2.50 \text{ V}$  and  $V^- = -2.50 \text{ V}$  unless otherwise specified. All limits are  $T_A = T_J = 25^{\circ}C$  unless otherwise specified.

| PARAMETER           |                                  |                                                              | TEST                                                      | ONDITIONS                              |                                      | LMF | 100CCN |             | LM  | F100CIWI | N       | UNIT |

|---------------------|----------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------|--------------------------------------|-----|--------|-------------|-----|----------|---------|------|

|                     |                                  |                                                              | 1231 60                                                   | JNDITIONS                              |                                      | MIN | TYP    | MAX         | MIN | TYP      | MAX     | UNIT |

| f <sub>CLK</sub>    | Clock frequency                  |                                                              |                                                           |                                        |                                      | 5   |        | 15000<br>00 | 5   |          | 1500000 | Hz   |

|                     |                                  |                                                              |                                                           |                                        |                                      |     | ±0.2%  |             |     | ±0.2%    |         |      |

| f <sub>CLK</sub> /f | Clock to center frequency ratio  | V <sub>Pin12</sub> = 5 V or 0<br>V, f <sub>CLK</sub> = 1 MHz | Tested<br>Limit <sup>(1)</sup>                            | $T_{\text{MIN}}$ to $T_{\text{MAX}}$   |                                      |     |        | ±1%         |     |          | ±1%     |      |

| 0                   | deviation                        | V, I <sub>CLK</sub> = I IVIHZ                                | Design<br>Limit <sup>(2)</sup>                            |                                        |                                      |     |        | ±1%         |     |          |         |      |

|                     |                                  |                                                              |                                                           |                                        |                                      |     | ±0.5%  |             |     | ±0.5%    |         |      |

| ΔQ                  |                                  | Q = 10, Mode 1,                                              | Tested                                                    |                                        |                                      |     |        | ±5%         |     |          |         |      |

|                     | Q Error (MAX) (3)                | V <sub>Pin12</sub> = 5 V or 0<br>V,                          | Limit <sup>(1)</sup>                                      | T <sub>MIN</sub> to T <sub>MAX</sub>   |                                      |     |        |             |     |          | ±8%     |      |

| Q                   |                                  | $f_{CLK} = 1 \text{ MHz}$                                    | Design<br>Limit <sup>(2)</sup>                            | $\rm T_{MIN}$ to $\rm T_{MAX}$         |                                      |     |        | ±8%         |     |          |         |      |

|                     |                                  |                                                              |                                                           |                                        |                                      |     | 0      |             |     | 0        |         |      |

|                     |                                  |                                                              | Tested                                                    |                                        |                                      |     |        | ±0.4        |     |          |         |      |

| H <sub>OBP</sub>    | Bandpass gain at $f_0$           | $f_{CLK} = 1 MHz$                                            | Limit <sup>(1)</sup>                                      | $T_{\text{MIN}}$ to $T_{\text{MAX}}$   |                                      |     |        |             |     |          | ±0.5    | dB   |

|                     |                                  |                                                              | Design<br>Limit <sup>(2)</sup>                            | $\rm T_{MIN}$ to $\rm T_{MAX}$         |                                      |     |        | ±0.5        |     |          |         |      |

|                     |                                  |                                                              |                                                           |                                        |                                      |     | 0      |             |     | 0        |         |      |

|                     |                                  | $R_1 = R_2 = 10 \text{ k},$                                  | Tested                                                    |                                        |                                      |     |        | ±0.2        |     |          |         |      |

| H <sub>OLP</sub>    | DC Lowpass gain                  | $f_{CLK} = 250 \text{ kHz}$                                  | Limit <sup>(1)</sup>                                      | $\rm T_{\rm MIN}$ to $\rm T_{\rm MAX}$ |                                      |     |        |             |     |          | ±0.2    | dB   |

|                     |                                  |                                                              | Design<br>Limit <sup>(2)</sup>                            | $T_{\text{MIN}}$ to $T_{\text{MAX}}$   |                                      |     |        | ±0.2        |     |          |         |      |

|                     |                                  |                                                              |                                                           | 1                                      |                                      |     | ±5     |             |     | ±5       |         | 4    |

| .,                  |                                  | (                                                            | Tested                                                    |                                        |                                      |     |        | ±15         |     |          | ±15     |      |

| V <sub>OS1</sub>    | DC Offset voltage <sup>(4)</sup> | f <sub>CLK</sub> = 250 kHz                                   | Limit <sup>(1)</sup> T <sub>MIN</sub> to T <sub>MAX</sub> |                                        |                                      |     |        |             |     |          | mV      |      |

|                     |                                  |                                                              | Design<br>Limit <sup>(2)</sup>                            | $T_{\text{MIN}}$ to $T_{\text{MAX}}$   |                                      |     |        | ±15         |     |          |         |      |

|                     |                                  |                                                              |                                                           |                                        |                                      | ±20 |        |             |     | ±20      |         |      |

|                     |                                  |                                                              | $S_{A/B} = V^+$                                           | Tested Limit <sup>(1)</sup>            |                                      |     |        | ±60         |     |          |         | mV   |

|                     |                                  |                                                              | - A/B                                                     |                                        | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        |             |     |          | ±60     | ł    |

| V <sub>OS2</sub>    | DC Offset voltage <sup>(4)</sup> | f <sub>CLK</sub> = 250 kHz                                   |                                                           | Design Limit <sup>(2)</sup>            | T <sub>MIN</sub> to T <sub>MAX</sub> | 10  |        | ±60         | 10  |          |         |      |

|                     |                                  |                                                              |                                                           |                                        |                                      | ±10 |        | ±50         | ±10 |          | mV      | ł    |

|                     |                                  |                                                              | $S_{A/B} = V^-$                                           | Tested Limit <sup>(1)</sup>            | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        | ±30         |     |          | ±60     |      |

|                     |                                  |                                                              |                                                           | Design Limit <sup>(2)</sup>            | T <sub>MIN</sub> to T <sub>MAX</sub> |     |        | ±60         |     |          | 100     |      |

|                     |                                  |                                                              |                                                           | Doolgri Linik                          | MIN CO MAA                           |     | ±10    | 200         |     | ±10      |         |      |

|                     |                                  |                                                              | Tested                                                    |                                        |                                      |     |        | ±25         |     |          |         |      |

| V <sub>OS3</sub>    | DC Offset voltage <sup>(4)</sup> | $f_{CLK} = 250 \text{ kHz}$                                  | Limit <sup>(1)</sup>                                      | T <sub>MIN</sub> to T <sub>MAX</sub>   |                                      |     |        |             |     |          | ±30     | mV   |

|                     |                                  |                                                              | Design<br>Limit <sup>(2)</sup>                            | $T_{\text{MIN}}$ to $T_{\text{MAX}}$   |                                      |     |        | ±30         |     |          |         |      |

|                     | Crosstalk <sup>(5)</sup>         | A Side to B Side or                                          | B Side to /                                               | A Side                                 |                                      |     | -65    |             |     | -65      |         | dB   |

|                     |                                  | f <sub>CLK</sub> = 250 kHz                                   | N                                                         |                                        |                                      |     | 25     |             |     | 25       |         |      |

|                     | Output noise <sup>(6)</sup>      | 20 kHz Bandwidth                                             | BP                                                        |                                        |                                      |     | 250    |             |     | 250      |         | μV   |

|                     |                                  | 100:1 Mode                                                   | LP                                                        |                                        |                                      |     | 220    |             |     | 220      |         |      |

|                     | Clock feedthrough <sup>(7)</sup> | f <sub>CLK</sub> = 250 kHz 100                               | :1 Mode                                                   |                                        |                                      |     | 2      |             |     | 2        |         | mV   |

The accuracy of the Q value is a function of the center frequency ( $f_0$ ). This is illustrated in the curves under the heading *Typical* (3) Characteristics

- (4)

- V<sub>os1</sub>, V<sub>os2</sub>, and V<sub>os3</sub> refer to the internal offsets as discussed in the *Application Information*. Crosstalk between the internal filter sections is measured by applying a 1 V<sub>RMS</sub> 10-kHz signal to one bandpass filter section input and (5) grounding the input of the other bandpass filter section. The crosstalk is the ratio between the output of the grounded filter section and the 1 V<sub>RMS</sub> input signal of the other section.

- In 50:1 mode the output noise is 3 dB higher. (6)

- In 50:1 mode the clock feed through is 6 dB higher. (7)

Copyright © 1999-2015, Texas Instruments Incorporated

SNOSBG9B-JULY 1999-REVISED JUNE 2015

www.ti.com

# Electrical Characteristics for $V^+ = +2.5 V$ and $V^- = -2.5 V$ (continued)

The following specifications apply for Mode 1, Q = 10 (R<sub>1</sub> = R<sub>3</sub> = 100 k, R<sub>2</sub> = 10 k), V<sup>+</sup> = +2.50 V and V<sup>-</sup> = -2.50 V unless otherwise specified. All limits are T<sub>A</sub> = T<sub>J</sub> = 25°C unless otherwise specified.

|                  | DADAMETED                            |          |                                      | TEOTO                          |                                      | LMF | 100CCN      |      | LMF | 100CIWM     |      |      |

|------------------|--------------------------------------|----------|--------------------------------------|--------------------------------|--------------------------------------|-----|-------------|------|-----|-------------|------|------|

| PARAMETER        |                                      |          | TEST CONDITIONS                      |                                |                                      | MIN | TYP         | MAX  | MIN | TYP         | MAX  | UNIT |

|                  |                                      |          | R <sub>L</sub> = 5 k<br>All Outputs  |                                |                                      |     | 1.6<br>-2.2 |      |     | 1.6<br>-2.2 |      |      |

|                  |                                      |          |                                      | Tested                         |                                      |     |             | ±1.5 |     |             |      |      |

| V <sub>OUT</sub> | Minimum output voltag                | e swina  | $R_L = 5 k$ (All                     | Limit <sup>(1)</sup>           | T <sub>MIN</sub> to T <sub>MAX</sub> |     |             |      |     |             | ±1.4 | V    |

| •001             | VOUT Within output voltage swing     |          | Outputs)                             | Design<br>Limit <sup>(2)</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |             | ±1.4 |     |             |      |      |

|                  |                                      |          | $R_L = 3.5 \text{ k}$<br>All Outputs |                                |                                      |     | 1.5<br>-2.1 |      |     | 1.5<br>-2.1 |      | V    |

| GB<br>W          | Operational amplifier ga             | ain BW   |                                      |                                |                                      |     | 5           |      |     | 5           |      | MHz  |

| SR               | Operational amplifier sl             | lew rate |                                      |                                |                                      |     | 18          |      |     | 18          |      | V/µs |

|                  | Maximum output,                      | Source   | All Outputs                          |                                |                                      |     | 10          |      |     | 10          |      | mA   |

| sc               | Short circuit current <sup>(8)</sup> | Sink     | All Outputs                          |                                |                                      |     | 20          |      |     | 20          |      | mA   |

(8) The short circuit source current is measured by forcing the output that is being tested to its maximum positive voltage swing and then shorting that output to the negative supply. The short circuit sink current is measured by forcing the output that is being tested to its maximum negative voltage swing and then shorting that output to the positive supply. These are the worst case conditions.

# 6.7 Logic Input Characteristics

All limits apply to  $T_A = T_J = 25^{\circ}C$  unless otherwise specified.

| PARAMETER     |                 | <u> </u>                                      | LMF                         | 100CCN                               | I   | LMF100CIWM |     |     |      |     |   |

|---------------|-----------------|-----------------------------------------------|-----------------------------|--------------------------------------|-----|------------|-----|-----|------|-----|---|

| PARA          | AMETER          |                                               | MIN                         | TYP                                  | MAX | MIN        | TYP | MAX | UNIT |     |   |

|               |                 |                                               | Tested Limit <sup>(1)</sup> |                                      |     |            | 3   |     |      |     |   |

|               | MIN Logical "1" | V <sup>+</sup> = +5 V, V <sup>−</sup> = −5 V, | Tested Limit.               | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     |     |      | 3   | V |

|               |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 3   |     |      |     |   |

|               |                 |                                               | Tested Limit <sup>(1)</sup> |                                      |     |            | -3  |     |      |     |   |

|               | MAX Logical "0" | $V_{LSh} = 0 V$                               | Tested Limit                | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     |     |      | -3  | V |

| CMOS Clock    |                 |                                               | Design Limit <sup>(2)</sup> | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |            | -3  |     |      |     |   |

| Input Voltage |                 |                                               | Tested Limit <sup>(1)</sup> |                                      |     |            | 8   |     |      |     |   |

|               | MIN Logical "1" | V <sup>+</sup> = +10 V, V <sup>-</sup> = 0 V, | Lested Limit                | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     |     |      | 8   | v |

|               |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 8   |     |      |     |   |

|               |                 | V <sub>LSh</sub> = +5 V                       | Tested Limit <sup>(1)</sup> |                                      |     |            | 2   |     |      |     |   |

|               | MAX Logical "0" |                                               |                             | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     |     |      | 2   | V |

|               |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 2   |     |      |     |   |

|               | MIN Logical "1" | al "1" $V^* = +5 V, V^- = -5 V,$              | Tested Limit <sup>(1)</sup> |                                      |     |            | 2   |     |      |     |   |

|               |                 |                                               |                             | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     |     |      | 2   | V |

|               |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 2   |     |      |     |   |

|               |                 |                                               | To see al. Line (r(1)       |                                      |     | 0.8        |     |     |      |     |   |

|               | MAX Logical "0" | $V_{LSh} = 0 V$                               | Tested Limit <sup>(1)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     | 0.8 | V    |     |   |

| TTL Clock     |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> | 0.8 |            |     |     |      |     |   |

| Input Voltage |                 |                                               | Tested Limit <sup>(1)</sup> |                                      |     |            | 2   |     |      |     |   |

|               | MIN Logical "1" | V <sup>+</sup> = +10 V, V <sup>-</sup> = 0 V, | Tested Limit                | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     | 2   | V    |     |   |

|               |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 2   |     |      |     |   |

|               |                 |                                               | Tested Limit(1)             |                                      |     |            | 0.8 |     |      |     |   |

|               | MAX Logical "0" | $V_{LSh} = 0 V$                               | Tested Limit <sup>(1)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |     |     |      | 0.8 | v |

|               |                 |                                               | Design Limit <sup>(2)</sup> | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 0.8 |     |      |     |   |

(1) Tested limits are specified to Texas Instruments AOQL (Average Outgoing Quality Level).

(2) Design limits are specified to Texas Instruments AOQL (Average Outgoing Quality Level) but are not 100% tested.

# Logic Input Characteristics (continued)

All limits apply to  $T_A = T_J = 25^{\circ}C$  unless otherwise specified.

| PARAMETER                          |                 |                                                   | LMF                                  | 100CCN                               |     | LMF100CIWM |      |     |      |      |   |

|------------------------------------|-----------------|---------------------------------------------------|--------------------------------------|--------------------------------------|-----|------------|------|-----|------|------|---|

| PARA                               | AMETER          |                                                   | MIN                                  | ТҮР                                  | MAX | MIN        | TYP  | MAX | UNIT |      |   |

|                                    |                 |                                                   | Tested Limit <sup>(1)</sup>          |                                      |     |            | 1.5  |     |      |      |   |

|                                    | MIN Logical "1" | V <sup>+</sup> = +2.5 V, V <sup>−</sup> = −2.5 V, |                                      | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |      |     |      | 1.5  | V |

|                                    |                 | Design Limit <sup>(2)</sup>                       | T <sub>MIN</sub> to T <sub>MAX</sub> |                                      |     | 1.5        |      |     |      |      |   |

|                                    |                 | Tested Limit <sup>(1)</sup>                       |                                      |                                      |     | -1.5       |      |     |      |      |   |

|                                    | MAX Logical "0" | $V_{LSh} = 0 V$                                   | rested Limit''                       | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |            |      |     |      | -1.5 | V |

| CMOS Clock<br>Input Voltage<br>MIN |                 |                                                   | Design Limit <sup>(2)</sup>          | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | -1.5 |     |      |      |   |

|                                    |                 | V <sup>+</sup> = +5 V, V <sup>-</sup> = 0 V,      | Tested Limit <sup>(1)</sup>          |                                      |     | 4          |      |     |      |      |   |

|                                    | MIN Logical "1" |                                                   |                                      | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |            |      |     |      | 4    | V |

|                                    |                 |                                                   | Design Limit <sup>(2)</sup>          | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |            | 4    |     |      |      |   |

|                                    |                 |                                                   | Tested Limit <sup>(1)</sup>          |                                      |     |            | 1    |     |      |      |   |

|                                    | MAX Logical "0" | $V_{LSh}$ = +2.5 V                                |                                      | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     |            |      |     |      | 1    | V |

|                                    |                 |                                                   | Design Limit <sup>(2)</sup>          | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 1    |     |      |      |   |

|                                    |                 |                                                   | Tested Limit <sup>(1)</sup>          |                                      |     |            | 2    |     |      |      |   |

|                                    | MIN Logical "1" | V <sup>+</sup> = +5 V, V <sup>-</sup> = 0 V,      | rested Limit."                       | $T_{\text{MIN}}$ to $T_{\text{MAX}}$ |     | 2          |      |     |      | 2    | V |

| TTL Clock                          |                 |                                                   | Design Limit <sup>(2)</sup>          | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            |      |     |      |      |   |

| Input Voltage                      |                 |                                                   | Tested Limit(1)                      |                                      |     |            | 0.8  |     |      |      |   |

|                                    | MAX Logical "0" | pical "0" $V_{LSh} = 0 V, V_{D}^{+} = 0 V$        | Tested Limit <sup>(1)</sup>          | $\rm T_{MIN}$ to $\rm T_{MAX}$       |     |            |      |     |      | 0.8  | V |

|                                    |                 |                                                   | Design Limit <sup>(2)</sup>          | T <sub>MIN</sub> to T <sub>MAX</sub> |     |            | 0.8  |     |      |      |   |

www.ti.com

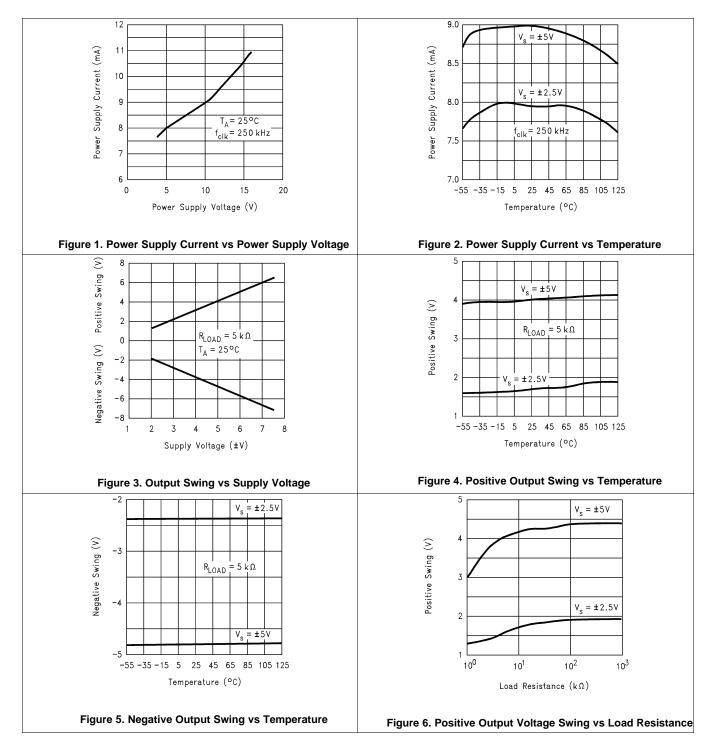

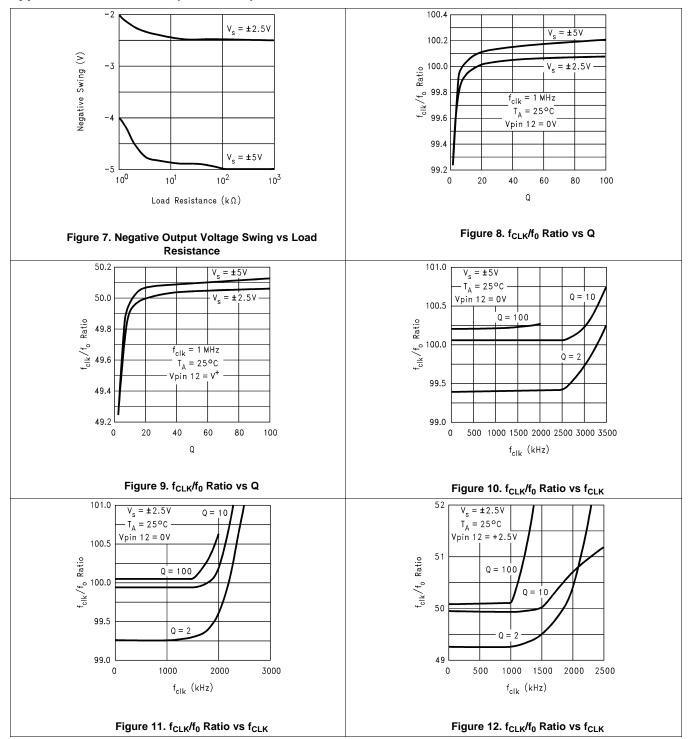

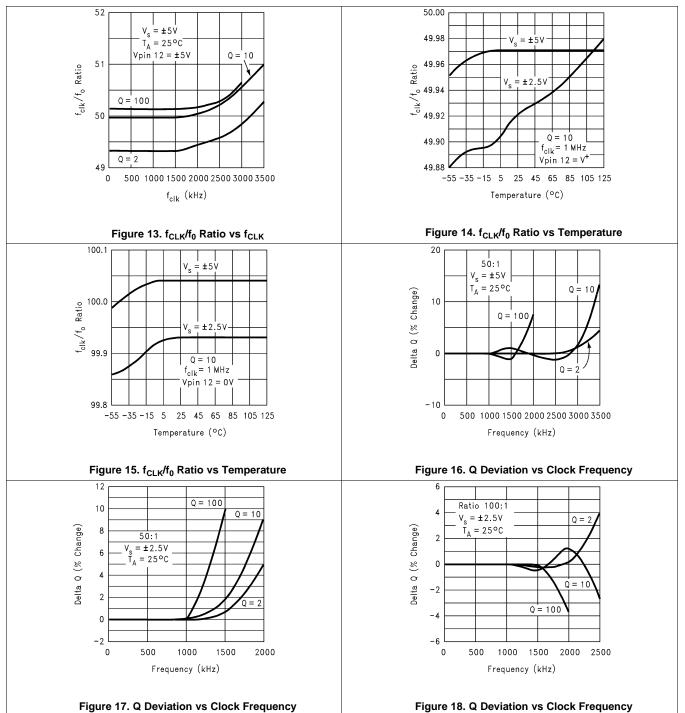

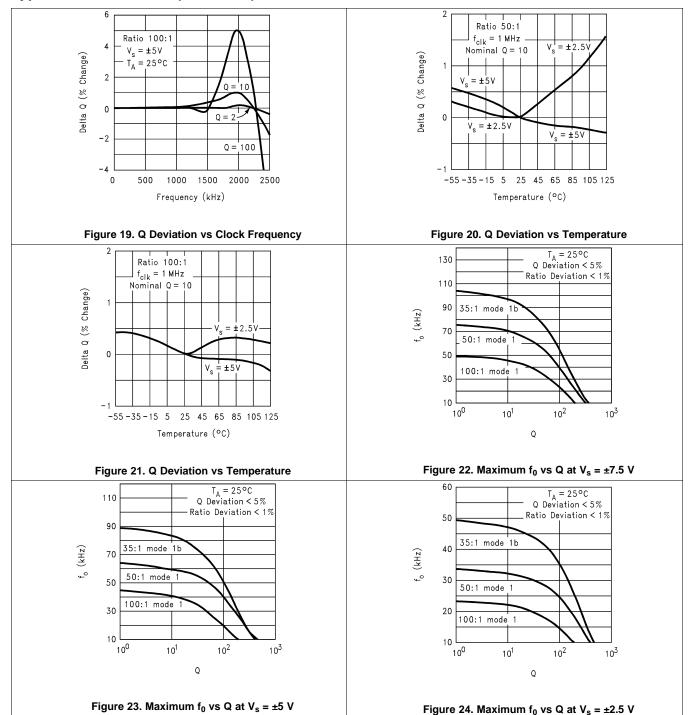

# 6.8 Typical Characteristics

## **Typical Characteristics (continued)**

www.ti.com

# **Typical Characteristics (continued)**

www.ti.com

LMF100 SNOSBG9B – JULY 1999 – REVISED JUNE 2015

## **Typical Characteristics (continued)**

Texas Instruments

www.ti.com

# 7 Parameter Measurement Information

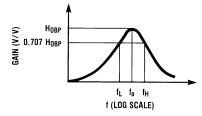

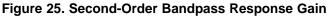

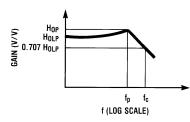

# 7.1 Definition of Terms Graphics

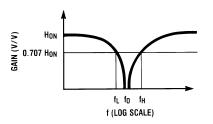

Figure 29. Second-Order Highpass Response Gain

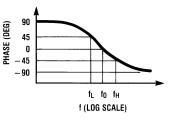

Figure 26. Second-Order Bandpass Response Phase

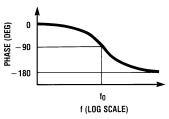

Figure 28. Second-Order Lowpass Response Phase

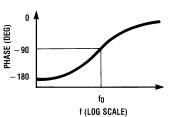

Figure 30. Second-Order Highpass Response Phase

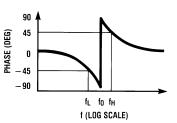

Figure 32. Second-Order Notch Response Phase

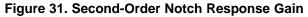

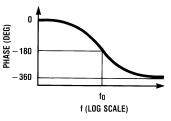

Figure 34. Second-Order Allpass Response Phase

# **Definition of Terms Graphics (continued)**

# 8 Detailed Description

## 8.1 Overview

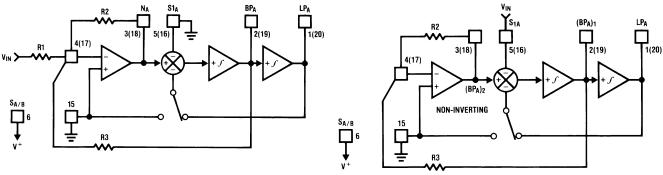

The LMF100 device contains two general-purpose, very high-performance switched capacitor filters that are costeffective and space-saving. It enables designers to implement all the classical filters up to fourth-order biquad with one chip. This switched capacitor filters can be used in a broad range of industrial and consumer application such as audio, communication, instrumentation, medical, telemetry, etc. It can be directly cascaded to implement higher order filters,

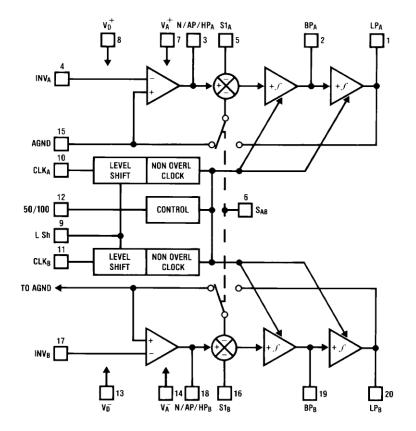

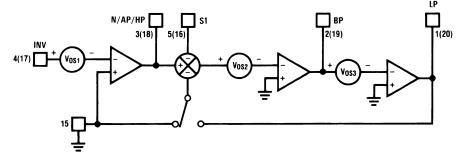

## 8.2 Functional Block Diagram

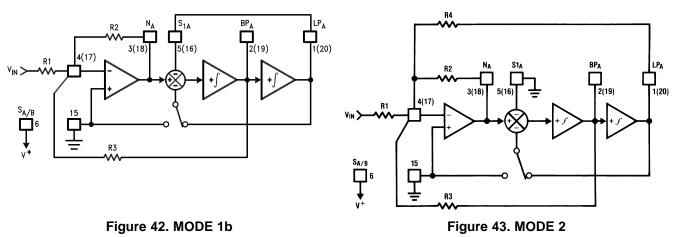

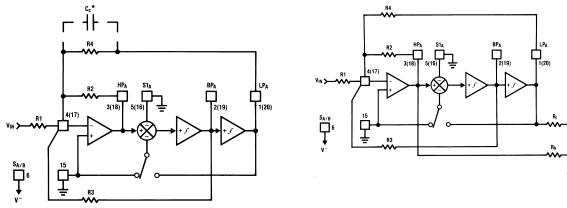

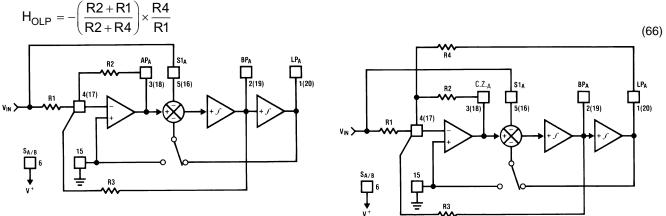

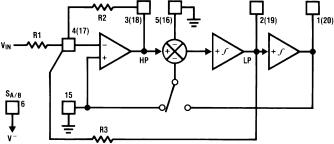

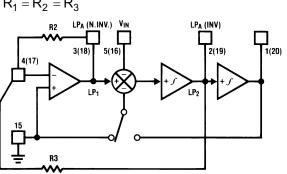

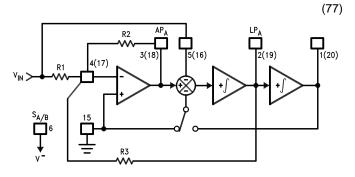

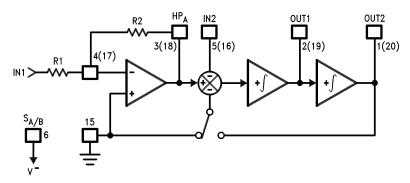

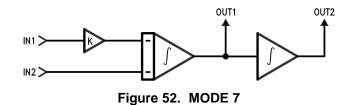

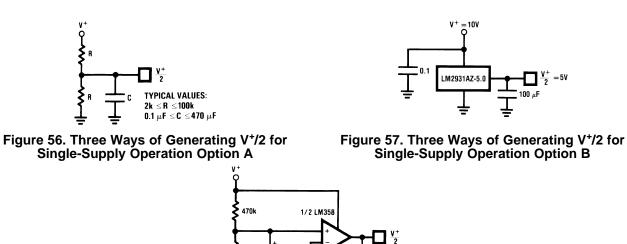

## 8.3 Feature Description