# LM5019

# 100V, 100mA Constant On-Time Synchronous Buck Regulator

# **General Description**

The LM5019 is a 100V, 100mA synchronous step-down regulator with integrated high side and low side MOSFETs. The constant-on-time (COT) control scheme employed in the LM5019 requires no loop compensation, provides excellent transient response, and enables very low step-down ratios. The on-time varies inversely with the input voltage resulting in nearly constant frequency over the input voltage range. A high voltage startup regulator provides bias power for internal operation of the IC and for integrated gate drivers.

A peak current limit circuit protects against overload conditions. The undervoltage lockout (UVLO) circuit allows the input undervoltage threshold and hysteresis to be independently programmed. Other protection features include thermal shutdown and bias supply undervoltage lockout.

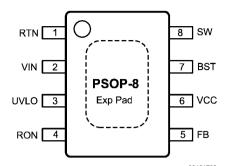

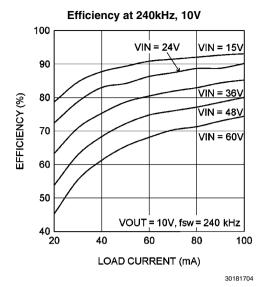

The LM5019 is available in LLP-8 and PSOP-8 plastic packages.

#### **Features**

- Wide 9V to 100V Input Range

- Integrated 100V, High and Low Side Switches

- No Schottky Required

- Constant On-Time Control

- No Loop Compensation Required

- Ultra-Fast Transient Response

- Nearly Constant Operating Frequency

- Intelligent Peak Current Limit

- Adjustable Output Voltage from 1.225V

- Precision 2% Feedback Reference

- Frequency Adjustable to 1MHz

- Adjustable Undervoltage Lockout

- Remote Shutdown

- Thermal Shutdown

# **Packages**

- LLP-8

- PSOP-8

# **Applications**

- Smart Power Meters

- Telecommunication Systems

- Automotive Electronics

- Isolated Bias Supply

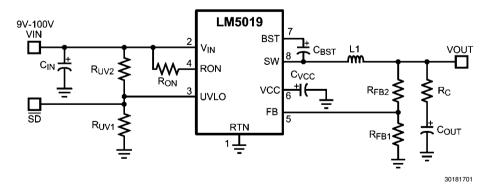

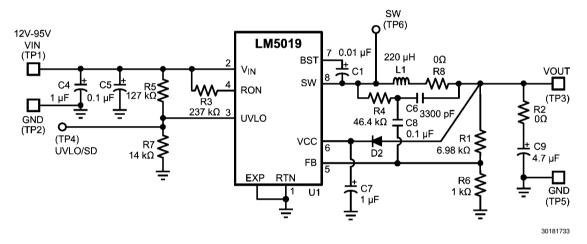

# **Typical Application**

FIGURE 1.

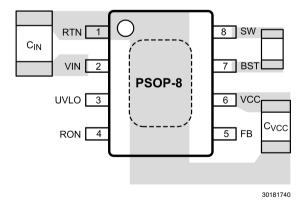

# **Connection Diagram**

Top View (Connect Exposed Pad to RTN)

Top View (Connect Exposed Pad to RTN)

# **Ordering Information**

| Order Number | Package Type | Package Drawing | Supplied As                 |

|--------------|--------------|-----------------|-----------------------------|

| LM5019MR     | PSOP-8       | MRA08A          | 1000 Units on Tape and Reel |

| LM5019SD     | LLP-8        | SDC08B          | 1000 Units on Tape and Reel |

# **Pin Descriptions**

| Pin | Name            | Description                                                                    | Application Information                                                                                                                                                                                                                                                  |

|-----|-----------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RTN             | Ground                                                                         | Ground connection of the integrated circuit.                                                                                                                                                                                                                             |

| 2   | $V_{IN}$        | Input Voltage                                                                  | Operating input range is 9V to 100V.                                                                                                                                                                                                                                     |

| 3   | UVLO            | Input Pin of Undervoltage Comparator                                           | Resistor divider from $V_{\rm IN}$ to UVLO to GND programs the undervoltage detection threshold. An internal current source is enabled when UVLO is above 1.225V to provide hysteresis. When UVLO pin is pulled below 0.66V externally, the parts goes in shutdown mode. |

| 4   | R <sub>ON</sub> | On-Time Control                                                                | A resistor between this pin and $\rm V_{IN}$ sets the switch ontime as a function of $\rm V_{IN}$ . Minimum recommended ontime is 100ns at max input voltage.                                                                                                            |

| 5   | FB              | Feedback                                                                       | This pin is connected to the inverting input of the internal regulation comparator. The regulation level is 1.225V.                                                                                                                                                      |

| 6   | V <sub>CC</sub> | Output From the Internal High Voltage Series Pass Regulator. Regulated at 7.6V | The internal $V_{CC}$ regulator provides bias supply for the gate drivers and other internal circuitry. A 1.0 $\mu$ F decoupling capacitor is recommended.                                                                                                               |

| 7   | BST             | Bootstrap Capacitor                                                            | An external capacitor is required between the BST and SW pins (0.01 $\mu$ F ceramic). The BST pin capacitor is charged by the V <sub>CC</sub> regulator through an internal diode when the SW pin is low.                                                                |

| 8   | SW              | Switching Node                                                                 | Power switching node. Connect to the output inductor and bootstrap capacitor.                                                                                                                                                                                            |

|     | EP              | Exposed Pad                                                                    | Exposed pad must be connected to RTN pin. Connect to system ground plane on application board for reduced thermal resistance.                                                                                                                                            |

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

$V_{IN}$ , UVLO to RTN -0.3V to 100V

SW to RTN -1.5V to  $V_{IN} + 0.3V$

$\begin{array}{cc} \text{BST to V}_{\text{CC}} & \text{100V} \\ \text{BST to SW} & \text{13V} \end{array}$

$R_{ON}$  to RTN -0.3V to 100V  $V_{CC}$  to RTN -0.3V to 13V

FB to RTN -0.3V to 5V

ESD Rating (Human Body Model(Note 2kV

*5*)

Lead Temperature (Note 2) 200°C

Storage Temperature Range -55°C to +150°C

# **Operating Ratings** (Note 1)

$V_{IN}$  Voltage 9V to 100V Operating Junction Temperature -40°C to +125°C

### **Electrical Characteristics**

Specifications with standard typeface are for  $T_J = 25^{\circ}$ C, and those with **boldface** type apply over full Operating Junction Temperature range.  $V_{IN} = 48V$ , unless otherwise stated. See (*Note 3*).

| Symbol                 | Parameter                                                                    | Conditions                                    | Min  | Тур  | Max  | Units |

|------------------------|------------------------------------------------------------------------------|-----------------------------------------------|------|------|------|-------|

| V <sup>CC</sup> Supply | •                                                                            |                                               |      | •    | •    | •     |

| V <sub>CC</sub> Reg    | V <sub>CC</sub> Regulator Output                                             | V <sub>IN</sub> = 48V, I <sub>CC</sub> = 20mA | 6.25 | 7.6  | 8.55 | V     |

|                        | V <sub>CC</sub> Current Limit                                                | V <sub>IN</sub> = 48V( <i>Note 4</i> )        | 26   |      |      | mA    |

|                        | V <sub>CC</sub> Undervoltage Lockout<br>Voltage (V <sub>CC</sub> Increasing) |                                               | 4.15 | 4.5  | 4.9  | V     |

|                        | V <sub>CC</sub> Undervoltage Hysteresis                                      |                                               |      | 300  |      | mV    |

|                        | V <sub>CC</sub> Drop Out Voltage                                             | $V_{IN} = 9V$ , $I_{CC} = 20mA$               |      | 2.3  |      | V     |

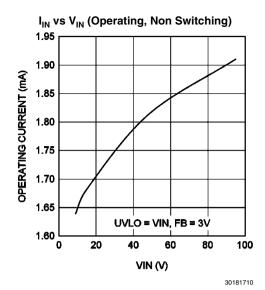

|                        | I <sub>IN</sub> Operating Current                                            | Non-Switching, FB = 3V                        |      | 1.75 |      | mA    |

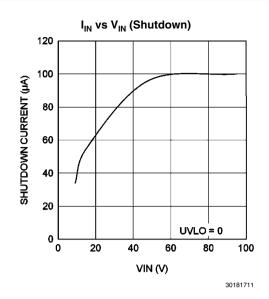

|                        | I <sub>IN</sub> Shutdown Current                                             | UVLO = 0V                                     |      | 50   | 225  | μΑ    |

| Switch Chai            | racteristics                                                                 |                                               |      |      | •    |       |

|                        | Buck Switch R <sub>DS(ON)</sub>                                              | I <sub>TEST</sub> = 200mA, BST-SW = 7V        |      | 0.8  | 1.8  | Ω     |

|                        | Synchronous R <sub>DS(ON)</sub>                                              | I <sub>TEST</sub> = 200mA                     |      | 0.45 | 1    | Ω     |

|                        | Gate Drive UVLO                                                              | V <sub>BST</sub> – V <sub>SW</sub> Rising     | 2.4  | 3    | 3.6  | V     |

|                        | Gate Drive UVLO Hysteresis                                                   |                                               |      | 260  |      | mV    |

| Current Lim            | it                                                                           | •                                             |      |      |      |       |

|                        | Current Limit Threshold                                                      |                                               | 150  | 240  | 300  | mA    |

|                        | Current Limit Response Time                                                  | Time to Switch Off                            |      | 150  |      | ns    |

|                        | Off-Time Generator (Test 1)                                                  | FB = 0.1V, V <sub>IN</sub> = 48V              |      | 12   |      | μs    |

|                        | Off-Time Generator (Test 2)                                                  | FB = 1V, V <sub>IN</sub> = 48V                |      | 2.5  |      | μs    |

| On-Time Ge             | enerator                                                                     | -                                             |      | ,    | •    |       |

|                        | T <sub>ON</sub> Test 1                                                       | V <sub>IN</sub> = 32V, R <sub>ON</sub> = 100k | 270  | 350  | 460  | ns    |

|                        | T <sub>ON</sub> Test 2                                                       | V <sub>IN</sub> = 48V, R <sub>ON</sub> = 100k | 188  | 250  | 336  | ns    |

|                        | T <sub>ON</sub> Test 3                                                       | $V_{IN} = 75V, R_{ON} = 250k$                 | 250  | 370  | 500  | ns    |

|                        | T <sub>ON</sub> Test 4                                                       | V <sub>IN</sub> = 10V, R <sub>ON</sub> = 250k | 1880 | 3200 | 4425 | ns    |

| Symbol        | Parameter                   | Conditions                                     | Min  | Тур   | Max  | Units |

|---------------|-----------------------------|------------------------------------------------|------|-------|------|-------|

| Minimum O     | ff-Time                     |                                                |      |       |      |       |

|               | Minimum Off-Timer           | FB = 0V                                        |      | 144   |      | ns    |

| Regulation    | and Overvoltage Comparators |                                                |      | •     |      | •     |

|               | FB Regulation Level         | Internal Reference Trip<br>Point for Switch ON | 1.2  | 1.225 | 1.25 | V     |

|               | FB Overvoltage Threshold    | Trip Point for Switch OFF                      |      | 1.62  |      | V     |

|               | FB Bias Current             |                                                |      | 60    |      | nA    |

| Undervolta    | ge Sensing Function         | ,                                              |      |       |      |       |

|               | UV Threshold                | UV Rising                                      | 1.19 | 1.225 | 1.26 | V     |

|               | UV Hysteresis Input Current | UV = 2.5V                                      | -10  | -20   | -29  | μΑ    |

|               | Remote Shutdown Threshold   | Voltage at UVLO Falling                        | 0.32 | 0.66  |      | V     |

|               | Remote Shutdown Hysteresis  |                                                |      | 110   |      | mV    |

| Thermal Sh    | utdown                      |                                                |      |       |      |       |

| Tsd           | Thermal Shutdown Temp.      |                                                |      | 165   |      | °C    |

|               | Thermal Shutdown Hysteresis |                                                |      | 20    |      | °C    |

| Thermal Re    | sistance                    | · ·                                            |      |       |      | •     |

| 0             | Junction to Ambient         | PSOP-8                                         |      | 40    |      | °C/W  |

| $\theta_{JA}$ |                             | LLP-8                                          |      | 40    |      | °C/W  |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics. The RTN pin is the GND reference electrically connected to the substrate.

Note 2: For detailed information on soldering plastic PSOP package, refer to the Packaging Data Book available from National Semiconductor Corporation. Max solder time not to exceed 4 seconds.

Note 3: All limits are guaranteed by design. All electrical characteristics having room temperature limits are tested during production at  $T_A = 25^{\circ}$ C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 4: V<sub>CC</sub> provides self bias for the internal gate drive and control circuits. Device thermal limitations limit external loading.

Note 5: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

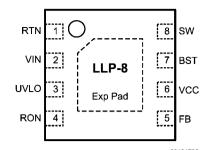

# **Typical Performance Characteristics**

30181712

# **Block Diagram**

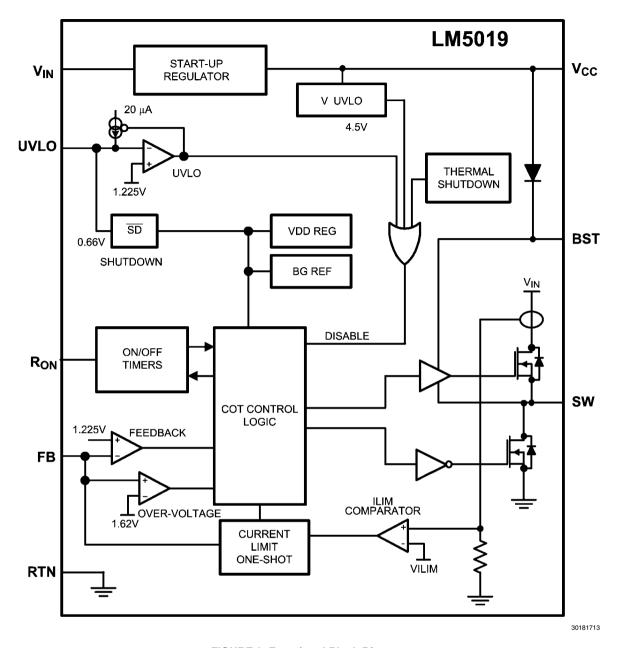

FIGURE 2. Functional Block Diagram

# **Functional Description**

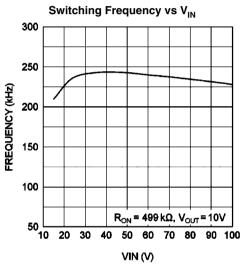

The LM5019 step-down switching regulator features all the functions needed to implement a low cost, efficient, buck converter capable of supplying up to 100mA to the load. This high voltage regulator contains 100V, N-channel buck and synchronous switches, is easy to implement, and is provided in thermally enhanced PSOP-8 and LLP-8 packages. The regulator operation is based on a constant on-time control scheme using an on-time inversely proportional to  $V_{\rm IN}$ . This control scheme does not require loop compensation. The current limit is implemented with a forced off-time inversely proportional to  $V_{\rm OUT}$ . This scheme ensures short circuit protection while providing minimum foldback. The simplified block diagram of the LM5019 is shown in *Figure 2*, Functional Block Diagram.

The LM5019 can be applied in numerous applications to efficiently regulate down higher voltages. This regulator is well suited for 48V telecom and 42V automotive power bus ranges. Protection features include: thermal shutdown, undervoltage lockout, minimum forced off-time, and an intelligent current limit.

#### **Control Overview**

The LM5019 buck regulator employs a control principle based on a comparator and a one-shot on-timer, with the output voltage feedback (FB) compared to an internal reference (1.225V). If the FB voltage is below the reference the internal buck switch is turned on for the one-shot timer period, which is a function of the input voltage and the programming resistor ( $R_{\rm ON}$ ). Following the on-time the switch remains off until the FB voltage falls below the reference, but never before the minimum off-time forced by the minimum off-time one-shot timer. When the FB pin voltage falls below the reference and the minimum off-time one-shot period expires, the buck switch is turned on for another on-time one-shot period. This will continue until regulation is achieved and the FB voltage is approximately equal to 1.225V (typ).

In a synchronous buck converter, the low side (sync) FET is 'on' when the high side (buck) FET is 'off'. The inductor current ramps up when the high side switch is 'on' and ramps down when the high side switch is 'off'. There is no diode emulation feature in this IC, and therefore, the inductor current may ramp in the negative direction at light load. This causes the converter to operate in continuous conduction mode (CCM) regardless of the output loading. The operating frequency remains relatively constant with load and line variations. The operating frequency can be calculated as follows:

$$f_{\rm sw} = \frac{V_{\rm OUT}}{10^{-10}\,\mathrm{x}\;\mathrm{R}_{\rm ON}}$$

The output voltage ( $V_{OUT}$ ) is set by two external resistors ( $R_{FB1}$ ,  $R_{FB2}$ ). The regulated output voltage is calculated as follows:

$$V_{OUT} = 1.225 V \times \frac{R_{FB2} + R_{FB1}}{R_{FB1}}$$

$$\frac{R_{FB2}}{R_{FB1}} = \frac{V_{OUT} - 1.225V}{1.225V}$$

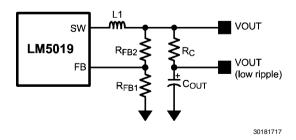

This regulator regulates the output voltage based on ripple voltage at the feedback input, requiring a minimum amount of ESR for the output capacitor ( $C_{OUT}$ ). A minimum of 25mV of ripple voltage at the feedback pin (FB) is required for the LM5019. In cases where the capacitor ESR is too small, additional series resistance may be required ( $R_{C}$  in *Figure 3* Low Ripple Output Configuration).

For applications where lower output voltage ripple is required the output can be taken directly from a low ESR output capacitor, as shown in *Figure 3* Low Ripple Output Configuration. However,  $R_{\rm C}$  slightly degrades the load regulation.

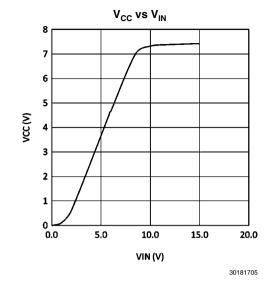

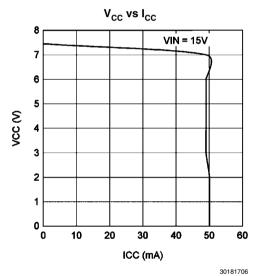

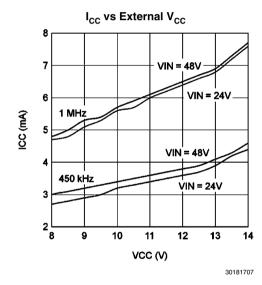

# **V<sub>CC</sub>** Regulator

The LM5019 contains an internal high voltage linear regulator with a nominal output of 7.6V. The input pin (V $_{\rm IN}$ ) can be connected directly to the line voltages up to 100V. The V $_{\rm CC}$  regulator is internally current limited to 30mA. The regulator sources current into the external capacitor at V $_{\rm CC}$ . This regulator supplies current to internal circuit blocks including the synchronous MOSFET driver and the logic circuits. When the voltage on the V $_{\rm CC}$  pin reaches the undervoltage lockout threshold of 4.5V, the IC is enabled.

The  $V_{\rm CC}$  regulator contains an internal diode connection to the BST pin to replenish the charge in the gate drive boot capacitor when SW pin is low.

At high input voltages, the power dissipated in the high voltage regulator is significant and can limit the overall achievable output power. As an example, with the input at 48V and switching at high frequency, the  $V_{CC}$  regulator may supply up to 7mA of current resulting in 48V x 7mA = 336mW of power dissipation. If the  $V_{CC}$  voltage is driven externally by an alternate voltage source, between 8V and 13V, the internal regulator is disabled. This reduces the power dissipation in the IC.

FIGURE 3. Low Ripple Output Configuration

### **Regulation Comparator**

The feedback voltage at FB is compared to an internal 1.225V reference. In normal operation, when the output voltage is in regulation, an on-time period is initiated when the voltage at FB falls below 1.225V. The high side switch will stay on for the on-time, causing the FB voltage to rise above 1.225V. After the on-time period, the high side switch will stay off until the FB voltage again falls below 1.225V. During start-up, the FB voltage will be below 1.225V at the end of each on-time, causing the high side switch to turn on immediately after the minimum forced off-time of 144ns. The high side switch can be turned off before the on-time is over, if the peak current in the inductor reaches the current limit threshold.

# **Overvoltage Comparator**

The feedback voltage at FB is compared to an internal 1.62V reference. If the voltage at FB rises above 1.62V the on-time pulse is immediately terminated. This condition can occur if the input voltage and/or the output load changes suddenly. The high side switch will not turn on again until the voltage at FB falls below 1.225V.

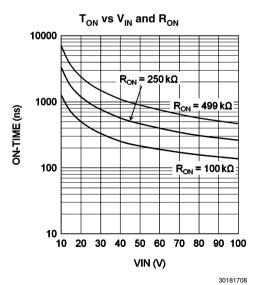

### **On-Time Generator**

The on-time for the LM5019 is determined by the  $R_{ON}$  resistor, and is inversely proportional to the input voltage ( $V_{IN}$ ), resulting in a nearly constant frequency as  $V_{IN}$  is varied over its range. The on-time equation for the LM5019 is:

$$T_{ON} = \frac{10^{-10} \text{ x R}_{ON}}{V_{IN}}$$

See figure " $T_{ON}$  vs  $V_{IN}$  and  $R_{ON}$ " in the section "Performance Curves".  $R_{ON}$  should be selected for a minimum on-time (at maximum  $V_{IN}$ ) greater than 100ns, for proper operation. This requirement limits the maximum switching frequency for high  $V_{IN}$ .

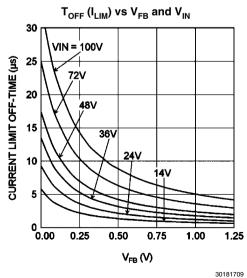

#### **Current Limit**

The LM5019 contains an intelligent current limit off-timer. If the current in the buck switch exceeds 240mA the present cycle is immediately terminated, and a non-resetable off-timer is initiated. The length of off-time is controlled by the FB voltage and the input voltage  $V_{\text{IN}}$ . As an example, when FB = 0V and  $V_{\text{IN}}$  = 48V, the maximum off-time is set to 16µs. This condition occurs when the output is shorted, and during the initial part of start-up. This amount of time ensures safe short circuit operation up to the maximum input voltage of 100V.

In cases of overload where the FB voltage is above zero volts (not a short circuit) the current limit off-time is reduced. Reducing the off-time during less severe overloads reduces the amount of foldback, recovery time, and start-up time. The off-time is calculated from the following equation:

$$T_{OFF(ILIM)} = \frac{0.07 \times V_{IN}}{V_{FB} + 0.2V} \ \mu s$$

The current limit protection feature is peak limited. The maximum average output will be less than the peak.

#### N-Channel Buck Switch and Driver

The LM5019 integrates an N-Channel Buck switch and associated floating high voltage gate driver. The gate driver circuit works in conjunction with an external bootstrap capacitor and an internal high voltage diode. A 0.01uF ceramic capacitor connected between the BST pin and the SW pin provides the voltage to the driver during the on-time. During each off-time, the SW pin is at approximately 0V, and the bootstrap capacitor charges from  $\rm V_{CC}$  through the internal diode. The minimum off-timer, set to 144ns, ensures a minimum time each cycle to recharge the bootstrap capacitor.

# **Synchronous Rectifier**

The LM5019 provides an internal synchronous N-Channel MOSFET rectifier. This MOSFET provides a path for the inductor current to flow when the high-side MOSFET is turned off.

The synchronous rectifier has no diode emulation mode, and is designed to keep the regulator in continuous conduction mode even during light loads which would otherwise result in discontinuous operation.

# **Undervoltage Detector**

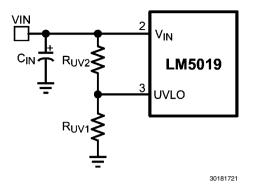

The LM5019 contains a dual level Undervoltage Lockout (UVLO) circuit. When the UVLO pin voltage is below 0.66V, the controller is in a low current shutdown mode. When the UVLO pin voltage is greater than 0.66V but less than 1.225V, the controller is in standby mode. In standby mode the  $V_{\rm CC}$  bias regulator is active while the regulator output is disabled. When the  $V_{\rm CC}$  pin exceeds the  $V_{\rm CC}$  undervoltage threshold and the UVLO pin voltage is greater than 1.225V, normal operation begins. An external set-point voltage divider from  $V_{\rm IN}$  to GND can be used to set the minimum operating voltage of the regulator.

UVLO hysteresis is accomplished with an internal 20 $\mu$ A current source that is switched on or off into the impedance of the set-point divider. When the UVLO threshold is exceeded, the current source is activated to quickly raise the voltage at the UVLO pin. The hysteresis is equal to the value of this current times the resistance  $R_{\rm LIV2}$ .

| UVLO           | V <sub>cc</sub>       | Mode      | Description                                                  |

|----------------|-----------------------|-----------|--------------------------------------------------------------|

| <0.66V         |                       | Shutdown  | V <sub>CC</sub> Regulator<br>Disabled.<br>Switcher Disabled. |

| 0.66V - 1.225V |                       | Standby   | V <sub>CC</sub> Regulator<br>Enabled<br>Switcher Disabled.   |

| >1.225V        | V <sub>CC</sub> <4.5V | Standby   | V <sub>CC</sub> Regulator<br>Enabled.<br>Switcher Disabled.  |

|                | V <sub>CC</sub> >4.5V | Operating | V <sub>CC</sub> enabled.<br>Switcher enabled.                |

If the UVLO pin is wired directly to the  $\rm V_{IN}$  pin, the regulator will begin operation once the  $\rm V_{CC}$  undervoltage is satisfied.

FIGURE 4. UVLO Resistor Setting

### **Thermal Protection**

The LM5019 should be operated so the junction temperature does not exceed 150°C during normal operation. An internal Thermal Shutdown circuit is provided to protect the LM5019 in the event of a higher than normal junction temperature.

When activated, typically at 165°C, the controller is forced into a low power reset state, disabling the buck switch and the  $V_{CC}$  regulator. This feature prevents catastrophic failures from accidental device overheating. When the junction temperature reduces below 145°C (typical hysteresis = 20°C), the  $V_{CC}$  regulator is enabled, and normal operation is resumed.

# **Application Information**

#### **SELECTION OF EXTERNAL COMPONENTS**

Selection of external components is illustrated through a design example. The design example specifications are as follows:

| Buck Converter Design Specifications |              |  |

|--------------------------------------|--------------|--|

| Input Voltage Range                  | 12.5V to 95V |  |

| Output Voltage                       | 10V          |  |

| Maximum Load Current                 | 100mA        |  |

| Switching Frequency                  | 400kHz       |  |

#### R<sub>FB1</sub>, R<sub>FB2</sub>:

$V_{OUT}=V_{FB}$  x ( $R_{FB2}/R_{FB1}+1$ ), and since  $V_{FB}=1.225V$ , the ratio of  $R_{FB2}$  to  $R_{FB1}$  calculates as 7:1. Standard values of 6.98kΩ and 1.00kΩ are chosen. Other values could be used as long as the 7:1 ratio is maintained.

#### Frequency Selection:

At the minimum input voltage, the maximum switching frequency of LM5019 is restricted by the forced minimum off-time  $(T_{OFF(MIN)})$  as given by:

$$f_{\text{SW(MAX)}} = \frac{1 - D_{\text{MAX}}}{T_{\text{OFF(MIN)}}} = \frac{1 - 10/12.5}{200 \text{ ns}} = 1 \text{ MHz}$$

Similarly, at maximum input voltage, the maximum switching frequency of LM5019 is restricted by the minimum  $T_{\rm ON}$  as given by:

$$f_{\text{SW(MAX)}} = \frac{D_{\text{MIN}}}{T_{\text{ON(MIN)}}} = \frac{10/95}{100 \text{ ns}} = 1.05 \text{ MHz}$$

Resistor  $R_{\text{ON}}$  sets the nominal switching frequency based on the following equations:

$$f_{\text{SW}} = \frac{V_{\text{OUT}}}{K \times R_{\text{ON}}}$$

where K = 1 x 10<sup>-10</sup>. Operation at high switching frequency results in lower efficiency while providing the smallest solution. For this example a 400kHz was selected, resulting in  $R_{ON}=246k\Omega.$  Selecting a standard value for  $R_{ON}=237k\Omega$  results in a nominal frequency of 416kHz.

#### **Inductor Selection:**

The inductance selection is a compromise between solution size, output ripple, and efficiency. The peak inductor current at maximum load current should be smaller than the minimum current limit of 150mA. The maximum permissible peak to peak inductor ripple is:

$$\Delta IL = 2*(I_{LIM(min)} - I_{OUT(max)} = 2*50 = 100mA$$

The minimum inductance is given by:

$$\Delta I_{L} = \frac{V_{IN} - V_{OUT}}{L1 \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}}$$

Resulting in L=215µH. A standard value of 220µH is selected. For proper operation the inductor saturation current should be higher than the peak encountered in the application. For robust short circuit protection, the inductor saturation current should be higher than the maximum current limit of 300mA.

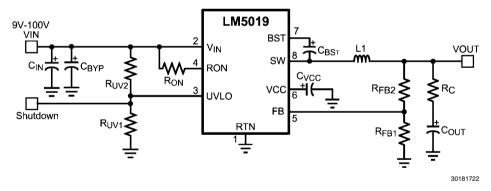

FIGURE 5. Reference Schematic for Selection of External Components

#### **Output Capacitor:**

The output capacitor is selected to minimize the capacitive ripple across it. The maximum ripple is observed at maximum input voltage and is given by:

$$C_{\text{OUT}} = \frac{\Delta I_{\text{L}}}{8 \times f_{\text{sw}} \times \Delta V_{\text{ripple}}}$$

where  $\Delta V_{ripple}$  is the voltage ripple across the capacitor. Substituting  $\Delta V_{ripple} = 10 mV$  gives  $C_{OUT} = 2.94 \mu F$ . A  $4.7 \mu F$  standard value is selected. An X5R or X7R type capacitor with a voltage rating 16V or higher should be selected.

#### Series Ripple Resistor R<sub>C</sub>:

The series resistor should be selected to produce sufficient ripple at the feedback node. The ripple produced by  $R_{\rm C}$  is proportional to the inductor current ripple, and therefore  $R_{\rm C}$  should be chosen for minimum inductor current ripple which occurs at minimum input voltage. The  $R_{\rm C}$  is calculated by the equation:

$$R_{\text{C}} \geq \frac{25\text{mV}}{\Delta I_{\text{L(MIN)}}} \quad x \quad \frac{V_{\text{OUT}}}{V_{\text{REF}}}$$

This gives an  $R_C$  of greater than or equal to  $10.8\Omega$ . Selecting  $R_C = 11\Omega$  results in ~1V of maximum output voltage ripple. For applications requiring lower output voltage ripple, Type II or Type III ripple injection circuits should be used as described in the section "Ripple Configuration".

#### V<sub>CC</sub> and Bootstrap Capacitor:

The  $V_{CC}$  capacitor provides charge to bootstrap capacitor as well as internal circuitry and low side gate driver. The Bootstrap capacitor provides charge to high side gate driver. A good value for  $C_{VCC}$  is 1µF. A good value for  $C_{BST}$  is 0.01µF.

#### **Input Capacitor:**

Input capacitor should be large enough to limit the input voltage ripple:

$$C_{IN} \ge \frac{I_{OUT(MAX)}}{8 \times f_{SW} \times \Delta V_{IN}}$$

choosing a  $\Delta V_{IN}=0.5V$  gives a minimum  $C_{IN}=0.12\mu F$ . A standard value of  $1\mu F$  is selected. The input capacitor should be rated for the maximum input voltage under all conditions. A 100V, X7R dielectric should be selected for this design.

Input capacitor should be placed directly across  $V_{IN}$  and RTN (pin 2 and 1) of the IC. If it is not possible to place all of the input capacitor close to the IC, a  $0.1\mu F$  capacitor should be placed near the IC to provide a bypass path for the high frequency component of the switching current. This helps limit the switching noise.

#### **UVLO Resistors:**

The UVLO resistors  $R_{FB1}$  and  $R_{FB2}$  set the UVLO threshold and hysteresis according to the following relationship:

$$V_{IN}(HYS) = I_{HYS} \times R_{UV2}$$

and

$$V_{IN}$$

(UVLO,rising) = 1.225V x  $\left(\frac{R_{UV2}}{R_{UV1}} + 1\right)$

where I $_{HYS}$  = 20 $\mu$ A. Setting UVLO hysteresis of 2.5V and UVLO rising threshold of 12V results in  $R_{UV1}$  = 14.53 $k\Omega$  and  $R_{UV2}$  = 125 $k\Omega$ . Selecting standard value of  $R_{UV1}$  = 14 $k\Omega$  and  $R_{UV2}$  = 125 $k\Omega$  results in UVLO thresholds and hysteresis of 12.4V and 2.5V respectively.

# APPLICATION CIRCUIT: 12V TO 95V INPUT AND 10V, 100mA OUTPUT BUCK CONVERTER

The application schematic of a buck supply is shown in *Figure 6* below. For output voltage ( $V_{OUT}$ ) above the maximum regulation threshold of  $V_{CC}$  (8.3V, see electrical characteristics), the  $V_{CC}$  pin can be connected to  $V_{OUT}$  through a diode (D2), as shown below, for higher efficiency and lower power dissipation in the IC.

#### RIPPLE CONFIGURATION

LM5019 uses Constant-On-Time (COT) control scheme, in which the on-time is terminated by an on-timer, and the off-time is terminated by the feedback voltage ( $V_{FB}$ ) falling below the reference voltage ( $V_{REF}$ ). Therefore, for stable operation, the feedback voltage must decrease monotonically, in phase with the inductor current during the off-time. Furthermore, this change in feedback voltage ( $V_{FB}$ ) during off-time must be large enough to suppress any noise component present at the feedback node.

Table 1 shows three different methods for generating appropriate voltage ripple at the feedback node. Type 1 and Type 2 ripple circuits couple the ripple at the output of the converter to the feedback node (FB). The output voltage ripple has two components:

- Capacitive ripple caused by the inductor current ripple charging/discharging the output capacitor.

- Resistive ripple caused by the inductor current ripple flowing through the ESR of the output capacitor.

The capacitive ripple is not in phase with the inductor current. As a result, the capacitive ripple does not decrease monotonically during the off-time. The resistive ripple is in phase with the inductor current and decreases monotonically during the off-time. The resistive ripple must exceed the capacitive ripple at the output node ( $V_{\text{OUT}}$ ) for stable operation. If this condition is not satisfied unstable switching behavior is observed in COT converters, with multiple on-time bursts in close succession followed by a long off-time.

Type 3 ripple method uses  $R_r$  and  $C_r$  and the switch node (SW) voltage to generate a triangular ramp. This triangular ramp is ac coupled using  $C_{\rm ac}$  to the feedback node (FB). Since this circuit does not use the output voltage ripple, it is ideally suited for applications where low output voltage ripple is required. See application note AN-1481 for more details for each ripple generation method.

FIGURE 6. Final Schematic for 12V to 95V Input, and 10V, 100mA Output Buck Converter

| Type 1 Lowest Cost Configuration                                                 | Type 2 Reduced Ripple Configuration                                                       | Type 3 Minimum Ripple Configuration                                                                                                              |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| To FB  R <sub>FB1</sub> R <sub>FB2</sub> R <sub>C</sub> Cout  GND                | V <sub>OUT</sub> C <sub>ac</sub> R <sub>FB2</sub> R <sub>C</sub> To FB  GND               | Vout R <sub>r</sub> C <sub>r</sub> R <sub>FB2</sub> GND To FB                                                                                    |

| $R_C \ge \frac{25 \text{ mV}}{\Delta I_{L(MIN)}} \times \frac{V_{OUT}}{V_{REF}}$ | $C_{ac} \ge 5f_{sw}/(R_{FB2}  R_{FB1})$ $R_C \ge \frac{25 \text{ mV}}{\Delta I_{L(MIN)}}$ | $C_r = 3300 \text{ pF}$ $C_{ac} = 100 \text{ nF}$ $R_r C_r \le \frac{(V_{\text{IN(MIN)}} - V_{\text{OUT}}) \times T_{\text{ON}}}{25 \text{ mV}}$ |

#### LAYOUT RECOMMENDATION

A proper layout is essential for optimum performance of the circuit. In particular, the following guidelines should be observed:

- C<sub>IN</sub>: The loop consisting of input capacitor (C<sub>IN</sub>), V<sub>IN</sub> pin, and RTN pin carries switching currents. Therefore, the input capacitor should be placed close to the IC, directly across V<sub>IN</sub> and RTN pins and the connections to these two pins should be direct to minimize the loop area. In general it is not possible to accommodate all of input capacitance near the IC. A good practice is to use a 0.1μF or 0.47μF capacitor directly across the V<sub>IN</sub> and RTN pins close to the IC, and the remaining bulk capacitor as close as possible (Refer to Figure 7 Placement of Bypass Capacitors).

- 2.  $C_{VCC}$  and  $C_{BST}$ : The  $V_{CC}$  and bootstrap (BST) bypass capacitors supply switching currents to the high and low

- side gate drivers. These two capacitors should also be placed as close to the IC as possible, and the connecting trace length and loop area should be minimized (See Figure 7 Placement of Bypass Capacitors).

- 3. The Feedback trace carries the output voltage information and a small ripple component that is necessary for proper operation of LM5019. Therefore, care should be taken while routing the feedback trace to avoid coupling any noise to this pin. In particular, feedback trace should not run close to magnetic components, or parallel to any other switching trace.

- 4. SW trace: The SW node switches rapidly between V<sub>IN</sub> and GND every cycle and is therefore a possible source of noise. The SW node area should be minimized. In particular, the SW node should not be inadvertently connected to a copper plane or pour.

FIGURE 7. Placement of Bypass Capacitors

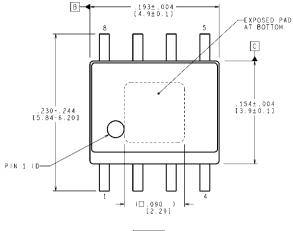

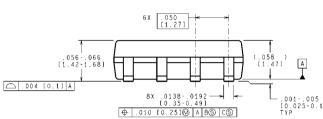

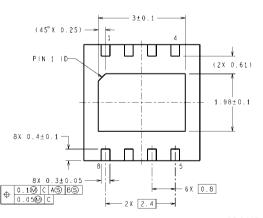

# Physical Dimensions inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS INCH VALUES IN [] ARE MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY

MRA08A (Rev D)

# PSOP-8 Outline Drawing NS Package Number MRA08A

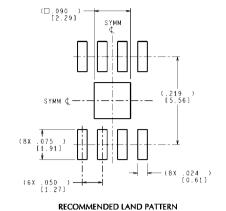

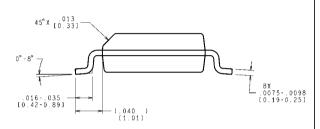

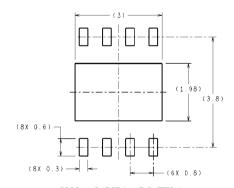

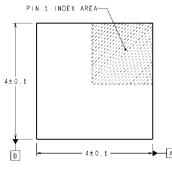

# DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY

(0.1)

# RECOMMENDED LAND PATTERN

SDC08B (Rev A)

8-Lead LLP Package NS Package Number SDC08B

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

**Applications**

Automotive and Transportation www.ti.com/automotive

e2e.ti.com

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|                   |                        | •                           |                                   |

|-------------------|------------------------|-----------------------------|-----------------------------------|

| Amplifiers        | amplifier.ti.com       | Communications and Telecom  | www.ti.com/communications         |

| Data Converters   | dataconverter.ti.com   | Computers and Peripherals   | www.ti.com/computers              |

| DLP® Products     | www.dlp.com            | Consumer Electronics        | www.ti.com/consumer-apps          |

| DSP               | dsp.ti.com             | Energy and Lighting         | www.ti.com/energy                 |

| Clocks and Timers | www.ti.com/clocks      | Industrial                  | www.ti.com/industrial             |

| Interface         | interface.ti.com       | Medical                     | www.ti.com/medical                |

| Logic             | logic.ti.com           | Security                    | www.ti.com/security               |

| Power Mgmt        | power.ti.com           | Space, Avionics and Defense | www.ti.com/space-avionics-defense |

| Microcontrollers  | microcontroller.ti.com | Video and Imaging           | www.ti.com/video                  |

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

**Products**

Audio

Wireless Connectivity www.ti.com/wirelessconnectivity

www.ti.com/audio

TI E2E Community Home Page

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated