# LM5000 High Voltage Switch Mode Regulator

## **General Description**

The LM5000 is a monolithic integrated circuit specifically designed and optimized for flyback, boost or forward power converter applications. The internal power switch is rated for a maximum of 80V, with a current limit set to 2A. Protecting the power switch are current limit and thermal shutdown circuits. The current mode control scheme provides excellent rejection of line transients and cycle-by-cycle current limiting. An external compensation pin and the built-in slope compensation allow the user to optimize the frequency compensation. Other distinctive features include softstart to reduce stresses during start-up and an external shutdown pin for remote ON/ OFF control. There are two operating frequency ranges available. The LM5000-3 is pin selectable for either 300kHz (FS Grounded) or 700kHz (FS Open). The LM5000-6 is pin selectable for either 600kHz (FS Grounded) or 1.3MHz (FS Open). The device is available in a low profile 16-lead TSSOP package or a thermally enhanced 16-lead LLP package.

## **Features**

- 80V internal switch

- Operating input voltage range of 3.1V to 40V

- Pin selectable operating frequency 300kHz/700kHz (-3) 600kHz/1.3MHz (-6)

- Adjustable output voltage

- External compensation

- Input undervoltage lockout

- Softstart

- Current limit

- Over temperature protection

- External shutdown

- Small 16-Lead TSSOP or 16-Lead LLP package

## **Applications**

- Flyback Regulator

- Forward Regulator

- Boost Regulator

- DSL Modems

- Distributed Power Converters

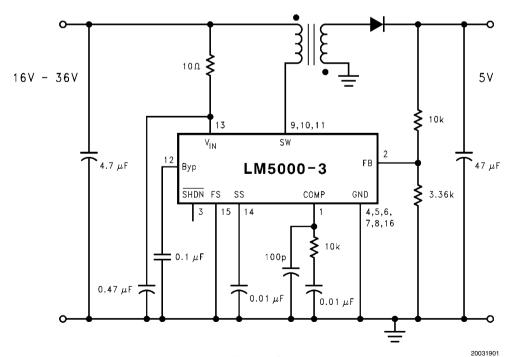

## **Typical Application Circuit**

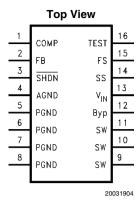

# **Connection Diagram**

# **Ordering Information**

|              | ı            |                     |                           |

|--------------|--------------|---------------------|---------------------------|

| Order Number | Package Type | NSC Package Drawing | Supplied As               |

| LM5000-3MTC  | TSSOP-16     | MTC16               | 94 Units, Rail            |

| LM5000-3MTCX | TSSOP-16     | MTC16               | 2500 Units, Tape and Reel |

| LM5000SD-3   | LLP-16       | SDA16               | 1000 Units, Rail          |

| LM5000SDX-3  | LLP-16       | SDA16               | 4500 Units, Tape and Reel |

| LM5000SD-6   | LLP-16       | SDA16               | 1000 Units, Rail          |

| LM5000SDX-6  | LLP-16       | SDA16               | 4500 Units, Tape and Reel |

# **Pin Descriptions**

| Pin | Name                                       | Function                                                                                                                                                                                                                             |

|-----|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | COMP                                       | Compensation network connection. Connected to the output of the voltage error amplifier. The RC compensation network should be connected from this pin to AGND. An additional 100pF high frequency capacitor to AGND is recommended. |

| 2   | FB                                         | Output voltage feedback input.                                                                                                                                                                                                       |

| 3   | SHDN                                       | Shutdown control input, Open = enable, Ground = disable.                                                                                                                                                                             |

| 4   | AGND                                       | Analog ground, connect directly to PGND.                                                                                                                                                                                             |

| 5   | PGND                                       | Power ground.                                                                                                                                                                                                                        |

| 6   | PGND                                       | Power ground.                                                                                                                                                                                                                        |

| 7   | PGND                                       | Power ground.                                                                                                                                                                                                                        |

| 8   | PGND                                       | Power ground.                                                                                                                                                                                                                        |

| 9   | SW                                         | Power switch input. Switch connected between SW pins and PGND pins                                                                                                                                                                   |

| 10  | SW                                         | Power switch input. Switch connected between SW pins and PGND pins                                                                                                                                                                   |

| 11  | SW                                         | Power switch input. Switch connected between SW pins and PGND pins                                                                                                                                                                   |

| 12  | BYP                                        | Bypass-Decouple Capacitor Connection, 0.1µF ceramic capacitor recommended.                                                                                                                                                           |

| 13  | V <sub>IN</sub>                            | Analog power input. A small RC filter is recommended, to suppress line glitches. Typical values of                                                                                                                                   |

|     |                                            | 10Ω and ≥ 0.1μF are recommended.                                                                                                                                                                                                     |

| 14  | SS                                         | Softstart Input. External capacitor and internal current source sets the softstart time.                                                                                                                                             |

| 15  | FS                                         | Switching frequency select input. Open = $F_{high}$ . Ground = $F_{low}$                                                                                                                                                             |

| 16  | TEST                                       | Factory test pin, connect to ground.                                                                                                                                                                                                 |

| -   | Exposed Pad<br>underside of LLP<br>package | Connect to system ground plane for reduced thermal resistance.                                                                                                                                                                       |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$V_{IN}$ -0.3V to 40V SW Voltage -0.3V to 80V FB Voltage -0.3V to 5V **COMP Voltage** -0.3V to 3V All Other Pins -0.3V to 7V Maximum Junction Temperature 150°C Power Dissipation(Note 2) Internally Limited Lead Temperature 216°C

Infrared (15 sec.) 235°C

ESD Susceptibility (Note 3)

Human Body Model 2kV

Machine Model 200V

Storage Temperature -65°C to +150°C

## **Operating Conditions**

Operating Junction Temperature Range (Note 7)

$\begin{array}{ccc} \mbox{(Note 7)} & -40^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \mbox{Supply Voltage (Note 7)} & 3.1\mbox{V o } 40\mbox{V} \end{array}$

## **Electrical Characteristics**

Specifications in standard type face are for  $T_J=25^{\circ}C$  and those with **boldface type** apply over the full **Operating Temperature Range** ( $T_J=-40^{\circ}C$  to +125°C) Unless otherwise specified.  $V_{IN}=12V$  and  $I_L=0A$ , unless otherwise specified.

| Symbol                             | Parameter                           | Conditions                                     | Min<br>(Note 4) | Typ<br>(Note 5) | Max<br>(Note 4) | Units |

|------------------------------------|-------------------------------------|------------------------------------------------|-----------------|-----------------|-----------------|-------|

| IQ                                 | Quiescent Current                   | FB = 2V (Not Switching)<br>FS = 0V             |                 | 2.0             | 2.5             | mA    |

|                                    |                                     | FB = 2V (Not Switching)<br>FS = Open           |                 | 2.1             | 2.5             | mA    |

|                                    |                                     | $V_{\overline{SHDN}} = 0V$                     |                 | 18              | 30              | μΑ    |

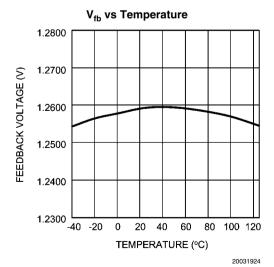

| V <sub>FB</sub>                    | Feedback Voltage                    |                                                | 1.2330          | 1.259           | 1.2840          | V     |

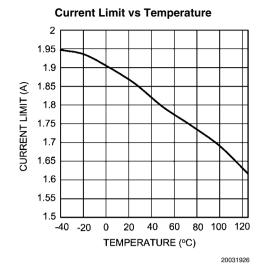

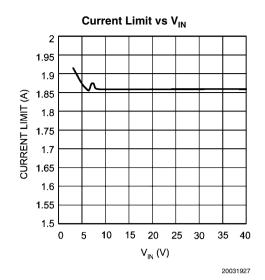

| I <sub>CL</sub>                    | Switch Current Limit                |                                                | 1.35            | 2.0             | 2.7             | Α     |

| %V <sub>FB</sub> /ΔV <sub>IN</sub> | Feedback Voltage Line<br>Regulation | $3.1V \le V_{IN} \le 40V$                      |                 | 0.001           | 0.04            | %/V   |

| I <sub>B</sub>                     | FB Pin Bias Current (Note 6)        |                                                |                 | 55              | 200             | nA    |

| BV                                 | Output Switch Breakdown             | $T_J = 25^{\circ}C, I_{SW} = 0.1\mu A$         | 80              |                 |                 | V     |

|                                    | Voltage                             | $T_J = -40$ °C to + 125°C, $I_{SW} = 0.5\mu A$ | 76              |                 |                 |       |

| V <sub>IN</sub>                    | Input Voltage Range                 |                                                | 3.1             |                 | 40              | V     |

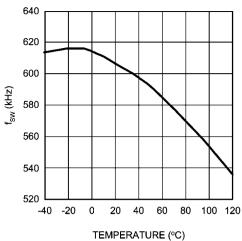

| g <sub>m</sub>                     | Error Amp Transconductance          | $\Delta I = 5\mu A$                            | 150             | 410             | 750             | μmho  |

| $A_V$                              | Error Amp Voltage Gain              |                                                |                 | 280             |                 | V/V   |

| D <sub>MAX</sub>                   | Maximum Duty Cycle<br>LM5000-3      | FS = 0V                                        | 85              | 90              |                 | %     |

|                                    | Maximum Duty Cycle<br>LM5000-6      | FS = 0V                                        | 85              | 90              |                 | %     |

| T <sub>MIN</sub>                   | Minimum On Time                     |                                                |                 | 165             |                 | ns    |

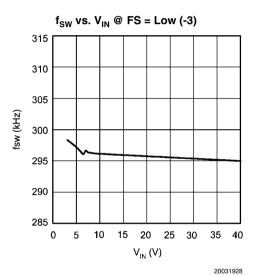

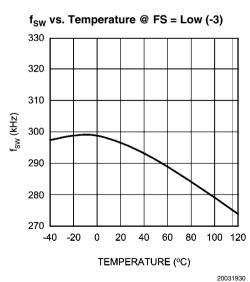

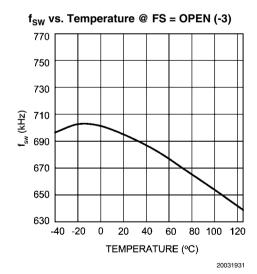

|                                    | Switching Frequency                 | FS = 0V                                        | 240             | 300             | 360             | 1.11= |

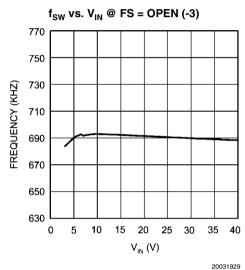

| f <sub>S</sub>                     | LM5000-3                            | FS = Open                                      | 550             | 700             | 840             | kHz   |

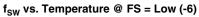

|                                    | Switching Frequency                 | FS = 0V                                        | 485             | 600             | 715             |       |

|                                    | LM5000-6                            | FS = Open                                      | 1.055           | 1.3             | 1.545           | MHz   |

| I <sub>SHDN</sub>                  | Shutdown Pin Current                | $V_{\overline{SHDN}} = 0V$                     |                 | -1              | -2              | μΑ    |

| IL                                 | Switch Leakage Current              | V <sub>SW</sub> = 80V                          |                 | 0.008           | 5               | μΑ    |

| R <sub>DSON</sub>                  | Switch R <sub>DSON</sub>            | I <sub>SW</sub> = 1A                           |                 | 160             | 445             | mΩ    |

| Th <sub>SHDN</sub>                 | SHDN Threshold                      | Output High                                    | 0.9             | 0.6             |                 | V     |

|                                    |                                     | Output Low                                     |                 | 0.6             | 0.3             | V     |

| UVLO                               | On Threshold                        |                                                | 2.74            | 2.92            | 3.10            | V     |

|                                    | Off Threshold                       |                                                | 2.60            | 2. 77           | 2.96            | V     |

| OVP                                | V <sub>COMP</sub> Trip              |                                                |                 | 0.67            |                 | V     |

| I <sub>SS</sub>                    | Softstart Current                   |                                                | 8               | 11              | 14              | μΑ    |

| Symbol        | Parameter          | Conditions          | Min<br>(Note 4) | Typ<br>(Note 5) | Max<br>(Note 4) | Units |

|---------------|--------------------|---------------------|-----------------|-----------------|-----------------|-------|

| $\theta_{JA}$ | Thermal Resistance | TSSOP, Package only |                 | 150             |                 | °C/W  |

|               |                    | LLP, Package only   |                 | 45              |                 |       |

Note 1: Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J(MAX)$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . See the Electrical Characteristics table for the thermal resistance of various layouts. The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_D(MAX) = (T_{J(MAX)} - T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown.

Note 3: The human body model is a 100 pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

Note 4: All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 5: Typical numbers are at 25°C and represent the most likely norm.

Note 6: Bias current flows into FB pin.

Note 7: Supply voltage, bias current product will result in aditional device power dissipation. This power may be significant. The thermal dissipation design should take this into account.

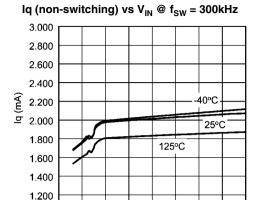

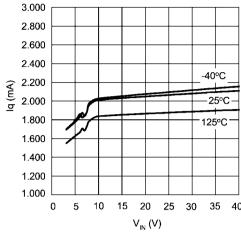

## **Typical Performance Characteristics**

20031920

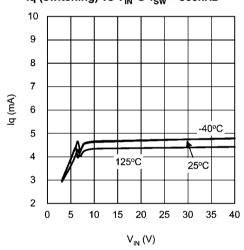

# Iq (non-switching) vs $V_{IN}$ @ $f_{SW} = 700kHz$

2003192

## Iq (switching) vs V<sub>IN</sub> @ f<sub>SW</sub> = 300kHz

$V_{IN}(V)$

10 15 20 25 30 35

1.000

20031922

5

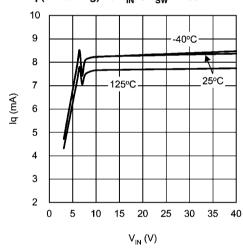

## Iq (switching) vs V<sub>IN</sub> @ f<sub>SW</sub> = 700kHz

20031923

350 300 125°C  $R_{DS}(ON)$  (m $\Omega$ ) 250 200 150 25°C 100 -40°C 50 5 10 15 20 25 35

$R_{DS(ON)}$  vs  $V_{IN}$  @  $I_{SW}$  =1A

400

20031925

VIN (V)

2003197

## Error Amp. Transconductance vs Temp.

20031932

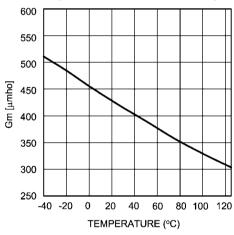

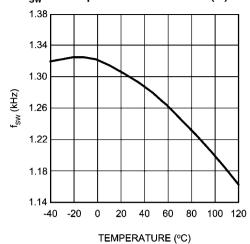

## f<sub>SW</sub> vs. Temperature @ FS = OPEN (-6)

20031975

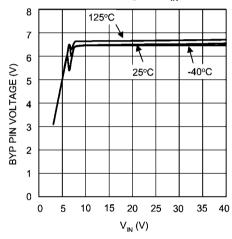

## BYP Pin Voltage vs V<sub>IN</sub>

20031933

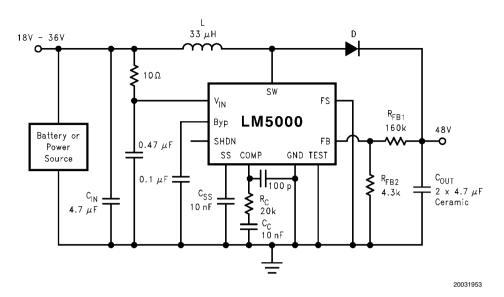

FIGURE 1. 300 kHz operation, 48V output

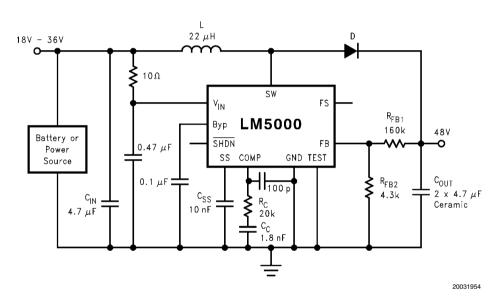

FIGURE 2. 700 kHz operation, 48V output

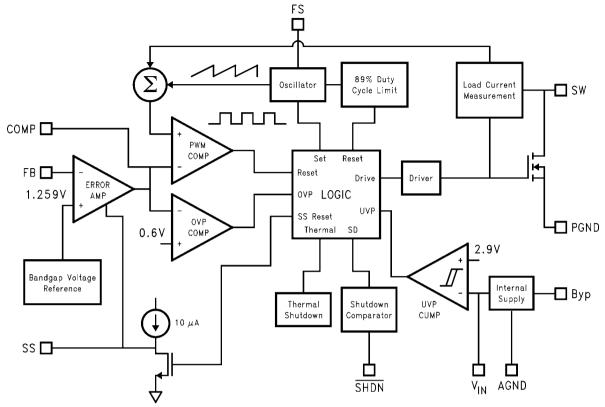

## **Block Diagram**

20031903

## **Boost Regulator Operation**

The LM5000 utilizes a PWM control scheme to regulate the output voltage over all load conditions. The operation can best be understood referring to the block diagram and Figure 3. At the start of each cycle, the oscillator sets the driver logic and turns on the NMOS power device conducting current through the inductor, cycle 1 of Figure 3 (a). During this cycle, the voltage at the COMP pin controls the peak inductor current. The COMP voltage will increase with larger loads and decrease with smaller. This voltage is compared with the summation of the SW volatge and the ramp compensation. The ramp compensation is used in PWM architectures to eliminate the sub-harmonic oscillations that occur during duty cycles greater than 50%. Once the summation of the ramp compensation and switch voltage equals the COMP voltage, the PWM comparator resets the driver logic turning off the NMOS power device. The inductor current then flows through the output diode to the load and output capacitor, cycle 2 of Figure 3 (b). The NMOS power device is then set by the oscillator at the

end of the period and current flows through the inductor once again.

The LM5000 has dedicated protection circuitry running during the normal operation to protect the IC. The Thermal Shutdown circuitry turns off the NMOS power device when the die temperature reaches excessive levels. The UVP comparator protects the NMOS power device during supply power startup and shutdown to prevent operation at voltages less than the minimum input voltage. The OVP comparator is used to prevent the output voltage from rising at no loads allowing full PWM operation over all load conditions. The LM5000 also features a shutdown mode. An external capacitor sets the softstart time by limiting the error amp output range, as the capacitor charges up via an internal 10µA current source.

The LM5000 is available in two operating frequency ranges. The LM5000-3 is pin selectable for either 300kHz (FS Grounded) or 700kHz (FS Open). The LM5000-6 is pin selectable for either 600kHz (FS Grounded) or 1.3MHz (FS Open)

## **Operation**

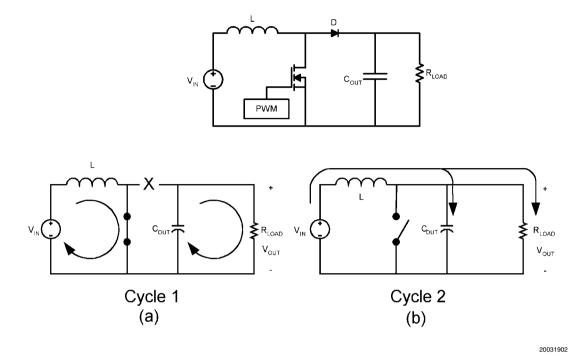

FIGURE 3. Simplified Boost Converter Diagram

(a) First Cycle of Operation (b) Second Cycle Of Operation

#### **CONTINUOUS CONDUCTION MODE**

The LM5000 is a current-mode, PWM regulator. When used as a boost regulator the input voltage is stepped up to a higher output voltage. In continuous conduction mode (when the inductor current never reaches zero at steady state), the boost regulator operates in two cycles.

In the first cycle of operation, shown in Figure 3 (a), the transistor is closed and the diode is reverse biased. Energy is collected in the inductor and the load current is supplied by  $\mathbf{C}_{\text{OUT}}$ .

The second cycle is shown in *Figure 3* (b). During this cycle, the transistor is open and the diode is forward biased. The energy stored in the inductor is transferred to the load and output capacitor.

The ratio of these two cycles determines the output voltage. The output voltage is defined approximately as:

$$V_{OUT} = \frac{V_{IN}}{1-D}, D' = (1-D) = \frac{V_{IN}}{V_{OUT}}$$

where D is the duty cycle of the switch, D and D $^\prime$  will be required for design calculations.

#### **SETTING THE OUTPUT VOLTAGE**

The output voltage is set using the feedback pin and a resistor divider connected to the output as shown in *Figure 1*. The feedback pin is always at 1.259V, so the ratio of the feedback resistors sets the output voltage.

$$R_{FB1} = R_{FB2} x \frac{V_{OUT} - 1.259}{1.259} \Omega$$

#### INTRODUCTION TO COMPENSATION

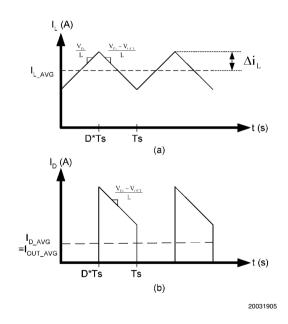

FIGURE 4. (a) Inductor current. (b) Diode current.

The LM5000 is a current mode PWM regulator. The signal flow of this control scheme has two feedback loops, one that senses switch current and one that senses output voltage.

To keep a current programmed control converter stable above duty cycles of 50%, the inductor must meet certain criteria. The inductor, along with input and output voltage, will determine the slope of the current through the inductor (see

Figure 4 (a)). If the slope of the inductor current is too great, the circuit will be unstable above duty cycles of 50%.

The LM5000 provides a compensation pin (COMP) to customize the voltage loop feedback. It is recommended that a series combination of  $\rm R_{\rm C}$  and  $\rm C_{\rm C}$  be used for the compensation network, as shown in *Figure 1*. The series combination of  $\rm R_{\rm C}$  and  $\rm C_{\rm C}$  introduces pole-zero pair according to the following equations:

$$f_{ZC} = \frac{1}{2\pi R_C C_C} Hz$$

$$f_{PC} = \frac{1}{2\pi(R_C + R_O)C_C} Hz$$

where  $R_O$  is the output impedance of the error amplifier,  $850k\Omega$ . For most applications, performance can be optimized by choosing values within the range  $5k\Omega \le R_C \le 20k\Omega$  and  $680pF \le C_C \le 4.7nF$ .

#### COMPENSATION

This section will present a general design procedure to help insure a stable and operational circuit. The designs in this datasheet are optimized for particular requirements. If different conversions are required, some of the components may need to be changed to ensure stability. Below is a set of general guidelines in designing a stable circuit for continuous conduction operation (loads greater than 100mA), in most all cases this will provide for stability during discontinuous operation as well. The power components and their effects will be determined first, then the compensation components will be chosen to produce stability.

#### INDUCTOR SELECTION

To ensure stability at duty cycles above 50%, the inductor must have some minimum value determined by the minimum input voltage and the maximum output voltage. This equation is:

$$L > \frac{V_{IN}R_{DSON}}{0.144 \text{ fs}} \left[ \frac{\left(\frac{D}{D'}\right)^2 - 1}{\left(\frac{D}{D'}\right) + 1} \right] (\text{in H})$$

where fs is the switching frequency, D is the duty cycle, and  $R_{\rm DSON}$  is the ON resistance of the internal switch. This equation is only good for duty cycles greater than 50% (D>0.5).

$$\Delta i_L = \frac{V_{IN}D}{2Lfs}$$

(in Amps)

The inductor ripple current is important for a few reasons. One reason is because the peak switch current will be the average inductor current (input current) plus  $\Delta i_L$ . Care must be taken to make sure that the switch will not reach its current limit during normal operation. The inductor must also be sized accordingly. It should have a saturation current rating higher than the peak inductor current expected. The output voltage ripple is also affected by the total ripple current.

#### DC GAIN AND OPEN-LOOP GAIN

Since the control stage of the converter forms a complete feedback loop with the power components, it forms a closed-

loop system that must be stabilized to avoid positive feedback and instability. A value for open-loop DC gain will be required, from which you can calculate, or place, poles and zeros to determine the crossover frequency and the phase margin. A high phase margin (greater than 45°) is desired for the best stability and transient response. For the purpose of stabilizing the LM5000, choosing a crossover point well below where the right half plane zero is located will ensure sufficient phase margin. A discussion of the right half plane zero and checking the crossover using the DC gain will follow.

#### **OUTPUT CAPACITOR SELECTION**

The choice of output capacitors is somewhat more arbitrary. It is recommended that low ESR (Equivalent Series Resistance, denoted  $\rm R_{ESR}$ ) capacitors be used such as ceramic, polymer electrolytic, or low ESR tantalum. Higher ESR capacitors may be used but will require more compensation which will be explained later on in the section. The ESR is also important because it determines the output voltage ripple according to the approximate equation:

After choosing the output capacitor you can determine a polezero pair introduced into the control loop by the following equations:

$$f_{P1} = \frac{1}{2\pi(R_{ESR} + R_L)C_{OUT}}$$

(in Hz)

$$f_{Z1} = \frac{1}{2\pi R_{ESR} C_{OUT}} \text{ (in Hz)}$$

Where  $\rm R_L$  is the minimum load resistance corresponding to the maximum load current. The zero created by the ESR of the output capacitor is generally very high frequency if the ESR is small. If low ESR capacitors are used it can be neglected. If higher ESR capacitors are used see the *High Output Capacitor ESR Compensation* section.

#### **RIGHT HALF PLANE ZERO**

A current mode control boost regulator has an inherent right half plane zero (RHP zero). This zero has the effect of a zero in the gain plot, causing an imposed +20dB/decade on the rolloff, but has the effect of a pole in the phase, subtracting another 90° in the phase plot. This can cause undesirable effects if the control loop is influenced by this zero. To ensure the RHP zero does not cause instability issues, the control loop should be designed to have a bandwidth of ½ the frequency of the RHP zero or less. This zero occurs at a frequency of:

$$\mathsf{RHPzero} = \frac{\mathsf{V}_{\mathsf{OUT}}(\mathsf{D'})^2}{2\pi \mathsf{I}_{\mathsf{LOAD}}\mathsf{L}} \, (\mathsf{in} \; \mathsf{Hz})$$

where  ${\rm I}_{\rm LOAD}$  is the maximum load current.

11

#### **SELECTING THE COMPENSATION COMPONENTS**

The first step in selecting the compensation components  $R_C$  and  $C_C$  is to set a dominant low frequency pole in the control loop. Simply choose values for  $R_C$  and  $C_C$  within the ranges given in the *Introduction to Compensation* section to set this pole in the area of 10Hz to 100Hz. The frequency of the pole created is determined by the equation:

$$f_{PC} = \frac{1}{2\pi(R_C + R_O)C_C}$$

(in Hz)

where  ${\rm R}_{\rm O}$  is the output impedance of the error amplifier,  $850{\rm k}\Omega.$  Since  ${\rm R}_{\rm C}$  is generally much less than  ${\rm R}_{\rm O},$  it does not have much effect on the above equation and can be neglected until a value is chosen to set the zero  ${\rm f}_{\rm ZC}.$  is created to cancel out the pole created by the output capacitor,  ${\rm f}_{\rm P1}.$  The output capacitor pole will shift with different load currents as shown by the equation, so setting the zero is not exact. Determine the range of  ${\rm f}_{\rm P1}$  over the expected loads and then set the zero  ${\rm f}_{\rm ZC}$  to a point approximately in the middle. The frequency of this zero is determined by:

$$f_{ZC} = \frac{1}{2\pi C_C R_C} \text{ (in Hz)}$$

Now R<sub>C</sub> can be chosen with the selected value for C<sub>C</sub>. Check to make sure that the pole  $f_{PC}$  is still in the 10Hz to 100Hz range, change each value slightly if needed to ensure both component values are in the recommended range. After checking the design at the end of this section, these values can be changed a little more to optimize performance if desired. This is best done in the lab on a bench, checking the load step response with different values until the ringing and overshoot on the output voltage at the edge of the load steps is minimal. This should produce a stable, high performance circuit. For improved transient response, higher values of R<sub>C</sub> (within the range of values) should be chosen. This will improve the overall bandwidth which makes the regulator respond more quickly to transients. If more detail is required, or the most optimal performance is desired, refer to a more in depth discussion of compensating current mode DC/DC switching regulators.

#### HIGH OUTPUT CAPACITOR ESR COMPENSATION

When using an output capacitor with a high ESR value, or just to improve the overall phase margin of the control loop, another pole may be introduced to cancel the zero created by the ESR. This is accomplished by adding another capacitor,  $C_{\rm C2},$  directly from the compensation pin  $V_{\rm C}$  to ground, in parallel with the series combination of  $R_{\rm C}$  and  $C_{\rm C}.$  The pole should be placed at the same frequency as  $f_{\rm Z1},$  the ESR zero. The equation for this pole follows:

$$f_{PC2} = \frac{1}{2\pi C_{C2}(R_{\odot}//R_{\odot})}$$

(in Hz)

To ensure this equation is valid, and that  $C_{C2}$  can be used without negatively impacting the effects of  $R_C$  and  $C_C$ ,  $f_{PC2}$  must be greater than  $10f_{PC}$ .

#### **CHECKING THE DESIGN**

The final step is to check the design. This is to ensure a bandwidth of 1/2 or less of the frequency of the RHP zero. This is done by calculating the open-loop DC gain,  $A_{DC}$ . After this value is known, you can calculate the crossover visually by placing a -20dB/decade slope at each pole, and a +20dB/decade slope for each zero. The point at which the gain plot crosses unity gain, or 0dB, is the crossover frequency. If the crossover frequency is at less than 1/2 the RHP zero, the phase margin should be high enough for stability. The phase margin can also be improved some by adding  $C_{C2}$  as discussed earlier in the section. The equation for  $A_{DC}$  is given below with additional equations required for the calculation:

$$A_{DC(DB)} = 20log_{10} \left(\!\!\left(\frac{R_{FB2}}{R_{FB1} + R_{FB2}}\right) \frac{g_m R_O D'}{R_{DSON}} \!\!\left\{\!\!\left[(\varpi \, \text{cLeff})\!/\!/ \; R_L \right]\!/\!/\!R_L \!\!\right\}\!\!\right) \! (\text{in dB})$$

$$\omega c \cong \frac{2fs}{nD'} \ \ (\text{in rad/s})$$

Leff =

$$\frac{L}{(D')^2}$$

$$n = 1 + \frac{2mc}{m1}$$

(no unit)

mc ≈ 0.072fs (in A/s)

$$m1 \cong \frac{V_{\text{IN}}R_{\text{DSON}}}{I} \ \ (\text{in V/s})$$

where  $\rm R_L$  is the minimum load resistance,  $\rm V_{IN}$  is the maximum input voltage, and  $\rm R_{DSON}$  is the value chosen from the graph " $\rm R_{DSON}$  vs.  $\rm V_{IN}$  " in the *Typical Performance Characteristics* section.

#### **SWITCH VOLTAGE LIMITS**

In a flyback regulator, the maximum steady-state voltage appearing at the switch, when it is off, is set by the transformer turns ratio, N, the output voltage,  $V_{OUT}$ , and the maximum input voltage,  $V_{IN}$  (Max):

$$V_{SW(OFF)} = V_{IN} (Max) + (V_{OUT} + V_F)/N$$

where  $V_F$  is the forward biased voltage of the output diode, and is typically 0.5V for Schottky diodes and 0.8V for ultrafast recovery diodes. In certain circuits, there exists a voltage spike,  $V_{LL}$ , superimposed on top of the steady-state voltage . Usually, this voltage spike is caused by the transformer leakage inductance and/or the output rectifier recovery time. To "clamp" the voltage at the switch from exceeding its maximum value, a transient suppressor in series with a diode is inserted across the transformer primary.

If poor circuit layout techniques are used, negative voltage transients may appear on the Switch pin. Applying a negative voltage (with respect to the IC's ground) to any monolithic IC pin causes erratic and unpredictable operation of that IC. This holds true for the LM5000 IC as well. When used in a flyback regulator, the voltage at the Switch pin can go negative when the switch turns on. The "ringing" voltage at the switch pin is caused by the output diode capacitance and the transformer leakage inductance forming a resonant circuit at the secondary(ies). The resonant circuit generates the "ringing" voltage, which gets reflected back through the transformer to the switch pin. There are two common methods to avoid this problem. One is to add an RC snubber around the output rectifier(s). The values of the resistor and the capacitor must be chosen so that the voltage at the Switch pin does not drop below -0.4V. The resistor may range in value between  $10\Omega$ and 1 k $\Omega$ , and the capacitor will vary from 0.001  $\mu F$  to 0.1 µF. Adding a snubber will (slightly) reduce the efficiency of the overall circuit.

The other method to reduce or eliminate the "ringing" is to insert a Schottky diode clamp between the SW pin and the PGND pin. The reverse voltage rating of the diode must be greater than the switch off voltage.

#### **OUTPUT VOLTAGE LIMITATIONS**

The maximum output voltage of a boost regulator is the maximum switch voltage minus a diode drop. In a flyback regulator, the maximum output voltage is determined by the turns ratio, N, and the duty cycle, D, by the equation:

$$V_{OUT}$$

$N \times V_{IN} \times D/(1 - D)$

The duty cycle of a flyback regulator is determined by the following equation:

$$D = \frac{V_{OUT} + V_F}{N(V_{IN} - V_{SAT}) + V_{OUT} + V_F} \approx \frac{V_{OUT}}{N(V_{IN}) + V_{OUT}}$$

Theoretically, the maximum output voltage can be as large as desired—just keep increasing the turns ratio of the transformer. However, there exists some physical limitations that prevent the turns ratio, and thus the output voltage, from increasing to infinity. The physical limitations are capacitances and inductances in the LM5000 switch, the output diode(s), and the transformer—such as reverse recovery time of the output diode (mentioned above).

#### INPUT LINE CONDITIONING

A small, low-pass RC filter should be used at the input pin of the LM5000 if the input voltage has an unusually large amount of transient noise. Additionally, the RC filter can reduce the dissipation within the device when the input voltage is high.

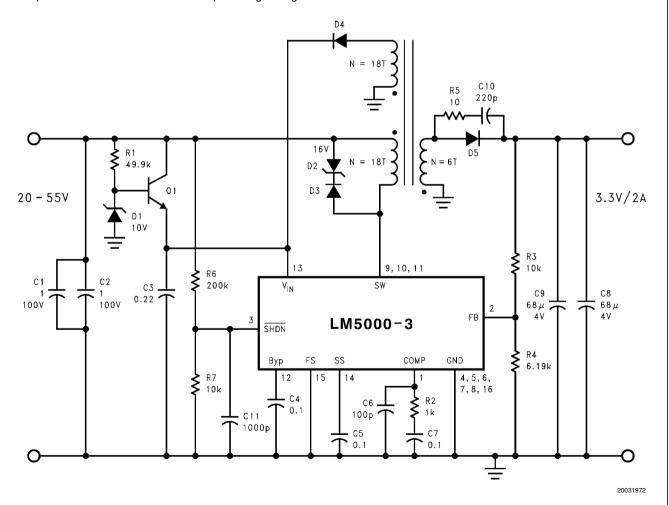

## **Flyback Regulator Operation**

The LM5000 is ideally suited for use in the flyback regulator topology. The flyback regulator can produce a single output voltage, or multiple output voltages.

The operation of a flyback regulator is as follows: When the switch is on, current flows through the primary winding of the transformer, T1, storing energy in the magnetic field of the transformer. Note that the primary and secondary windings are out of phase, so no current flows through the secondary when current flows through the primary. When the switch turns off, the magnetic field collapses, reversing the voltage polarity of the primary and secondary windings. Now rectifier D5 is forward biased and current flows through it, releasing the energy stored in the transformer. This produces voltage at the output.

The output voltage is controlled by modulating the peak switch current. This is done by feeding back a portion of the output voltage to the error amp, which amplifies the difference between the feedback voltage and a 1.259V reference. The error amp output voltage is compared to a ramp voltage proportional to the switch current (i.e., inductor current during the switch on time). The comparator terminates the switch on time when the two voltages are equal, thereby controlling the peak switch current to maintain a constant output voltage.

FIGURE 5. LM5000 Flyback Converter

| I | ГЕМ | PART NUMBER     | DESCRIPTION                             | VALUE       |

|---|-----|-----------------|-----------------------------------------|-------------|

| С | 1   | C4532X7R2A105MT | Capacitor, CER, TDK                     | 1μ, 100V    |

| С | 2   | C4532X7R2A105MT | Capacitor, CER, TDK                     | 1μ, 100V    |

| С | 3   | C1206C224K5RAC  | Capacitor, CER, KEMET                   | 0.22µ, 50V  |

| С | 4   | C1206C104K5RAC  | Capacitor, CER, KEMET                   | 0.1µ, 50V   |

| С | 5   | C1206C104K5RAC  | Capacitor, CER, KEMET                   | 0.1µ, 50V   |

| С | 6   | C1206C101K1GAC  | Capacitor, CER, KEMET                   | 100p, 100V  |

| С | 7   | C1206C104K5RAC  | Capacitor, CER, KEMET                   | 0.1μ, 50V   |

| С | 8   | C4532X7S0G686M  | Capacitor, CER, TDK                     | 68µ, 4V     |

| С | 9   | C4532X7S0G686M  | Capacitor, CER, TDK                     | 68µ, 4V     |

| С | 10  | C1206C221K1GAC  | Capacitor, CER, KEMET                   | 220p, 100V  |

| С | 11  | C1206C102K5RAC  | Capacitor, CER, KEMET                   | 1000p, 500V |

|   |     |                 |                                         |             |

| D | 1   | BZX84C10-NSA    | Central, 10V Zener, SOT-23              |             |

| D | 2   | CMZ5930B-NSA    | Central, 16V Zener, SMA                 |             |

| D | 3   | CMPD914-NSA     | Central, Switching, SOT-23              |             |

| D | 4   | CMPD914-NSA     | Central, Switching, SOT-23              |             |

| D | 5   | CMSH3-40L-NSA   | Central, Schottky, SMC                  |             |

|   |     |                 |                                         |             |

| Т | 1   | A0009-A         | Coilcraft, Transformer                  |             |

|   |     |                 |                                         |             |

| R | 1   | CRCW12064992F   | Resistor                                | 49.9K       |

| R | 2   | CRCW12061001F   | Resistor                                | 1K          |

| R | 3   | CRCW12061002F   | Resistor                                | 10K         |

| R | 4   | CRCW12066191F   | Resistor                                | 6.19K       |

| R | 5   | CRCW120610R0F   | Resistor                                | 10          |

| R | 6   | CRCW12062003F   | Resistor                                | 200K        |

| R | 7   | CRCW12061002F   | Resistor                                | 10K         |

|   |     | 0)/75554 NO.4   | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |             |

| Q | 1   | CXT5551-NSA     | Central, NPN, 180V                      |             |

| U | 1   | LM5000-3        | Regulator, National                     |             |

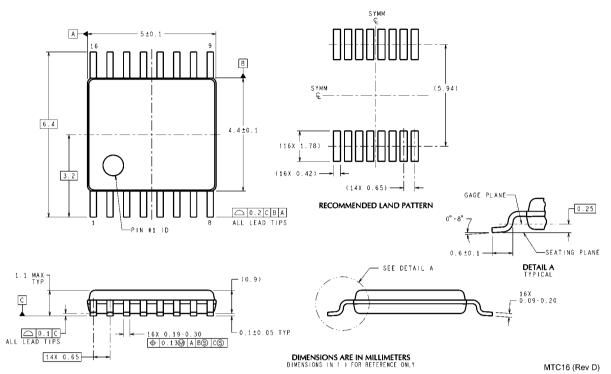

# Physical Dimensions inches (millimeters) unless otherwise noted

TSSOP-16 Pin Package (MTC)

For Ordering, Refer to Ordering Information Table

NS Package Number MTC16

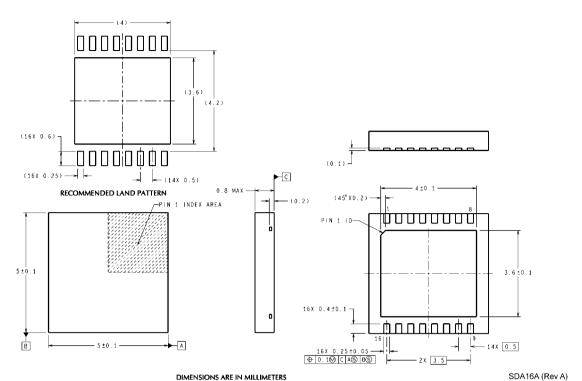

LLP-16 Pin Package (SDA)

For Ordering, Refer to Ordering Information Table

NS Package Number SDA16A

## **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560