**DAC8775** SLVSBY7-FEBRUARY 2017

# DAC8775 Quad-Channel, 16-Bit Programmable Current Output and Voltage Output **Digital-to-Analog Converter with Adaptive Power Management**

Technical

#### Features 1

- Output Current:

- 0 mA to 24 mA; 3.5 mA to 23.5 mA; 0 mA to 20 mA; 4 mA to 20 mA; ±24 mA

- Output Voltage (with/without 20% over-range):

- 0 V to 5 V; 0 V to 10 V; ±5 V; ±10 V

- 0 V to 6 V; 0 V to 12 V; ±6 V; ±12 V

- Adaptive Power Management

- Single Wide Power Supply Pin (12 V 36 V)

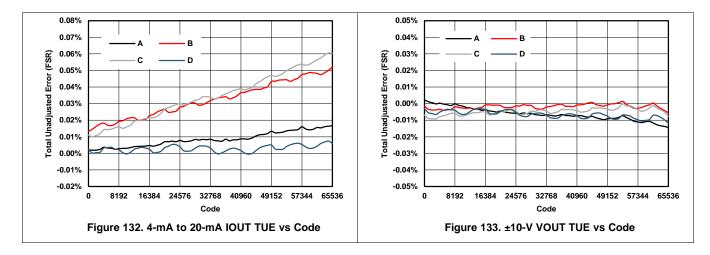

- ±0.1% FSR Total Unadjusted Error (TUE)

- DNL: ±1 LSB Max

- Internal 5-V Reference (10 ppm/°C max)

- Internal 5-V Digital Power Supply Output

- CRC/Frame Error Check, Watchdog Timer

- Thermal Alarm, Open/Short Circuit for System Reliability

- Safe Actions on Alarm Condition

- Auto Learn Load Detection

- Wide Temperature Range: -40°C to +125°C

#### Applications 2

- 4-mA to 20-mA Current Loops

- Analog Output Modules

- Programmable Logic Controllers (PLCs)

- **Building Automation**

- Sensor Transmitters

- Process Control

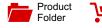

## 3 Description

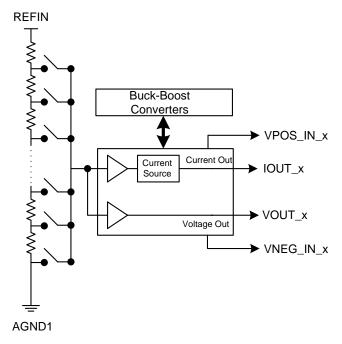

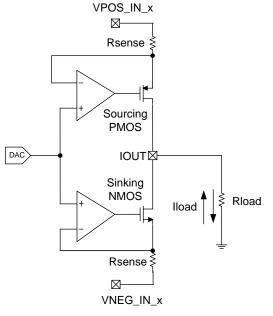

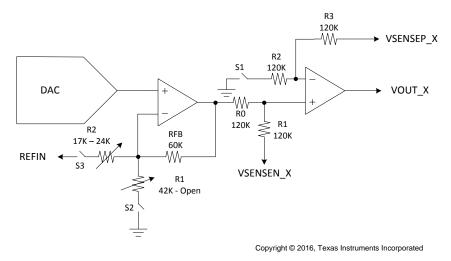

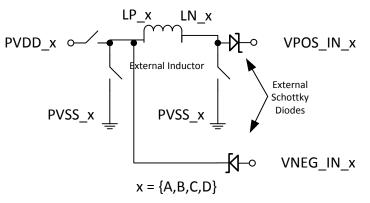

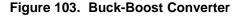

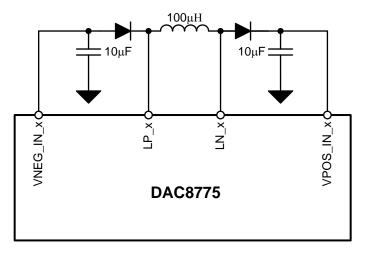

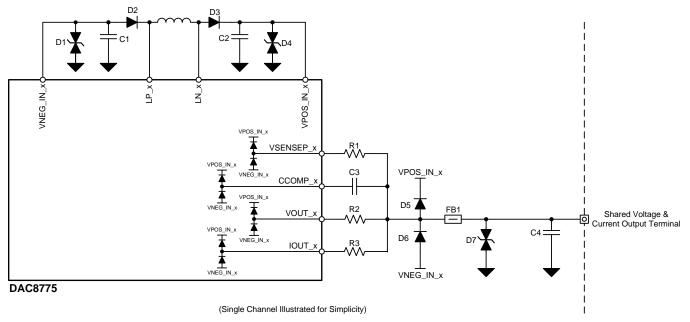

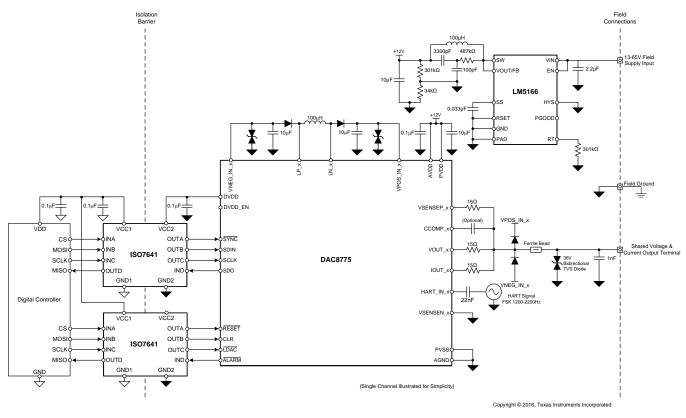

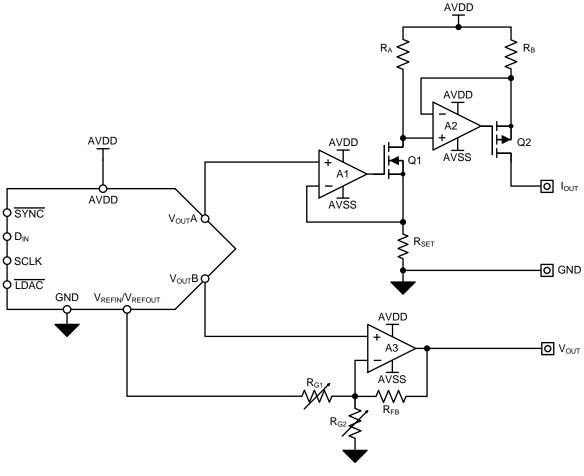

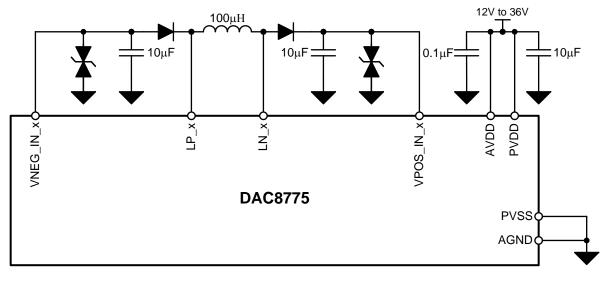

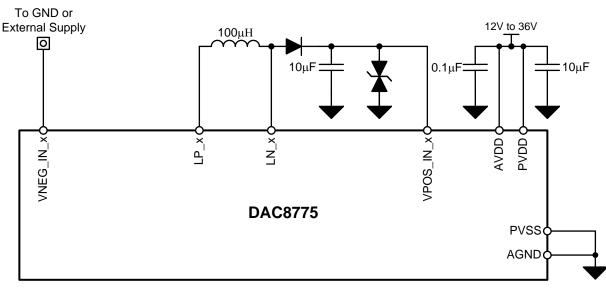

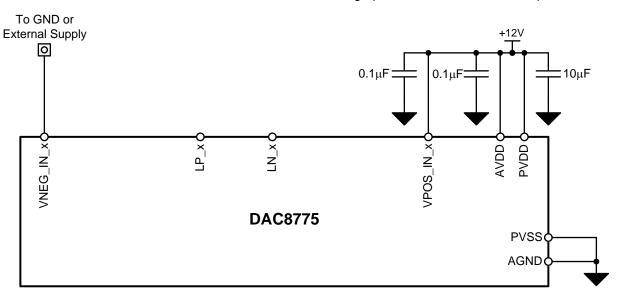

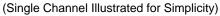

The DAC8775 is a guad-channel precision, fully integrated, 16-bit, digital-to-analog converter (DAC) with adaptive power management, and is designed to requirements of industrial meet the control applications. The adaptive power management when enabled, minimizes circuit. the power dissipation of the chip. When programmed as a current output, the supply voltage on the current output driver is regulated between 4.5 V and 32 V based on continuous feedback of voltage on the current output pin via an integrated buck/boost converter. When programmed as a voltage output, this circuit generates a programmable supply voltage for the voltage output stage (±15 V). DAC8775 also contains an LDO to generate the digital supply (5 V) from a single power supply pin.

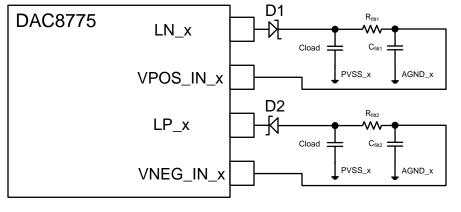

DAC8775 is also implemented with a Highway Addressable Remote Transducer (HART) Signal Interface to superimpose an external HART signal on the current output. The slew rate of the current output DAC is register programmable. The device can operate with a single external power supply of +12 V to +36 V using the integrated buck/boost converters or with external power supplies when the buck/boost converters are disabled.

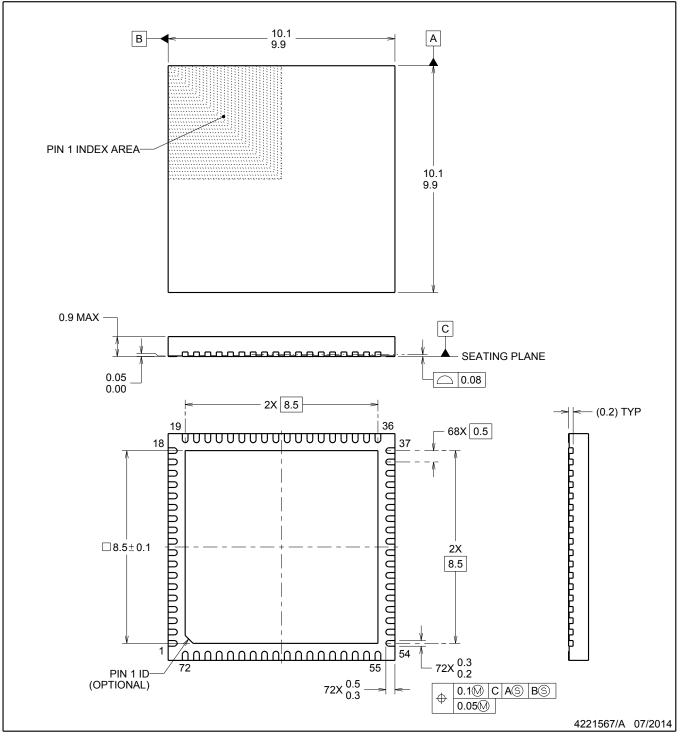

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| DAC8775     | VQFN (72) | 10.00 mm x 10.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

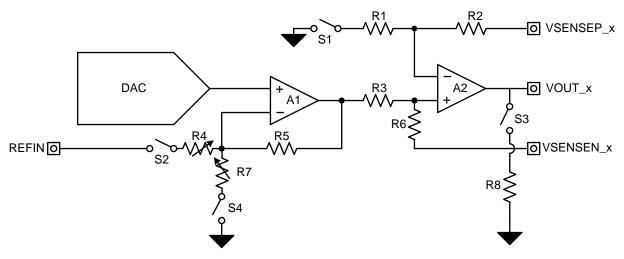

### Block Diagram

TEXAS INSTRUMENTS

www.ti.com

# **Table of Contents**

| 1 | Feat | tures 1                                          |

|---|------|--------------------------------------------------|

| 2 | Арр  | lications1                                       |

| 3 | Des  | cription1                                        |

| 4 | Rev  | ision History 2                                  |

| 5 | Dev  | ice Comparison Table 3                           |

| 6 | Pin  | Configuration and Functions 3                    |

| 7 | Spe  | cifications6                                     |

|   | 7.1  | Absolute Maximum Ratings 6                       |

|   | 7.2  | ESD Ratings 6                                    |

|   | 7.3  | Recommended Operating Conditions 6               |

|   | 7.4  | Thermal Information7                             |

|   | 7.5  | Electrical Characteristics7                      |

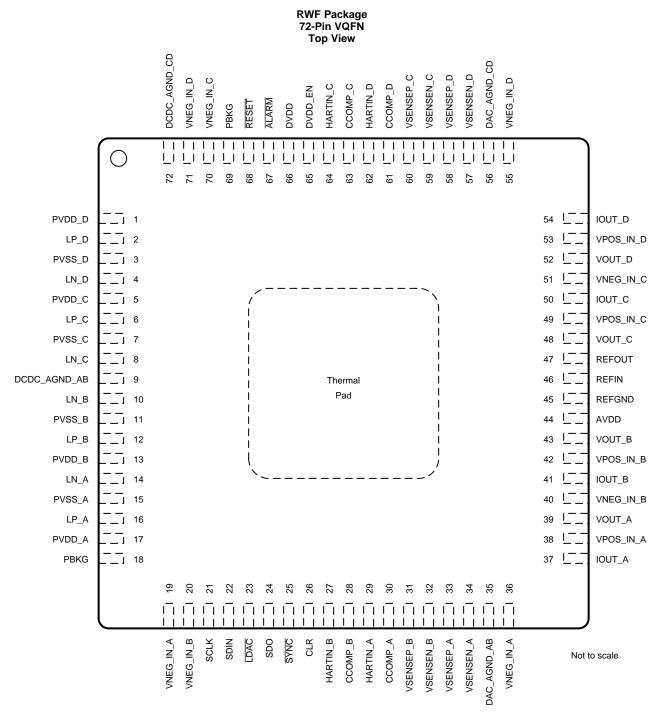

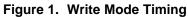

|   | 7.6  | Timing Requirements: Write and Readback Mode. 13 |

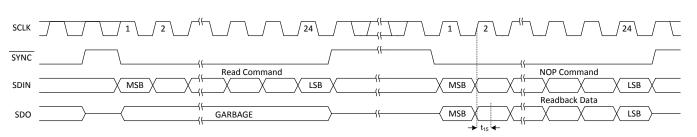

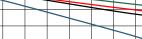

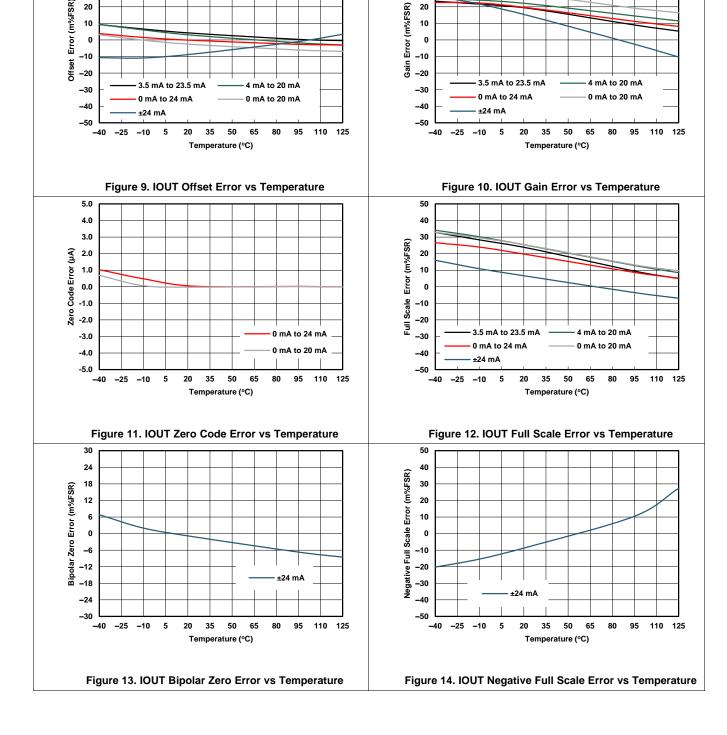

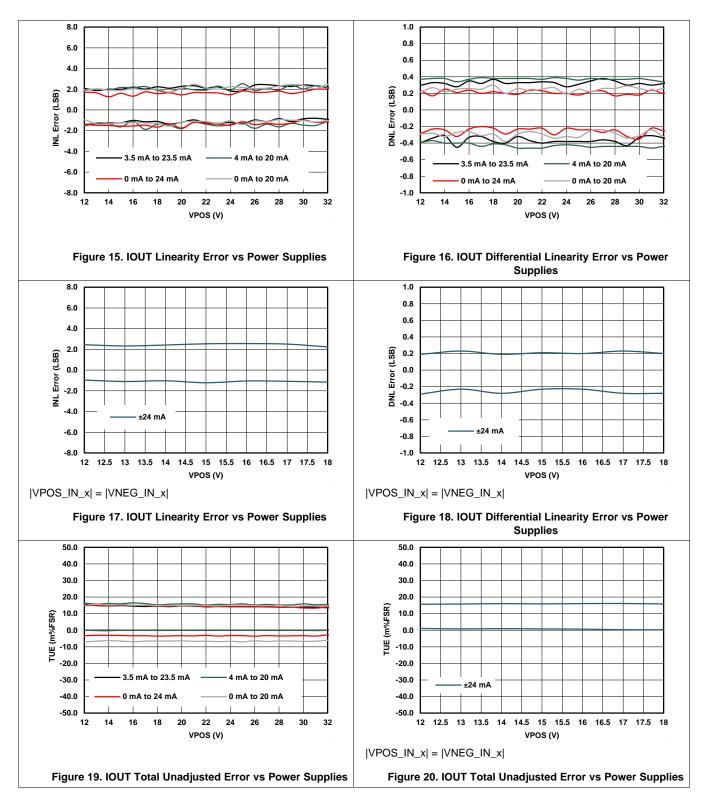

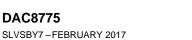

|   | 7.7  | Typical Characteristics 15                       |

| 8 | Deta | ailed Description 34                             |

|   | 8.1  | Overview                                         |

|   | 8.2  | Functional Block Diagram 34                      |

|   | 8.3  | Feature Description 34                           |

|   |      |                                                  |

|    | 8.4  | Device Functional Modes 4                         | 3 |

|----|------|---------------------------------------------------|---|

|    | 8.5  | Register Maps 4                                   | 7 |

| 9  | Арр  | lication and Implementation60                     | С |

|    | 9.1  | Application Information                           | C |

|    | 9.2  | Typical Application                               | 3 |

| 10 | Pow  | er Supply Recommendations6                        | 7 |

| 11 | Lay  | out6                                              | 9 |

|    | 11.1 | Layout Guidelines6                                | 9 |

|    | 11.2 | Layout Example 7                                  | 0 |

| 12 | Dev  | ice and Documentation Support72                   | 2 |

|    | 12.1 | Documentation Support7                            | 2 |

|    | 12.2 | Receiving Notification of Documentation Updates 7 | 2 |

|    | 12.3 | Community Resources                               | 2 |

|    | 12.4 | Trademarks 7                                      | 2 |

|    | 12.5 | Electrostatic Discharge Caution 7                 | 2 |

|    | 12.6 | Glossary7                                         | 2 |

| 13 |      | hanical, Packaging, and Orderable                 |   |

|    | Info | rmation                                           | 3 |

|    |      |                                                   |   |

# 4 Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| February 2017 | *        | Initial release. |

## 5 Device Comparison Table

| PRODUCT | RESOLUTION | DIFFERENTIAL<br>NONLINEARITY (LSB) |

|---------|------------|------------------------------------|

| DAC8775 | 16         | ±1                                 |

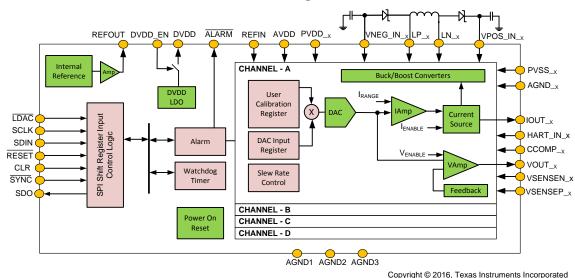

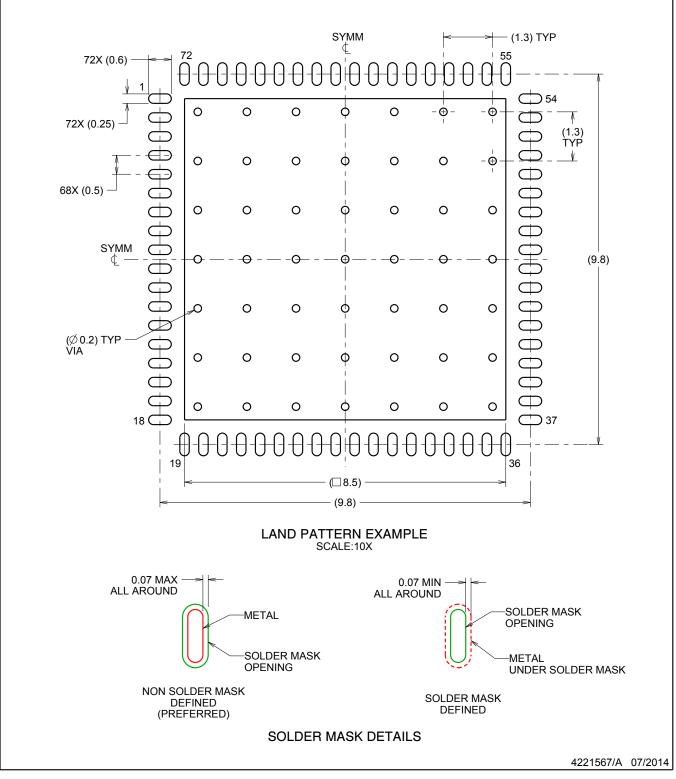

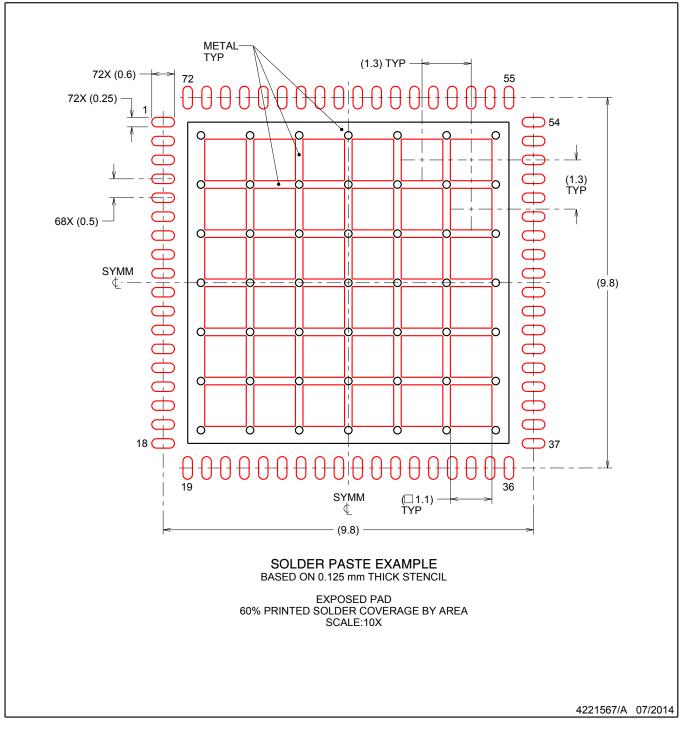

## 6 Pin Configuration and Functions

(1) Thermal pad should be connected to ground.

### **Pin Functions**

| NAME         NO.         DESCRIPTION           PVDD_D         1         Buck-Boost Converter power switch supply D           PL_D         2         External Inductor terminal - negative D           PVDD_C         5         Buck-Boost Converter power switch supply C           PVD_C         5         Buck-Boost Converter power switch supply C           PVD_C         6         External Inductor terminal - negative D           PVD_C         6         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter Switches B           LP_B         10         External Inductor terminal - negative B           PVDD_S         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative B           PVD_B         13         Buck-Boost Converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVD_A         17         Buck-Boost Converter power switch supply A           PKS         16         Ground for Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - negative A           PVD_D_A         17         Buck-Boost Converter powere switch supply A           PK                                                                                                                                                                                                                                                                                                                                                                                      | PIN         | Pin Functions |                                                                                                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|----------------------------------------------------------------------------------------------------|--|--|

| PVDD_D         1         Buck-Boost Converter power switch supply D           PVSD_D         2         External Inductor terminal - nogative D           PVSD_C         5         Buck-Boost Converter switches D           PVDD_C         5         Buck-Boost Converter switches D           PVDD_C         6         External Inductor terminal - negative C           PVSS_C         7         Ground for Buck-Boost converter switches C           LN_C         8         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter Switches C           LN_E         10         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative A           PVSS B         11         Ground for Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - negative A           PVDD_B         13         Buck-Boost Converter switch supply A           PVDA         16         External Inductor terminal - negative A           PVDA         17         Buck-Boost Converter power switch supply A           PVBC         18         Buck-Boost Converter power switch supply A                                                                                                                                                                                                                                                                                                                                                                                         |             |               | DESCRIPTION                                                                                        |  |  |

| LP_D         2         External Inductor terminal - positive D           PVSS_D         3         Ground for Buck-Boost converter switches D           NL_D         4         External Inductor terminal - positive C           PVDD_C         5         Buck-Boost Converter power switch supply C           LP_C         6         External Inductor terminal - positive C           PVSS_C         7         Ground for Buck-Boost converter switches C           LN_C         8         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter switches B           LP_B         10         External Inductor terminal - negative B           PVDD_B         13         Buck-Boost converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVDD_B         13         Buck-Boost Converter power switch supply A           PVDS_A         15         Ground for Buck-Boost converter switches A           LP_A         16         External Inductor terminal - negative A           PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VMEG_IN_B         20         Negative power supply for VOUT_A and IOUT_A                                                                                                                                                                                                                                                                                                                                                                            |             |               | Buck-Boost Converter power switch supply D                                                         |  |  |

| PVSS_D         3         Ground for Buck-Boost converter switches D           LN_D         4         External Inductor terminal - negative D           PVDD_C         5         Buck-Boost Converter yowns writch supply C           LP_C         6         External Inductor terminal - negative C           PVSS_C         7         Ground for Buck-Boost converter switches C           LN_C         8         External Inductor terminal - negative C           DCDC_AOND_AB         9         Analog GND Buck-Boost converter witches B           LN_B         10         External Inductor terminal - negative B           PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative A           PVDD_B         13         Buck-Boost Converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost converter switches A           LP_A         18         External Inductor terminal - negative A           PVDD_A         17         Buck-Boost Converter power switch supply A           PVBEG_IN_B         20         Negative power supply for VOUT_A and IOUT_A           VHEG_IN_B         20         Negative power supply for VOUT_A and IOU                                                                                                                                                                                                                                                                                                                                                            | _           |               |                                                                                                    |  |  |

| LN_D         4         External Inductor terminal - negative D           PVDD_C         5         Buck-Boost Converter power switch supply C           LP_C         6         External Inductor terminal - negative C           PVSS_C         7         Ground for Buck-Boost converter switches C           LN_G         8         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GNB Duck-Boost converter Switches B           LN_B         10         External Inductor terminal - negative B           PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - negative A           PVDD_A         17         Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - negative A           PVDD_A         17         Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - negative A           PVDD_A         17         Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - negative A           PVDD_A <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                            |             |               |                                                                                                    |  |  |

| PVDD_C         5         Buck-Boost Converter power switch supply C           LP_C         6         External Inductor terminal - positive C           PVSS_C         7         Ground for Buck-Boost converter switches C           LN_C         8         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter Switches B           LN_B         10         External Inductor terminal - negative A           PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative A           PVDD_A         14         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost converter switchs supply A           PVDD_A         16         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost Converter switchs supply A           PVBD_A         16         External Inductor terminal - positive A           PVDD_A         17         Buck-Boost Converter power switch supply A           PKEG         18         Chip substrate, connect to 0 V           VNEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           Stott         221         Serial data toput_Toger logic input.<                                                                                                                                                                                                                                                                                                                                                            | _           |               |                                                                                                    |  |  |

| LP_C         6         External Inductor terminal - positive C           PVSS_C         7         Ground for Buck-Boost converter switches C           LN_C         8         External Inductor terminal - agaive C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter switches D           PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - agaive A           PVSS_B         13         Buck-Boost Converter switches B           LP_B         12         External Inductor terminal - agaive A           PVDD_B         13         Buck-Boost Converter switches A           LP_A         16         External Inductor terminal - agaive A           PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VNEC_IN_A         19         Negative power supply for VOUT_A and IOUT_A           VNEC_IN_B         20         Negative power supply for VOUT_B and IOUT_A           ScILK         21         Serial data input. Data are docked into the 24-bit input shift register data into the DAC register and updates the AC output. A logic low on this pin loads the input shift register data into the DAC register and updates the AC output. A logic low on this pin loads the input shift register unless SYNC is low. When SY                                                                                                                                                                                                                                                                    |             |               |                                                                                                    |  |  |

| PVSS_C         7         Ground for Buck-Boost converter switches C           LN_C         8         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter Channels A and B           LN_B         10         External Inductor terminal - negative B           PVSS_B         11         Ground for Buck-Boost converter switches B           PVD_B         13         Buck-Boost Converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost converter switches A           PVAS         16         External Inductor terminal - negative A           PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VNEC_IN_A         19         Negative power supply for VOUT_A and IOUT_A           VNEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           SCLK         21         Schmit-Trigger logic input.           Solin         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input.           SDN         22         Serial data ouput. Data are valid on the falling edge of SCLK.           <                                                                                                                                                                                                                                                                                                                                      | _           | -             |                                                                                                    |  |  |

| LN_C         8         External Inductor terminal - negative C           DCDC_AGND_AB         9         Analog GND Buck-Boost converter Channels A and B           LN_B         10         External Inductor terminal - negative B           PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative A           PVDD_B         13         Buck-Boost converter switch supply B           LN_A         14         External Inductor terminal - negative A           PVDS_A         15         Ground for Buck-Boost converter switch supply A           PBKG         18         Chip substrate, connect to 0 V           VNEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           VNEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           Scluk         21         Serial data value. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input.           Scluk         21         Serial data value. Data are clocked into the 24-bit input shift register data into the DAC register and updates the DAC ouput.           EDRO         24         Serial data value. Data are clocked into the serial shift register data into the DAC register and updates the DAC ouput.           EDRO         24         Serial data value. Data are dicke walue o                                                                                                                                                                                                                                                                    |             |               |                                                                                                    |  |  |

| DCDC_AGND_AB         9         Analog GND Buck-Boost converter Channels A and B           LN_B         10         External Inductor terminal - negative B           PVSS_B         11         Ground for Buck-Boost converter switchs B           LP_B         12         External Inductor terminal - positive B           PVDD_B         13         Buck-Boost Converter power switch supply B           LN_A         14         External Inductor terminal - nositive A           PVSS_A         16         Ground for Buck-Boost Converter switchs apply A           PVDA         17         Buck-Boost Converter power switch supply A           PVDD_A         17         Buck-Boost Converter power switch supply A           PKG         18         Chip substrate, connect to V           VNEG_IN_A         19         Negative power supply for VOLT_A and IOUT_A           SCLK         21         Schrait-Trigger logic input.           Schrait-Trigger logic input.         Schrait-Trigger logic input.           SDIN         22         Serial dock input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schrait-Trigger logic input.           STNC         23         Load DAC lack control input. A logic low on this pin loads the input shift register unless SYNC is low. When SYNC is high. SDO is in high-impedance status.           CLR <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                          |             |               |                                                                                                    |  |  |

| LN_B         10         External Inductor terminal - negative B           PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - negative B           PVDD_B         13         Buck-Boost converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost converter switchs a           LP_A         16         External Inductor terminal - positive A           PVDD_B         13         Buck-Boost Converter power switch supply A           PKG         16         Chip substrate, connect to 0 V           VNEG_IN_A         19         Negative power supply for VOUT_B and IOUT_A           NMEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           Sclik         21         Serial dots input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schmitt-Trigger logic input.           SDO         24         Serial data input. Data are clocked into the 24-bit input shift register data into the DAC register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STVC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial                                                                                                                                                                                                                                                                     |             |               |                                                                                                    |  |  |

| PVSS_B         11         Ground for Buck-Boost converter switches B           LP_B         12         External Inductor terminal - positive B           PVDD_B         13         Buck-Boost Converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost converter switches A           LP_A         16         External Inductor terminal - positive A           PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VNEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           SCLK         21         Serial clock input 0 serial pripheral interface (SPI1 <sup>M</sup> ). Data can be transferred at rates up to 25 MHz.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schimt-Trigger logic input.           IDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC solpti.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is high. Sol is in high-impedance status.           CLR         26         Level Triggerelogic input.                                                                                                                                                                                                                              |             | -             | · ·                                                                                                |  |  |

| LP_B       12       External Inductor terminal - positive B         PVDD_B       13       Buck-Boost Converter power switch supply B         LN_A       14       External Inductor terminal - negative A         PVSS_A       15       Ground for Buck-Boost converter switches A         LP_A       16       External Inductor terminal - positive A         PVDD_A       17       Buck-Boost Converter power switch supply A         PBKG       18       Chip substrate, connect to 0 V         VINEG_IN_B       20       Negative power supply for VOUT_A and IOUT_A         SCLK       21       Serial clock input 0 serial peripheral interface (SPI**). Data can be transferred at rates up to 25 MHz.         SDIN       22       Serial clock input 0 serial peripheral interface (SPI**). Data can be transferred at rates up to 25 MHz.         SDIN       22       Serial data input. Data are clocked into the 24-bit input shift register data into the DAC register and updates the DAC output.         SDO       24       Serial data output. Data are valid on the falling edge of SCLK.         STNC       25       SPI bus chip select input (active lew). Data bis are not clocked into the serial shift register unless SYNC is low. When SYNC is high, SDO is in high-impedance status.         CLR       26       Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear section)                                                                                                                                                                                                                                                         |             | -             |                                                                                                    |  |  |

| PVDD_B         13         Buck-Boost Converter power switch supply B           LN_A         14         External Inductor terminal - negative A           PVSS_A         15         Ground for Buck-Boost converter switches A           LP_A         16         External Inductor terminal - positive A           PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VNEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           SCLK         21         Serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmit-Trigger logic input.           SDIN         22         Serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmit-Trigger logic input.           IDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC<br>register and updates the DAC output.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high. SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)           COMP_B         28         External compensation capacitor connection pin for VOUT_B.                                                                                                                                                              |             |               |                                                                                                    |  |  |

| LN_A       14       External Inductor terminal - negative A         PVSS.A       15       Ground for Buck-Boost converter switches A         LP_A       16       External Inductor terminal - positive A         PVDD.A       17       Buck-Boost Converter power switch supply A         PBKG       18       Chip substrate, connect to 0 V         VNEG_IN_A       19       Negative power supply for VOUT_A and IOUT_A         VNEG_IN_B       20       Negative power supply for VOUT_B and IOUT_A         SCLK       21       Serial clock input of serial peripheral interface (SPI™). Data can be transferred at rates up to 25 MHz.         Spin       22       Serial clock input of a are clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schmitt-Trigger logic input.         SDD       24       Serial data output. Data are clocked into the 24-bit input shift register data into the DAC register and updates the DAC output.         STNC       25       SPI bus chip select input (factive low). Data bits are not clocked into the serial shift register unless SYNC is low. When SYNC is high, SDO is in high-impedance status.         CLR       26       Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear section)         HARTIN_B       27       Input pin for HART modulation. for IOUT_B         CCOMP_B       28       External compensation capaci                                                                                                                                                                                                                                 |             |               |                                                                                                    |  |  |

| PVSS_A         15         Ground for Buck-Boost converter switches A           LP_A         16         External Inductor terminal - positive A           PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VINEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           SCLK         21         Serial clock input of serial peripheral interface (SPIT <sup>M</sup> ). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock<br>input. Schmitt-Trigger logic input.           IDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC<br>register and updates the DAC output.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high, SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)           HARTIN_B         27         Input pin for HART modulation. for IOUT_B           HARTIN_A         29         Input pin for HART modulation. for IOUT_B in by reducing the bandwidth of the output<br>ampliffer at the expense of increased settiling time.                                                                                                                    | _           | -             |                                                                                                    |  |  |

| LP_A       16       External Inductor terminal - positive A         PVDD_A       17       Buck-Boost Converter power switch supply A         PBKG       18       Chip substrate, connect to 0 V         VNEG_IN_A       19       Negative power supply for VOUT_A and IOUT_A         VNEG_IN_B       20       Negative power supply for VOUT_B and IOUT_A         SCLK       21       Serial clock input of serial peripheral interface (SPIT <sup>M</sup> ). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.         SDIN       22       Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schmitt-Trigger logic input.         IDAC       23       Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC output.         SDO       24       Serial data output. Data are valid on the falling edge of SCLK.         STNC       25       SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is logit, SDO is in logit, SDO is in logit, SDO is in logit, SDO is night, SDO is n                                  |             |               | 5                                                                                                  |  |  |

| PVDD_A         17         Buck-Boost Converter power switch supply A           PBKG         18         Chip substrate, connect to 0 V           VINEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           VINEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           SCLK         21         Serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.           LDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is low. When SYNC is high. SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active low). Data bits are not clocked into the external capacitor improves the stability with high capacitive loads at the VOUT_B . Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output amplifier at the expense of increased settling time.                                         | -           |               |                                                                                                    |  |  |

| PBKG         18         Chip substrate, connect to 0 V           VNEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           VNEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           SCLK         21         Serial clock input of serial peripheral interface (SPIT*). Data can be transferred at rates up to 25 MHz. Schmitt-Trigger logic input.           SDIN         22         Serial clock input of serial peripheral interface (SPIT*). Data can be transferred at rates up to 25 MHz. Schmitt-Trigger logic input.           IDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is low. When SYNC is high, SDO is in high-impedance status.           CLR         26         Level Triggerel delar pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear section).           HARTIN_B         27         Input pin for HART modulation. for IOUT_B           CCOMP_B         28         External compensation capacitor connection pin for VOUT_A. Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output amplifier at the expense of increased settling time. <td></td> <td></td> <td></td>                                                                    |             |               |                                                                                                    |  |  |

| VNEG_IN_A         19         Negative power supply for VOUT_A and IOUT_A           VNEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           SCLK         21         Serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock<br>input. Schmitt-Trigger logic input.           LDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC<br>register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high, SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)           HARTIN_B         27         Input pin for HART modulation. for IOUT_B           CCOMP_B         28         External compensation capacitor connection pin for VOUT_B i. Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.           CCOMP_A         30         External compensation capa                                                               | PVDD_A      | 17            |                                                                                                    |  |  |

| VNEG_IN_B         20         Negative power supply for VOUT_B and IOUT_A           SCLK         21         Serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock<br>input. Schmitt-Trigger logic input.           IDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC<br>register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high, SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)           HARTIN_B         27         Input pin for HART modulation. for IOUT_B           CCOMP_B         28         External compensation capacitor connection pin for VOUT_B in by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.           VSENSEP_B         31         Sense output pin for the positive voltage output (channel B) load connection.           VSENSEP_B         31         Sense output pin for the positive voltage output A pin by reducing the bandwidth of the outpu                                                                  | PBKG        | 18            | Chip substrate, connect to 0 V                                                                     |  |  |

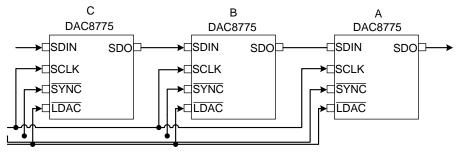

| SCLK         21         Serial clock input of serial peripheral interface (SPITM). Data can be transferred at rates up to 25 MHz.<br>Schmitt-Trigger logic input.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock<br>input. Schmitt-Trigger logic input.           LDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC<br>register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high, SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)           HARTIN_B         27         Input pin for HART modulation. for IOUT_B           CCOMP_B         28         External compensation capacitor connection pin for VOUT_B . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A bit pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling.           VCOMP_A         30         External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling. | VNEG_IN_A   | 19            | Negative power supply for VOUT_A and IOUT_A                                                        |  |  |

| SULK         21         Schmitt-Trigger logic input.           SDIN         22         Serial data input. Data are clocked into the 24-bit input shift register on the falling edge of the serial clock input. Schmitt-Trigger logic input.           LDAC         23         Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC output.           SDO         24         Serial data output. Data are valid on the falling edge of SCLK.           STNC         25         SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is low. When SYNC is high, SDO is in high-impedance status.           CLR         26         Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear section)           HARTIN_B         27         Input pin for HART modulation. for IOUT_B           CCOMP_B         28         External compensation capacitor connection pin for VOUT_B . Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output amplifier at the expense of increased setting time.           HARTIN_A         29         Input pin for HART modulation. for IOUT_A           COMP_A         30         External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output amplifiner at the expense of increased setting time.                                                  | VNEG_IN_B   | 20            | Negative power supply for VOUT_B and IOUT_A                                                        |  |  |

| SDIN       22       input. Schmiti-Trigger logic input.         LDAC       23       Load DAC latch control input. A logic low on this pin loads the input shift register data into the DAC register and updates the DAC output.         SDO       24       Serial data output. Data are valid on the falling edge of SCLK.         SYNC       25       SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC is high, SDO is in high-impedance status.         CLR       26       Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear section)         HARTIN_B       27       Input pin for HART modulation. for IOUT_B         CCOMP_B       28       External compensation capacitor connection pin for VOUT_B in by reducing the bandwidth of the output amplifier at the expense of increased settling time.         HARTIN_A       29       Input pin for HART modulation. for IOUT_A         COMP_A       30       External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output amplifier at the expense of increased settling time.         VSENSEP_B       31       Sense output pin for the positive voltage output (channel B) load connection.         VSENSEP_B       32       Sense output pin for the negative voltage output (channel A) load connection.         VSENSEP_A       33       Sense                                                                                                                                        | SCLK        | 21            |                                                                                                    |  |  |

| LDAC23register and updates the DAC output.SDO24Serial data output. Data are valid on the falling edge of SCLK.STNC25SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high, SDO is in high-impedance status.CLR26Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)HARTIN_B27Input pin for HART modulation. for IOUT_BCCOMP_B28External compensation capacitor connection pin for VOUT_B . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.HARTIN_A29Input pin for HART modulation. for IOUT_ACCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the positive voltage output (channel A) load connection.VSENSEP_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEP_A35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_A<                                                                                                                                                   | SDIN        | 22            |                                                                                                    |  |  |

| SYNC25SPI bus chip select input (active low). Data bis are not clocked into the serial shift register unless SYNC<br>is low. When SYNC is high, SDO is in high-impedance status.CLR26Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear<br>section)HARTIN_B27Input pin for HART modulation. for IOUT_BCCOMP_B28External compensation capacitor connection pin for VOUT_B. Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.HARTIN_A29Input pin for HART modulation. for IOUT_ACCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the negative voltage output (channel A) load connection.VSENSEP_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A34Sense output pin for VOUT_A and IOUT_AUNEG_IN_A36Negative power supply for VOUT_A and IOUT_AVOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                       | LDAC        | 23            |                                                                                                    |  |  |

| STNC25is low. When SYNC is high, SDO is in high-impedance status.CLR26Level Triggered clear pin (Active High). Clears all DAC channel to zero code or mid code (see DAC clear section)HARTIN_B27Input pin for HART modulation. for IOUT_BCCOMP_B28External compensation capacitor connection pin for VOUT_B . Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output amplifier at the expense of increased settling time.HARTIN_A29Input pin for HART modulation. for IOUT_ACCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the negative voltage output (channel B) load connection.VSENSEP_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)VOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                       | SDO         | 24            | Serial data output. Data are valid on the falling edge of SCLK.                                    |  |  |

| ULR26section)HARTIN_B27Input pin for HART modulation. for IOUT_BCCOMP_B28External compensation capacitor connection pin for VOUT_B. Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.HARTIN_A29Input pin for HART modulation. for IOUT_ACCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the negative voltage output (channel B) load connection.VSENSEP_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                               | SYNC        | 25            |                                                                                                    |  |  |

| CCOMP_B28External compensation capacitor connection pin for VOUT_B. Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.HARTIN_A29Input pin for HART modulation. for IOUT_ACCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEN_B32Sense output pin for the negative voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the positive voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CLR         | 26            |                                                                                                    |  |  |

| CCOMP_B28the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.HARTIN_A29Input pin for HART modulation. for IOUT_ACCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HARTIN_B    | 27            | Input pin for HART modulation. for IOUT_B                                                          |  |  |

| CCOMP_A30External compensation capacitor connection pin for VOUT_A . Addition of the external capacitor improves<br>the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEP_A32Sense output pin for the negative voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CCOMP_B     | 28            | the stability with high capacitive loads at the VOUT_B pin by reducing the bandwidth of the output |  |  |

| CCOMP_A30the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output<br>amplifier at the expense of increased settling time.VSENSEP_B31Sense output pin for the positive voltage output (channel B) load connection.VSENSEN_B32Sense output pin for the negative voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the positive voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HARTIN_A    | 29            | Input pin for HART modulation. for IOUT_A                                                          |  |  |

| VSENSEN_B32Sense output pin for the negative voltage output (channel B) load connection.VSENSEP_A33Sense output pin for the positive voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CCOMP_A     | 30            | the stability with high capacitive loads at the VOUT_A pin by reducing the bandwidth of the output |  |  |

| VSENSEP_A33Sense output pin for the positive voltage output (channel A) load connection.VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VSENSEP_B   | 31            | Sense output pin for the positive voltage output (channel B) load connection.                      |  |  |

| VSENSEN_A34Sense output pin for the negative voltage output (channel A) load connection.DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VSENSEN_B   | 32            | Sense output pin for the negative voltage output (channel B) load connection.                      |  |  |

| DAC_AGND_AB       35       Analog GND DAC Channels A and B         VNEG_IN_A       36       Negative power supply for VOUT_A and IOUT_A         IOUT_A       37       Current Output Pin (Channel A)         VPOS_IN_A       38       Positive power supply for VOUT_A and IOUT_A         VOUT_A       39       Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VSENSEP_A   | 33            | Sense output pin for the positive voltage output (channel A) load connection.                      |  |  |

| DAC_AGND_AB35Analog GND DAC Channels A and BVNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VSENSEN_A   | 34            |                                                                                                    |  |  |

| VNEG_IN_A36Negative power supply for VOUT_A and IOUT_AIOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DAC_AGND_AB | 35            | Analog GND DAC Channels A and B                                                                    |  |  |

| IOUT_A37Current Output Pin (Channel A)VPOS_IN_A38Positive power supply for VOUT_A and IOUT_AVOUT_A39Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | 36            | Negative power supply for VOUT_A and IOUT_A                                                        |  |  |

| VPOS_IN_A         38         Positive power supply for VOUT_A and IOUT_A           VOUT_A         39         Voltage Output Pin (Channel A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |               |                                                                                                    |  |  |