## CYD04S72V CYD09S72V CYD18S72V

# FLEx72<sup>™</sup> 3.3 V 64 K/128 K/256 K × 72 Synchronous Dual-Port RAM

### Features

- True dual-ported memory cells that allow simultaneous access of the same memory location

- Synchronous pipelined operation

- Family of 4 Mbit, 9 Mbit, and 18 Mbit devices

- Pipelined output mode allows fast operation

- 0.18-micron complmentary metal oxide semiconductor (CMOS) for optimum speed and power

- High-speed clock to data access

- 3.3 V low power

Active as low as 225 mA (typ)

Standby as low as 55 mA (typ)

- Mailbox function for message passing

- Global master reset

- Separate byte enables on both ports

- Commercial and industrial temperature ranges

- IEEE 1149.1-compatible joint test action group (JTAG) boundary scan

- 484-ball fine-pitch ball grid array (FBGA) (1-mm pitch)

- Pb-free packaging available

- Counter wrap around control

Internal mask register controls counter wrap-around

Counter-interrupt flags to indicate wrap-around

Memory block retransmit operation

- Counter readback on address lines

- Mask register readback on address lines

- Dual chip enables on both ports for easy depth expansion

- Seamless migration to next generation dual-port family

#### Table 1. Product Selection Guide

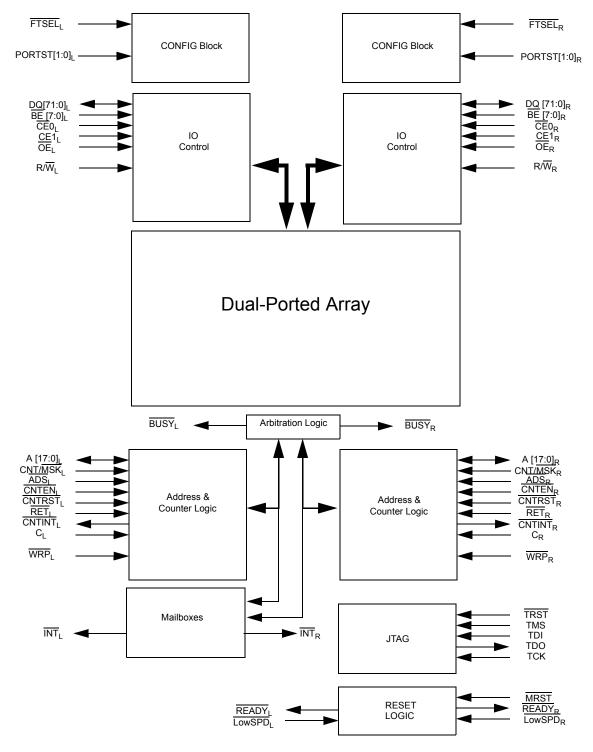

### **Functional Description**

The FLEx72 family includes 4 Mbit, 9 Mbit and 18 Mbit pipelined, synchronous, true dual-port static RAMs that are high-speed, low-power 3.3 V CMOS. Two ports are provided, permitting independent, simultaneous access to any location in memory. The result of writing to the same location by more than one port at the same time is undefined. Registers on control, address, and data lines allow for minimal set-up and hold time.

During a Read operation, data is registered for decreased cycle time. Each port contains a burst counter on the input address register. After externally loading the counter with the initial address, the counter will increment the address internally (more details to follow). The internal write pulse width is independent of the duration of the R/W input signal. The internal write pulse is self-timed to allow the shortest possible cycle times.

A HIGH on CE0 or LOW on CE1 for one clock cycle will power down the internal circuitry to reduce the static power consumption. One cycle with chip enables asserted is required to reactivate the outputs.

Additional features include: readback of burst-counter internal address value on address lines, counter-mask registers to control the counter wrap-around, counter interrupt (CNTINT) flags, readback of mask register value on address lines, retransmit functionality, interrupt flags for message passing, JTAG for boundary scan, and asynchronous Master Reset (MRST).

The CYD18S72V device have limited features. Please see Table 3 on page 8 for details.

# Seamless Migration to Next-Generation Dual-Port Family

Cypress offers a migration path for all devices to the next-generation devices in the Dual-Port family with a compatible footprint. Please contact Cypress Sales for more details

| Density                             | 4-Mbit<br>(64K x 72)           | 9-Mbit<br>(128K x 72)          | 18-Mbit<br>(256K x 72)         |

|-------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Part number                         | CYD04S72V                      | CYD09S72V                      | CYD18S72V                      |

| Max. speed (MHz)                    | 167                            | 133                            | 133                            |

| Max. access time—clock to data (ns) | 4.0                            | 4.4                            | 5.0                            |

| Typical operating current (mA)      | 225                            | 350                            | 410                            |

| Package                             | 484-ball FBGA<br>23 mm x 23 mm | 484-ball FBGA<br>23 mm x 23 mm | 484-ball FBGA<br>23 mm x 23 mm |

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised May 25, 2011

### Logic Block Diagram<sup>[1]</sup>

#### Note

1. CYD04S72V have 16 address bits, CYD09S72V have 17 address bits and CYD18S72V have 18 bits.

### Contents

| Pin Configuration                            | 4  |

|----------------------------------------------|----|

| Pin Definitions                              | 5  |

| Master Reset                                 | 7  |

| Mailbox Interrupts                           | 7  |

| Address Counter and Mask Register Operations | 8  |

| Counter Reset Operation                      | 8  |

| Counter Load Operation                       | 8  |

| Counter Increment Operation                  | 9  |

| Counter Hold Operation                       | 9  |

| Counter Interrupt                            | 9  |

| Counter Readback Operation                   | 9  |

| Retransmit                                   | 9  |

| Mask Reset Operation                         | 9  |

| Mask Load Operation                          | 9  |

| Mask Readback Operation                      | 9  |

| Counting by Two                              | 9  |

| IEEE 1149.1 Serial Boundary Scan (JTAG)      | 11 |

| Performing a TAP Reset                       | 11 |

| Performing a Pause/Restart                   | 11 |

| Boundary Scan Hierarchy for FLEx72 Family    | 11 |

| Maximum Ratings                                       | 13 |

|-------------------------------------------------------|----|

| Operating Range                                       |    |

| Electrical Characteristics Over the Operating Range . |    |

| Capacitance                                           | 14 |

| AC Test Load and Waveforms                            | 14 |

| Switching Characteristics Over the Operating Range    | 14 |

| JTAG Timing Characteristics                           | 16 |

| Switching Waveforms                                   | 16 |

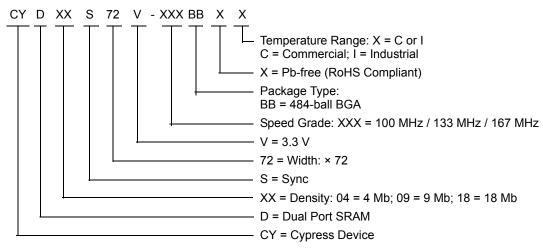

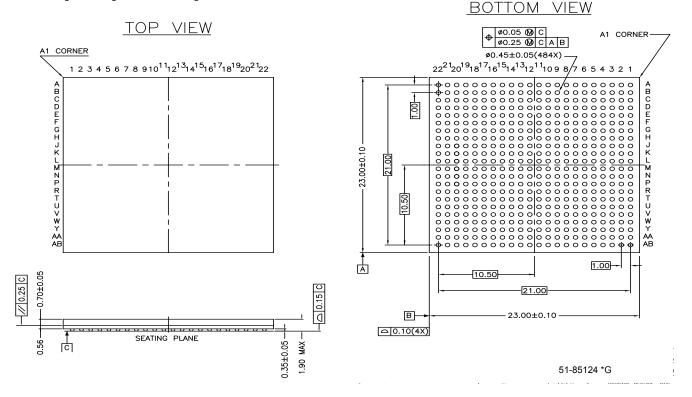

| Ordering Information                                  | 26 |

| Ordering Code Definitions                             | 26 |

| Package Diagram                                       | 27 |

| Acronyms                                              |    |

| Document Conventions                                  |    |

| Units of Measure                                      | 28 |

| Document History Page                                 |    |

| Sales, Solutions, and Legal Information               |    |

| Worldwide Sales and Design Support                    |    |

| Products                                              |    |

| PSoC Solutions                                        |    |

### **Pin Configuration**

|    | 484-ball BGA<br>Top View<br>CYD04S72V/CYD09S72V/CYD18S72V |             |                             |                     |        |                      |                      |                     |                                       |                        |                      |                      |                        |                              |            |                      |                      |                     |                      |                                      |                  |               |

|----|-----------------------------------------------------------|-------------|-----------------------------|---------------------|--------|----------------------|----------------------|---------------------|---------------------------------------|------------------------|----------------------|----------------------|------------------------|------------------------------|------------|----------------------|----------------------|---------------------|----------------------|--------------------------------------|------------------|---------------|

|    | 1                                                         | 2           | 3                           | 4                   | 5      | 6                    | 7                    | 8                   | 9                                     | 10                     | 11                   | 12                   | 13                     | 14                           | 15         | 16                   | 17                   | 18                  | 19                   | 20                                   | 21               | 22            |

| Α  | NC                                                        | DQ61L       | DQ59L                       | DQ57L               | DQ54L  | DQ51L                | DQ48L                | DQ45L               | DQ42L                                 | DQ39L                  | DQ36L                | DQ36R                | DQ39R                  | DQ42R                        | DQ45R      | DQ48R                | DQ51R                | DQ54R               | DQ57R                | DQ59R                                | DQ61R            | NC            |

| в  | DQ63L                                                     | DQ62L       | DQ60L                       | DQ58L               | DQ55L  | DQ52L                | DQ49L                | DQ46L               | DQ43L                                 | DQ40L                  | DQ37L                | DQ37R                | DQ40R                  | DQ43R                        | DQ46R      | DQ49R                | DQ52R                | DQ55R               | DQ58R                | DQ60R                                | DQ62R            | DQ63R         |

| с  | DQ65L                                                     | DQ64L       | VSS                         | VSS                 | DQ56L  | DQ53L                | DQ50L                | DQ47L               | DQ44L                                 | DQ41L                  | DQ38L                | DQ38R                | DQ41R                  | DQ44R                        | DQ47R      | DQ50R                | DQ53R                | DQ56R               | VSS                  | VSS                                  | DQ64R            | DQ65R         |

| D  | DQ67L                                                     | DQ66L       | VSS                         | VSS                 | VSS    | NC <sup>[2, 5]</sup> | NC <sup>[2, 5]</sup> | VSS                 | L <u>O</u> WSP<br>DL <sup>[2,4]</sup> | PORTS<br>TD0L<br>[2,4] | NC <sup>[2, 5]</sup> | BUSYL<br>[2, 5]      | CNTINT<br>L<br>[10]    | PORTS<br>TD1L<br>[2, 4]      | NC         | NC <sup>[2, 5]</sup> | NC <sup>[2, 5]</sup> | VSS                 | VSS                  | VSS                                  | DQ66R            | DQ67R         |

| Е  | DQ69L                                                     | DQ68L       | VDDIOL                      | VSS                 | VSS    | VDDIOL               | VDDIO<br>L           | VDDIO<br>L          | VDDIOL                                | VDDIOL                 | VTTL                 | VTTL                 | VTTL                   | VDDIO<br>R                   | VDDIO<br>R | VDDIO<br>R           | VDDIOR               | NC                  | VSS                  | VDDIOR                               | DQ68R            | DQ69R         |

| F  | DQ71L                                                     | DQ70L       | CE1L <sup>[8]</sup>         | CE0L <sup>[9]</sup> | VDDIOL | VDDIOL               | VDDIO<br>L           | VDDIO<br>L          | VDDIOL                                | VCORE                  | VCORE                | VCORE                | VCORE                  | VDDIO<br>R                   | VDDIO<br>R | VDDIO<br>R           | VDDIOR               | VDDIOR              | CE0R <sup>[9]</sup>  | CE1R <sup>[8]</sup>                  | DQ70R            | DQ71R         |

| G  | A0L                                                       | A1L         | RETL <sup>[2,3]</sup>       | BE4L                | VDDIOL | VDDIOL               | VREFL<br>[2, 4]      | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VREFR<br>[2, 4]      | VDDIOR               | VDDIOR              | BE4R                 | RETR <sup>[2,3</sup>                 | <sup>3</sup> A1R | A0R           |

| н  | A2L                                                       | A3L         | $WRP_{3]}^{[2,}$            | BE5L                | VDDIOL | VDDIOL               | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VDDIOR               | VDDIOR              | BE5R                 | $WRP_{3]}R^{[2]}$                    | A3R              | A2R           |

| J  | A4L                                                       | A5L         | READYL<br>[2, 5]            | BE6L                | VDDIOL | VDDIOL               | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VDDIOR               | VDDIOR              | BE6R                 | READYR<br>[2, 5]                     | A5R              | A4R           |

| к  | A6L                                                       | A7L         | NC <sup>[2,5]</sup>         | BE7L                | VTTL   | VCORE                | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VCORE                | VDDIOR              | BE7R                 | NC <sup>[2,5]</sup>                  | A7R              | A6R           |

| L  | A8L                                                       | A9L         | CL                          | OEL                 | VTTL   | VCORE                | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VCORE                | VTTL                | OER                  | CR                                   | A9R              | A8R           |

| м  | A10L                                                      | A11L        | VSS                         | BE3L                | VTTL   | VCORE                | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VCORE                | VTTL                | BE3R                 | VSS                                  | A11R             | A10R          |

| N  | A12L                                                      | A13L        | ADSL <sup>[9]</sup>         | BE2L                | VDDIOL | VCORE                | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VCORE                | VTTL                | BE2R                 | ADSR <sup>[9]</sup>                  | A13R             | A12R          |

| Р  | A14L                                                      | A15L        | CNT/MS<br>KL <sup>[8]</sup> | BE1L                | VDDIOL | VDDIOL               | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VDDIOR               | VDDIOR              | BE1R                 | C <u>N</u> T/MS<br>KR <sup>[8]</sup> | A15R             | A14R          |

| R  | A16L<br>[6]                                               | A17L<br>[7] | CNTENL                      | BE0L                | VDDIOL | VDDIOL               | VSS                  | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VSS                  | VDDIOR               | VDDIOR              | BE0R                 |                                      | A17R             | A16R<br>[6]   |

| т  | A18L<br>[2,5]                                             | NC          | CNTRST                      | INTL                | VDDIOL | VDDIOL               | VREFL<br>[2, 4]      | VSS                 | VSS                                   | VSS                    | VSS                  | VSS                  | VSS                    | VSS                          | VSS        | VREFR<br>[2, 4]      | VDDIOR               | VDDIOR              | INTR                 | CNTRST<br>R <sup>[8]</sup>           | NC               | A18R<br>[2,5] |

| U  | DQ35L                                                     | DQ34L       | R/WL                        | REYL<br>(2,4)       | VDDIOL | VDDIOL               | VDDIO<br>L           | VDDIO<br>L          | VDDIOL                                | VCORE                  | VCORE                | VCORE                | VCORE                  | VDDIO<br>R                   | VDDIO<br>R | VDDIO<br>R           | VDDIOR               | VDDIOR              | REVR <sup>[2,4</sup> | R/WR                                 | DQ34R            | DQ35R         |

| v  | DQ33L                                                     | DQ32L       | FTSELL                      | VDDIOL              | NC     | VDDIOL               |                      | VDDIO               | VDDIOL                                | VTTL                   | VTTL                 | VTTL                 | VDDIO<br>R             | VDDIO<br>R                   | VDDIO<br>R | VDDIO<br>R           | VDDIOR               | TRST <sup>[2,</sup> | VDDIOR               | FTSELR                               | DQ32R            | DQ33R         |

| w  | DQ31L                                                     | DQ30L       | VSS                         | MRST                | VSS    | NC <sup>[2, 5]</sup> | NC <sup>[2, 5]</sup> | REVL <sup>[2,</sup> | PORTS<br>TD1R<br>[2, 4]               | CNTINT<br>R<br>[10]    | BUSY<br>[2, 5]       | NC <sup>[2, 5]</sup> | PORTS<br>TD0R<br>[2,4] | LOWSP<br>DR <sup>[2,4]</sup> | VSS        | NC <sup>[2, 5]</sup> | NC <sup>[2, 5]</sup> | VSS                 | TDI                  | TDO                                  | DQ30R            | DQ31R         |

| Y  | DQ29L                                                     | DQ28L       | VSS                         | VSS                 | DQ20L  | DQ17L                | DQ14L                | DQ11L               | DQ8L                                  | DQ5L                   | DQ2L                 | DQ2R                 | DQ5R                   | DQ8R                         | DQ11R      | DQ14R                | DQ17R                | DQ20R               | TMS                  | тск                                  | DQ28R            | DQ29R         |

| AA | DQ27L                                                     | DQ26L       | DQ24L                       | DQ22L               | DQ19L  | DQ16L                | DQ13L                | DQ10L               | DQ7L                                  | DQ4L                   | DQ1L                 | DQ1R                 | DQ4R                   | DQ7R                         | DQ10R      | DQ13R                | DQ16R                | DQ19R               | DQ22R                | DQ24R                                | DQ26R            | DQ27R         |

| АВ | NC                                                        | DQ25L       | DQ23L                       | DQ21L               | DQ18L  | DQ15L                | DQ12L                | DQ9L                | DQ6L                                  | DQ3L                   | DQ0L                 | DQ0R                 | DQ3R                   | DQ6R                         | DQ9R       | DQ12R                | DQ15R                | DQ18R               | DQ21R                | DQ23R                                | DQ25R            | NC            |

#### Notes

2. This ball will represent a next generation Dual-Port feature. For more information about this feature, contact Cypress Sales.

3. Connect this ball to VDDIO. For more information about this next generation Dual-Port feature contact Cypress Sales.

Connect this ball to VSS. For more information about this next generation Dual-Port feature, contact Cypress Sales. 4.

5. Leave this ball unconnected. For more information about this feature, contact Cypress Sales.

Leave this ball unconnected for a 64K x 72 configuration.

Leave this ball unconnected for a 64K x 72 configuration.

Leave this ball unconnected for CYD18S72V device. They need to be tied to VDDIO.

These balls are not applicable for CYD18S72V device. They need to be tied to VSS.

These balls are not applicable for CYD18S72V device. They need to be no connected.

### **Pin Definitions**

| Left Port                                   | Right Port                                  | Description                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0L</sub> -A <sub>17L</sub>           | A <sub>0R</sub> -A <sub>17R</sub>           | Address inputs.                                                                                                                                                                                                                                                                                                                                            |

| BE <sub>0L</sub> –BE <sub>7L</sub>          | BE <sub>0R</sub> –BE <sub>7R</sub>          | Byte enable inputs. Asserting these signals enables Read and Write operations to the corresponding bytes of the memory array.                                                                                                                                                                                                                              |

| BUSY <sub>L</sub> <sup>[11,12]</sup>        | BUSY <sub>R</sub> <sup>[11,12]</sup>        | <b>Port busy output</b> . When the collision is detected, a <b>BUSY</b> is asserted.                                                                                                                                                                                                                                                                       |

| CL                                          | C <sub>R</sub>                              | Input clock signal.                                                                                                                                                                                                                                                                                                                                        |

| CE0 <sub>L</sub> <sup>[13]</sup>            | CE0 <sub>R</sub> <sup>[13]</sup>            | Active low chip enable input.                                                                                                                                                                                                                                                                                                                              |

| CE1 <sub>L</sub> <sup>[14]</sup>            | CE1 <sub>R</sub> <sup>[14]</sup>            | Active high chip enable input.                                                                                                                                                                                                                                                                                                                             |

| DQ <sub>0L</sub> –DQ <sub>71L</sub>         | DQ <sub>0R</sub> -DQ <sub>71R</sub>         | Data bus input/output.                                                                                                                                                                                                                                                                                                                                     |

| OEL                                         | OE <sub>R</sub>                             | <b>Output enable input</b> . This asynchronous signal must be asserted LOW to enable the DQ data pins during Read operations.                                                                                                                                                                                                                              |

| INTL                                        | INT <sub>R</sub>                            | <b>Mailbox interrupt flag output</b> . The mailbox permits communications between ports. The upper two memory locations can be used for message passing. $INT_L$ is asserted LOW when the right port writes to the mailbox location of the left port, and vice versa. An interrupt to a port is deasserted HIGH when it reads the contents of its mailbox. |

| LowSPD <sub>L</sub> <sup>[11,15]</sup>      | LowSPD <sub>R</sub> <sup>[11,15]</sup>      | <b>Port low speed select input</b> . When operating at less than 100 MHz, the LowSPD disables the port DLL.                                                                                                                                                                                                                                                |

| PORTSTD[1:0] <sub>L</sub> <sup>[11,15</sup> | PORTSTD[1:0] <sub>R</sub> <sup>[11,15</sup> | Port address/control/data i/o standard select input.                                                                                                                                                                                                                                                                                                       |

| $R/\overline{W}_L$                          | R/W <sub>R</sub>                            | <b>Read/write enable input</b> . Assert this pin LOW to write to, or HIGH to Read from the dual-port memory array.                                                                                                                                                                                                                                         |

| READY <sub>L</sub> <sup>[11,12]</sup>       | READY <sub>R</sub> <sup>[11,12]</sup>       | <b>Port ready output</b> . This signal will be asserted when a port is ready for normal operation.                                                                                                                                                                                                                                                         |

| CNT/MSKL <sup>[14]</sup>                    | CNT/MSK <sub>R</sub> <sup>[14]</sup>        | Port counter/mask select input. Counter control input.                                                                                                                                                                                                                                                                                                     |

| ADS <sub>L</sub> <sup>[13]</sup>            | ADS <sub>R</sub> <sup>[13]</sup>            | Port counter address load strobe input. Counter control input.                                                                                                                                                                                                                                                                                             |

| CNTEN <sub>L</sub> <sup>[13]</sup>          | CNTEN <sub>R</sub> <sup>[13]</sup>          | Port counter enable input. Counter control input.                                                                                                                                                                                                                                                                                                          |

| CNTRST <sub>L</sub> <sup>[14]</sup>         | CNTRST <sub>R</sub> <sup>[14]</sup>         | Port counter reset input. Counter control input.                                                                                                                                                                                                                                                                                                           |

| CNTINT <sub>L</sub> <sup>[16]</sup>         | CNTINT <sub>R</sub> <sup>[16]</sup>         | <b>Port counter interrupt output</b> . This pin is asserted LOW when the unmasked portion of the counter is incremented to all "1s".                                                                                                                                                                                                                       |

| WRP <sub>L</sub> <sup>[11,17]</sup>         | WRP <sub>R</sub> <sup>[11,17]</sup>         | <b>Port counter wrap input</b> . After the burst counter reaches the maximum count, if $\overline{\text{WRP}}$ is low, the unmasked counter bits will be set to 0. If high, the counter will be loaded with the value stored in the mirror register.                                                                                                       |

| RET <sub>L</sub> <sup>[11,17]</sup>         | RET <sub>R</sub> <sup>[12,17]</sup>         | Port counter retransmit input. Counter control input.                                                                                                                                                                                                                                                                                                      |

| FTSEL <sub>L</sub> <sup>[11,17]</sup>       | FTSEL <sub>R</sub> <sup>[11,17]</sup>       | <b>Flow-through select</b> . Use this pin to select Flow-Through mode. When is de-asserted, the device is in pipelined mode.                                                                                                                                                                                                                               |

| VREF <sub>L</sub> <sup>[11,15]</sup>        | VREF <sub>R</sub> <sup>[11,15]</sup>        | Port external high-speed io reference input.                                                                                                                                                                                                                                                                                                               |

#### Notes

Notes

11. This ball will represent a next generation Dual-Port feature. For more information about this feature, contact Cypress Sales.

12. Leave this ball unconnected. For more information about this feature, contact Cypress Sales.

13. These balls are not applicable for CYD18S72V device. They need to be tied to VSS.

14. These balls are not applicable for CYD18S72V device. They need to be tied to VDDIO.

15. Connect this ball to VSS. For more information about this next generation Dual-Port feature, contact Cypress Sales.

16. These balls are not applicable for CYD18S72V device. They need to be no connected.

17. Connect this ball to VDD. For more information about this next generation Dual-Port feature, contact Cypress Sales.

17. Connect this ball to VDDIO. For more information about this next generation Dual-Port feature contact Cypress Sales

### Pin Definitions (continued)

| Left Port                | Right Port                          | Description                                                                                                                                                             |  |  |  |

|--------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VDDIO <sub>L</sub>       | VDDIO <sub>R</sub>                  | Port IO power supply.                                                                                                                                                   |  |  |  |

| REV <sup>[18,19]</sup> L | REV <sup>[18,19]</sup> <sub>R</sub> | Reserved pins for future features.                                                                                                                                      |  |  |  |

| MR                       | RST                                 | <b>Master reset input</b> . MRST is an asynchronous input signal and affects both ports. A master reset operation is required at power-up.                              |  |  |  |

| TRST                     | -[18,20]                            | JTAG reset input.                                                                                                                                                       |  |  |  |

| TN                       | MS                                  | <b>JTAG test mode select input</b> . It controls the advance of JTAG TAP state machine. State machine transitions occur on the rising edge of TCK.                      |  |  |  |

| TI                       | DI                                  | <b>JTAG test data input</b> . Data on the TDI input will be shifted serially into selected registers.                                                                   |  |  |  |

| тс                       | СК                                  | JTAG test clock input.                                                                                                                                                  |  |  |  |

| ТС                       | 00                                  | <b>JTAG test data output</b> . TDO transitions occur on the falling edge of TCK. TDO is normally three-stated except when captured data is shifted out of the JTAG TAP. |  |  |  |

| V                        | SS                                  | Ground inputs.                                                                                                                                                          |  |  |  |

| V <sub>COF</sub>         | RE <sup>[21]</sup>                  | Core power supply.                                                                                                                                                      |  |  |  |

| V <sub>T</sub>           |                                     | LVTTL power supply.                                                                                                                                                     |  |  |  |

Notes

- 18. This ball will represent a next generation Dual-Port feature. For more information about this feature, contact Cypress Sales.

- 19. Connect this ball to VSS. For more information about this next generation Dual-Port feature, contact Cypress Sales

20. Leave this ball unconnected. For more information about this feature, contact Cypress Sales. 21. This family of Dual-Ports does not use V<sub>CORE</sub>, and these pins are internally NC. The next generation Dual-Port family, the FLEx72-E<sup>™</sup>, will use V<sub>CORE</sub> of 1.5 V or 1.8 V. Please contact local Cypress FAE for more information

Page 6 of 30

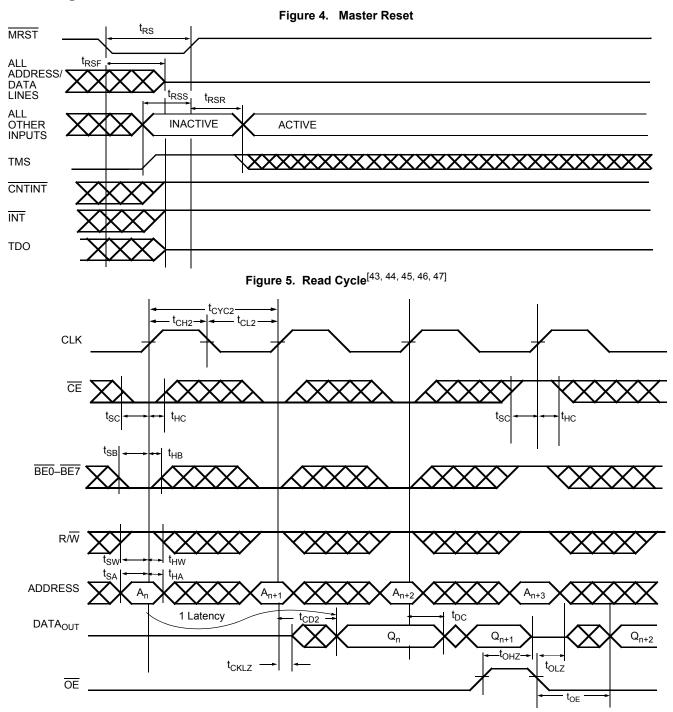

#### Master Reset

The FLEx72 family devices undergo a complete reset by taking the MRST input LOW. MRST input can switch asynchronously to the clocks. MRST initializes the internal burst counters to zero, and the counter mask registers to all ones (completely unmasked). MRST also forces the mailbox interrupt (INT) flags and the Counter Interrupt (CNTINT) flags HIGH. MRST must be performed on the FLEx72 family devices after power-up.

#### Mailbox Interrupts

The upper two memory locations may be used for message passing and permit communications between ports. Table 2 shows the interrupt operation for both ports using 18 Mbit device as an example. The highest memory location, 3FFFF is the mailbox for the right port and 3FFFE is the mailbox for the left port. Table 2.shows that in order to set the  $INT_R$  flag, a write

Table 2. Interrupt Operation Example <sup>[22, 23, 24, 25]</sup>

operation by the left port to address 3FFFF will assert  $\overline{INT}_R$  LOW. At least one byte has to be active for a write to generate an interrupt. A valid Read of the 3FFFF location by the right port will reset INT<sub>R</sub> HIGH. At least one byte has to be active in order for a read to reset the interrupt. When one port writes to the other port's mailbox, the INT of the port that the mailbox belongs to is asserted LOW.

The INT is reset when the owner (port) of the mailbox reads the contents of the mailbox. The interrupt flag is set in a flow-thru mode (i.e., it follows the clock edge of the writing port). Also, the flag is reset in a flow-thru mode (i.e., it follows the clock edge of the reading port)

Each port can read the other port's mailbox without resetting the interrupt. And each port can write to its own mailbox without setting the interrupt. If an application does not require message passing, INT pins should be left open.

| Function                          |     | Left | Port                |   |                  | Righ | t Port              |                  |

|-----------------------------------|-----|------|---------------------|---|------------------|------|---------------------|------------------|

| Function                          | R/W | CEL  | A <sub>0L-17L</sub> |   | R/W <sub>R</sub> | CER  | A <sub>0R-17R</sub> | INT <sub>R</sub> |

| Set Right INT <sub>R</sub> Flag   | L   | L    | 3FFFF               | Х | Х                | Х    | Х                   | L                |

| Reset Right INT <sub>R</sub> Flag | Х   | Х    | Х                   | Х | Н                | L    | 3FFFF               | Н                |

| Set Left INT <sub>L</sub> Flag    | Х   | Х    | Х                   | L | L                | L    | 3FFFE               | Х                |

| Reset Left INT <sub>L</sub> Flag  | Н   | L    | 3FFFE               | Н | Х                | Х    | Х                   | Х                |

Notes

22. <u>CYD04S72V</u> have 16 <u>address bits</u>, <u>CYD09S72V</u> have 17 address bits and CYD18S72V have 18 bits.

23. <u>CE</u> is internal signal. <u>CE</u> = LOW if <u>CE</u> = LOW and <u>CE</u> = HIGH. For a single Read operation, <u>CE</u> only needs to be asserted once at the rising edge of the CLK and <u>can</u> be deasserted after that. Data will be out after the following CLK edge and will be three-stated after the next CLK edge.

24. OE is "Don't Care" for mailbox operation.

25. At least one of BE0 or BE7 must be LOW.

| CLK | MRST | CNT/MSK | CNTRST | ADS | CNTEN | Operation         | Description                                                            |

|-----|------|---------|--------|-----|-------|-------------------|------------------------------------------------------------------------|

| Х   | L    | Х       | Х      | Х   | х     | Master Reset      | Reset address counter to all 0s and mask register to all 1s            |

|     | Н    | Н       | L      | Х   | Х     | Counter Reset     | Reset counter unmasked portion to all 0s                               |

|     | н    | Н       | Н      | L   | L     | Counter Load      | Load counter with external address value presented<br>on address lines |

|     | Н    | Н       | Н      | L   | Н     | Counter Readback  | Read out counter internal value on address lines                       |

|     | Н    | Н       | Н      | Н   | L     | Counter Increment | Internally increment address counter value                             |

|     | Н    | Н       | Н      | Н   | Н     | Counter Hold      | Constantly hold the address value for multiple clock cycles            |

|     | Н    | L       | L      | Х   | Х     | Mask Reset        | Reset mask register to all 1s                                          |

|     | Н    | L       | Н      | L   | L     | Mask Load         | Load mask register with value presented on the address lines           |

|     | Н    | L       | Н      | L   | Н     | Mask Readback     | Read out mask register value on address lines                          |

|     | Н    | L       | Н      | Н   | Х     | Reserved          | Operation undefined                                                    |

#### Table 3. Address Counter and Counter Mask Register Control Operation (Any Port) [26,27]

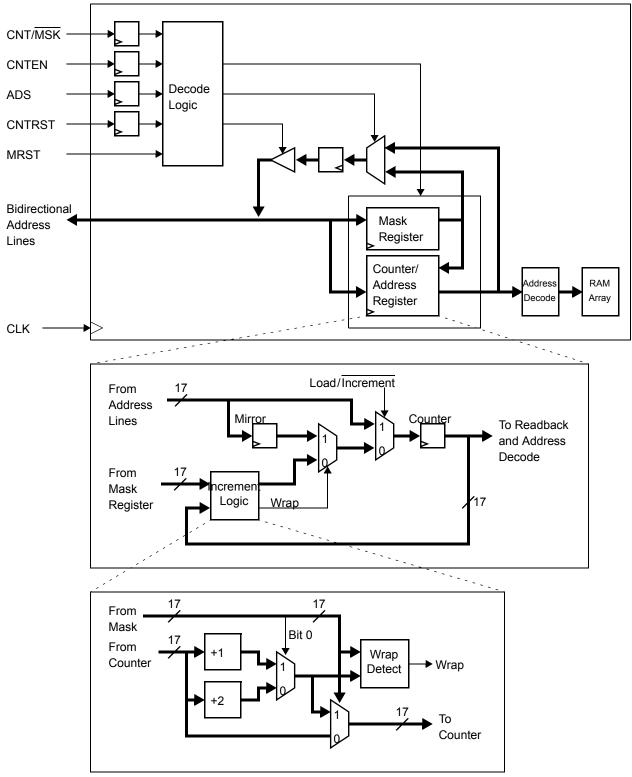

#### Address Counter and Mask Register Operations<sup>[28]</sup>

This section describes the features only apply to 4 Mbit and 9 Mbit devices, not to 18 Mbit device. Each port has a programmable burst address counter. The burst counter contains three registers: a counter register, a mask register, and a mirror register.

The **counter register** contains the address used to access the RAM array. It is changed only by the <u>Counter Load</u>, Increment, Counter Reset, and by master reset (MRST) operations.

The **mask register** value affects the Increment and Counter Reset operations by preventing the corresponding bits of the counter register <u>from</u> changing. It also affects the counter interrupt output (CNTINT). The mask register is changed <u>only</u> by the Mask Load and Mask Reset operations, and by the MRST. The mask register defines the counting range of the counter register. It divides the counter register into two regions: zero or more "0s" in the most significant bits define the masked region, one or more "1s" in the least significant bits define the unmasked region. Bit 0 may also be "0," masking the least significant counter bit and causing the counter to increment by two instead of one.

The mirror register is used to reload the counter register on increment operations (see "retransmit," below). It always contains the value last loaded into the counter register, and is changed only by the <u>Counter Load</u>, and Counter Reset operations, and by the MRST.

Table 3 summarizes the operation of <u>these</u> registers and the required input control signals. The <u>MRST</u> control signal is asynchronous. <u>All the other control</u> signals in <u>Table 3</u> (CNT/MSK, <u>CNTRST</u>, <u>ADS</u>, <u>CNTEN</u>) are synchronized to the port's CLK. All these counter and mask operations are independent of the port's chip enable inputs (CE0 and CE1).

Counter enable (CNTEN) inputs are provided to stall the operation of the address input and utilize the internal address generated by the internal counter for fast, interleaved memory applications. A port's burst counter is loaded when the port's address strobe (ADS) and CNTEN signals are LOW. When the port's CNTEN is asserted and the ADS is deasserted, the address counter will increment on each LOW to HIGH transition of that port's clock signal. This will Read/Write one word from/into each successive address the entire memory array, and will loop back to the start. Counter reset (CNTRST) is used to reset the unmasked portion of the burst counter to 0s. A counter-mask register is used to control the counter wrap.

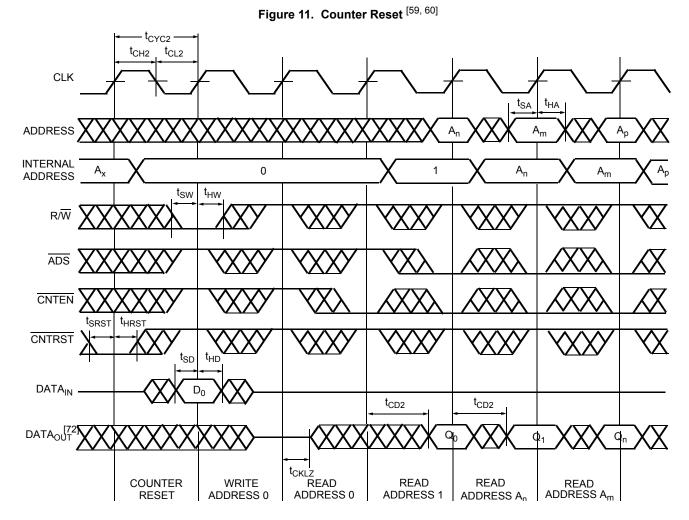

#### **Counter Reset Operation**

All unmasked bits of the counter and mirror registers are reset to "0." All masked bits remain unchanged. A Mask Reset followed by a Counter Reset will reset the counter and mirror registers to 00000, as will master reset (MRST).

#### **Counter Load Operation**

The address counter and mirror registers are both loaded with the address value presented at the address lines.

#### Notes

26. X" = "Don't Care," "H" = HIGH, "L" = LOW.

<sup>27.</sup> Counter operation and mask register operation is independent of chip enables.

<sup>28.</sup> The CYD04S72V has 16 address bits and a maximum address value of FFFF. The CYD09S72V has 17 address bits and a maximum address value of 1FFFF. The CYD18S72V has 18 address bits and a maximum address value of 3FFFF.

#### **Counter Increment Operation**

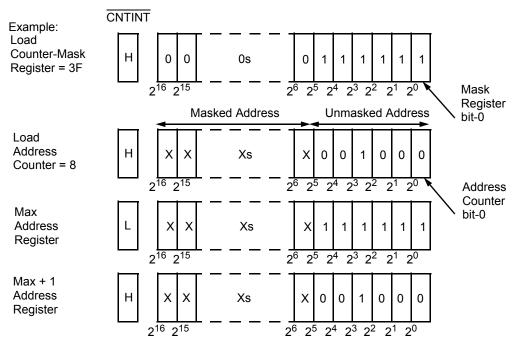

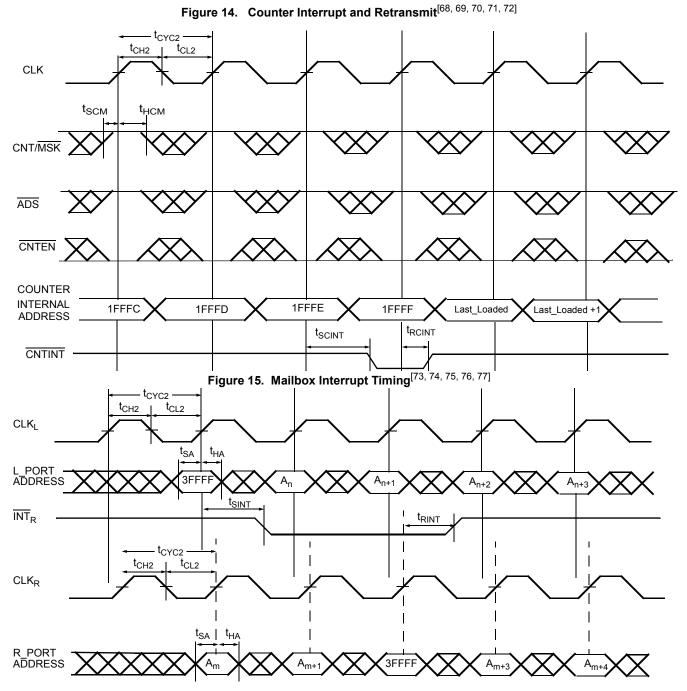

Once the address counter register is initially loaded with an external address, the counter can internally increment the address value, potentially addressing the entire memory array. Only the unmasked bits of the counter register are incremented. The corresponding bit in the mask register must be a "1" for a counter bit to change. The counter register is incremented by 1 if the least significant bit is unmasked, and by 2 if it is masked. If all unmasked bits are "1," the next increment will wrap the counter back to the initially loaded value. If an Increment results in all the unmasked bits of the counter being "1s," a counter interrupt flag (CNTINT) is asserted. The next Increment will return the counter register to its initial value, which was stored in the mirror register. The counter address can instead be forced to loop to 00000 by externally connecting CNTINT to CNTRST.<sup>[29]</sup> An increment that results in one or more of the unmasked bits of the counter being "0" will de-assert the counter interrupt flag. The example in Figure 2 shows the counter mask register loaded with a mask value of 0003Fh unmasking the first 6 bits with bit "0" as the LSB and bit "16" as the MSB. The maximum value the mask register can be loaded with is 1FFFFh. Setting the mask register to this value allows the counter to access the entire memory space. The address counter is then loaded with an initial value of 8h. The base address bits (in this case, the 6th address through the 16th address) are loaded with an address value but do not increment once the counter is configured for increment operation. The counter address will start at address 8h. The counter will increment its internal address value till it reaches the mask register value of 3Fh. The counter wraps around the memory block to location 8h at the next count. CNTINT is issued when the counter reaches its maximum value.

#### **Counter Hold Operation**

The value of all three registers can be constantly maintained unchanged for an unlimited number of clock cycles. Such operation is useful in applications where wait states are needed, or when address is available a few cycles ahead of data in a shared bus interface.

#### **Counter Interrupt**

The counter interrupt (CNTINT) is asserted LOW when an increment operation results in the unmasked portion of the counter register being all "1s." It is deasserted HIGH when an Increment operation results in any other value. It is also de-asserted by Counter Reset, <u>Counter Load</u>, Mask Reset and Mask Load operations, and by MRST.

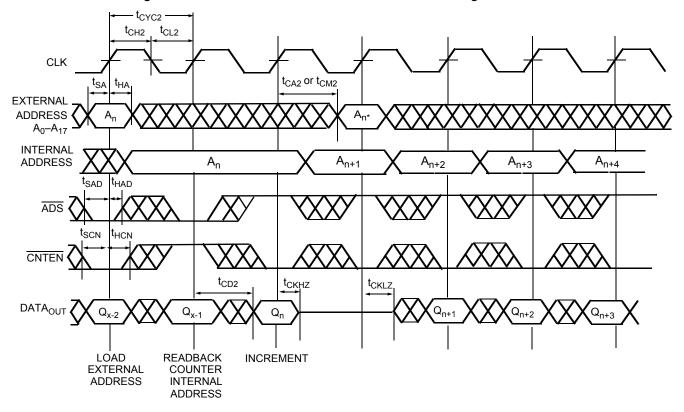

#### **Counter Readback Operation**

The internal value of the counter register can be read out on the address lines. Readback is pipelined; the address will be valid  $t_{CA2}$  after the next rising edge of the port's clock. If address readback occurs while the port is enabled (CE0 LOW and CE1 HIGH), the data lines (DQs) will be three-stated. *Figure 1* shows a block diagram of the operation.

#### Retransmit

Note

Retransmit is a feature that allows the Read of a block of memory more than once without the need to reload the initial address.

This eliminates the need for external logic to store and route data. It also reduces the complexity of the system design and saves board space. An internal "mirror register" is used to store the initially loaded address counter value. When the counter unmasked portion reaches its maximum value set by the mask register, it wraps back to the initial value stored in this "mirror register." If the counter is continuously configured in increment mode, it increments again to its maximum value and wraps back to the value initially stored into the "mirror register." Thus, the repeated access of the same data is allowed without the need for any external logic.

#### **Mask Reset Operation**

The mask register is reset to all "1s," which unmasks every bit of the counter. Master reset (MRST) also resets the mask register to all "1s."

#### Mask Load Operation

The mask register is loaded with the address value presented at the address lines. Not all values permit correct increment operations. Permitted values are of the form  $2^n$ -1 or  $2^n$ -2. From the most significant bit to the least significant bit, permitted values have zero or more "0s," one or more "1s," or one "0." Thus 1FFFF, 003FE, and 00001 are permitted values, but 1F0FF, 003FC, and 00000 are not.

#### Mask Readback Operation

The internal value of the mask register can be read out on the address lines. Readback is pipelined; the address will be valid  $t_{CM2}$  after the next rising edge of the port's clock. If mask readback occurs while the port is enabled (CE0 LOW and CE1 HIGH), the data lines (DQs) will be three-stated. *Figure 1* shows a block diagram of the operation.

#### **Counting by Two**

When the least significant bit of the mask register is "0," the counter increments by two. This may be used to connect the x72 devices as a 144-bit single port SRAM in which the counter of one port counts even addresses and the counter of the other port counts odd addresses. This even-odd address scheme stores one half of the 144-bit data in even memory locations, and the other half in odd memory locations.

<sup>29.</sup> CNTINT and CNTRST specs are guaranteed by design to operate properly at speed grade operating frequency when tied together.

Figure 1. Counter, Mask, and Mirror Logic Block Diagram<sup>[30]</sup>

#### Note

30. CYD04S72V have 16 address bits, CYD09S72V have 17 address bits and CYD18S72V have 18 bits.

### IEEE 1149.1 Serial Boundary Scan (JTAG)<sup>[33]</sup>

The FLEx72 incorporates an IEEE 1149.1 serial boundary scan test access port (TAP). The TAP controller functions in a manner that does not conflict with the operation of other devices using 1149.1-compliant TAPs. The TAP operates using JEDEC-standard 3.3 V I/O logic levels. It is composed of three input connections and one output connection required by the test logic defined by the standard.

#### Performing a TAP Reset

A reset is performed by forcing TMS HIGH ( $V_{DD}$ ) for five rising edges of TCK. This reset does not affect the operation of the FLEx72 family and may be performed while the device is operating. An MRST must be performed on the FLEx72 after power-up.

#### Performing a Pause/Restart

When a SHIFT-DR PAUSE-DR SHIFT-DR is performed the scan chain will output the next bit in the chain twice. For example, if the value expected from the chain is 1010101, the device will output a 11010101. This extra bit will cause some testers to report an erroneous failure for the FLEx72 in a scan test. Therefore the tester should be configured to never enter the PAUSE-DR state.

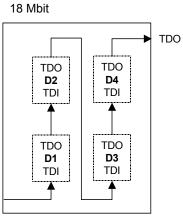

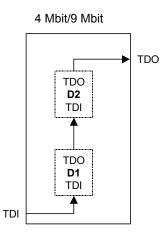

#### Boundary Scan Hierarchy for FLEx72 Family

Internally, the CYD04S72V and CYD09S72V have two DIEs while CYD18S72V has four DIEs. Each DIE contains all the circuitry required to support boundary scan testing. The circuitry includes the TAP, TAP controller, instruction register, and data **Notes**

31. CYD04S72V have 16 address bits, CYD09S72V have 17 address bits and CYD18S72V have 18 bits.

32. The "X" in this diagram represents the counter upper bits.

33. Boundary scan is IEEE 1149.1-compatible. See "Performing a Pause/Restart" for deviation from strict 1149.1 compliance.

registers. The circuity and operation of the DIE boundary scan are described in detail below. The scan chain of each DIE is connected serially to form the scan chain of the FLEx72 family as shown in Figure 3. TMS and TCK are connected in parallel to each DIE to drive all 4 TAP controllers in unison. In many cases, each DIE will be supplied with the same instruction. In other cases, it might be useful to supply different instructions to each DIE. One example would be testing the device ID of one DIE while bypassing the others.

Each pin of FLEx72 family is typically connected to multiple DIEs. For connectivity testing with the EXTEST instruction, it is desirable to check the internal connections between DIEs as well as the external connections to the package. This can be accomplished by merging the netlist of the devices with the netlist of the user's circuit board. To facilitate boundary scan testing of the devices, Cypress provides the BSDL file for each DIE, the internal netlist of the device, and a description of the device scan chain. The user can use these materials to easily integrate the devices into the board's boundary scan environment. Further information can be found in the Cypress application note Using JTAG Boundary Scan with the FLEx18/72<sup>TM</sup> Dual-Port SRAMs.

# CYD04S72V CYD09S72V CYD18S72V

Figure 3. Scan Chain

#### Table 4. Identification Register Definitions

| Instruction Field        | Value | Description                                                 |

|--------------------------|-------|-------------------------------------------------------------|

| Revision number(31:28)   | 0h    | Reserved for version number                                 |

| Cypress device(27:12)    | C002h | Defines Cypress DIE number for CYD18S72V and CYD09S72V      |

|                          | C001h | Defines Cypress DIE number for CYD04S72V                    |

| Cypress JDEC ID(11:1)    | 034h  | Allows unique identification of FLEx72 family device vendor |

| ID register presence (0) | 1     | Indicates the presence of an ID register                    |

#### Table 5. Scan Registers Sizes

TDI

| Register Name  | Bit Size          |

|----------------|-------------------|

| Instruction    | 4                 |

| Bypass         | 1                 |

| Identification | 32                |

| Boundary scan  | n <sup>[34]</sup> |

#### Table 6. Instruction Identification Codes

| Instruction    | Code            | Description                                                                        |

|----------------|-----------------|------------------------------------------------------------------------------------|

| EXTEST         | 0000            | Captures the Input/Output ring contents. Places the BSR between the TDI and TDO    |

| BYPASS         | 1111            | Places the BYR between TDI and TDO                                                 |

| IDCODE         | 1011            | Loads the IDR with the vendor ID code and places the register between TDI and TDO  |

| HIGHZ          | 0111            | Places BYR between TDI and TDO. Forces all FLEx72 output drivers to a High-Z state |

| CLAMP          | 0100            | Controls boundary to 1/0. Places BYR between TDI and TDO                           |

| SAMPLE/PRELOAD | 1000            | Captures the input/output ring contents. Places BSR between TDI and TDO            |

| NBSRST         | 1100            | Resets the non-boundary scan logic. Places BYR between TDI and TDO                 |

| RESERVED       | All other codes | Other combinations are reserved. Do not use other than the above                   |

### Maximum Ratings<sup>[35]</sup>

(Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested)

| Storage temperature65 °C to + 150 °C                                 |

|----------------------------------------------------------------------|

| Ambient temperature with power applied                               |

| Supply voltage to ground potential–0.5 V to + 4.6 V                  |

| DC Voltage Applied to Outputs in High-Z state                        |

| DC input voltage $-0.5$ V to V <sub>DD</sub> + 0.5 V <sup>[37]</sup> |

| Output current into outputs (LOW) | 20 mA    |

|-----------------------------------|----------|

| Static discharge voltage          | > 2000 V |

| (JEDEC JESD22-A114-2000B)         |          |

| Latch-up current                  | > 200 mA |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>DD</sub> | V <sub>CORE</sub> <sup>[36]</sup> |

|------------|------------------------|-----------------|-----------------------------------|

| Commercial | 0 °C to +70 °C         | 3.3 V ± 165 mV  | 1.8 V ± 100 mV                    |

| Industrial | –40 °C to +85 °C       | 3.3 V ± 165 mV  | 1.8 V ± 100mV                     |

Electrical Characteristics Over the Operating Range

| Devenueter                        | Description                                                                                                    | Davit Na                     |      | -167 |     |      | -133 |     |      | -100 |     | Unit |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------|------|------|-----|------|------|-----|------|------|-----|------|

| Parameter                         | Description Part No.                                                                                           | Part No.                     | Min  | Тур  | Max | Min  | Тур  | Max | Min  | Тур  | Max | Unit |

| V <sub>OH</sub>                   | Output HIGH voltage (V <sub>DD</sub> =<br>-4.0 mA)                                                             | = Min., I <sub>OH</sub> =    | 2.4  | -    | -   | 2.4  | -    | -   | 2.4  | -    | -   | V    |

| V <sub>OL</sub>                   | Output LOW voltage (V <sub>DD</sub> = mA)                                                                      | Min., I <sub>OL</sub> = +4.0 | _    | -    | 0.4 | -    | -    | 0.4 | -    | -    | 0.4 | V    |

| V <sub>IH</sub>                   | Input HIGH voltage                                                                                             |                              | 2.0  | -    | _   | 2.0  | _    | -   | 2.0  | -    | -   | V    |

| V <sub>IL</sub>                   | Input LOW voltage                                                                                              |                              | _    | -    | 0.8 | -    | -    | 0.8 | -    | -    | 0.8 | V    |

| I <sub>OZ</sub>                   | Output leakage current                                                                                         |                              | -10  | -    | 10  | -10  | -    | 10  | -10  | -    | 10  | μΑ   |

| I <sub>IX1</sub>                  | Input leakage current excep<br>MRST                                                                            | ot TDI, TMS,                 | -10  | -    | 10  | -10  | -    | 10  | -10  | -    | 10  | μA   |

| I <sub>IX2</sub>                  | Input leakage current TDI, 1                                                                                   | MS, MRST                     | -0.1 | -    | 1.0 | -0.1 | _    | 1.0 | -0.1 | -    | 1.0 | mA   |

| I <sub>CC</sub>                   | Operating current                                                                                              | CYD04S72V                    | _    | 225  | 300 | -    | _    | -   | _    | -    | -   | mA   |

|                                   | (V <sub>DD</sub> = Max.,I <sub>OUT</sub> = 0 mA),<br>outputs disabled                                          | CYD09S72V                    | _    | -    | _   | -    | 350  | 500 | _    | -    | -   |      |

|                                   |                                                                                                                | CYD18S72V                    | _    | -    | _   | -    | 410  | 580 | _    | 315  | 450 | mA   |

| I <sub>SB1</sub>                  | Standby current                                                                                                | CYD04S72V                    | _    | 90   | 115 | -    |      |     | -    | -    | -   | mA   |

|                                   | (both ports TTL level)<br>$CE_L$ and $CE_R \ge V_{IH}$ , f = f <sub>MAX</sub>                                  | CYD09S72V                    | -    | -    | -   | -    | 105  | 150 | -    | -    | -   |      |

| I <sub>SB2</sub>                  | Standby current                                                                                                | CYD04S72V                    | -    | 160  | 210 | -    |      |     | -    | -    | -   | mA   |

|                                   | $\frac{(one port}{CE_{L}} TTL level)$ $CE_{L}   CE_{R} \ge V_{IH}, f = f_{MAX}$                                | CYD09S72V                    | -    | -    | -   | -    | 266  | 380 | -    | -    | -   |      |

| I <sub>SB3</sub>                  | Standby current (both ports                                                                                    | CYD04S72V                    | —    | 55   | 75  | -    |      |     | _    | -    | -   | mA   |

|                                   | CMOS level) $\overline{CE}_{L}$ and $\overline{CE}_{R}$<br>$\geq V_{DD} - 0.2V$ , f = 0                        | CYD09S72V                    | _    | -    | -   | -    | 55   | 75  | -    | -    | -   |      |

| I <sub>SB4</sub>                  | Standby current                                                                                                | CYD04S72V                    | _    | 160  | 210 | -    |      |     | -    | -    | -   | mA   |

|                                   | $\frac{\text{(one port CMOS level)}}{\text{CE}_{L} \mid \text{CE}_{R} \ge \text{V}_{IH}, \text{ f = f}_{MAX}}$ | CYD09S72V                    | -    | -    | _   | -    | 224  | 320 | _    | -    |     |      |

| I <sub>SB5</sub>                  | Operating current (VDDIO<br>= Max, lout = 0 mA, f = 0)<br>outputs disabled                                     | CYD18S72V                    | -    | -    | -   | -    |      | 75  | -    | -    | 75  | mA   |

| I <sub>CORE</sub> <sup>[36]</sup> | Core operating current for (<br>I <sub>OUT</sub> = 0 mA), outputs disab                                        |                              | -    | 0    | 0   | -    | 0    | 0   | -    | 0    | 0   | mA   |

Notes

35. The voltage on any input or I/O pin can not exceed the power pin during power-up. 36. This family of Dual-Ports does not use VCORE, and these pins are internally NC. The next generation Dual-Port family, the FLEx72-E™, will use VCORE of 1.5 V or 1.8 V. Please contact local Cypress FAE for more information.

37. Pulse width < 20 ns.

### Capacitance<sup>[38]</sup>

| Part#     | Parameter        | Description        | Test Conditions                         | Max                | Unit |

|-----------|------------------|--------------------|-----------------------------------------|--------------------|------|

|           | C <sub>IN</sub>  | Input capacitance  | $T_A = 25 ^{\circ}C, f = 1 \text{MHz},$ | 20                 | pF   |

| CYD09S72V | C <sub>OUT</sub> | Output capacitance | V <sub>DD</sub> = 3.3 V                 | 10 <sup>[39]</sup> | pF   |

| CYD18S72V | C <sub>IN</sub>  | Input capacitance  |                                         | 40                 | pF   |

|           | C <sub>OUT</sub> | Output capacitance |                                         | 20                 | pF   |

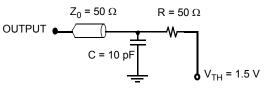

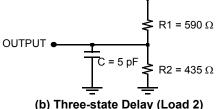

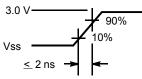

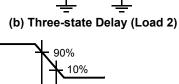

### **AC Test Load and Waveforms**

3.3 V o

(a) Normal Load (Load 1)

ALL INPUT PULSES

<u><</u> 2 ns

### Switching Characteristics Over the Operating Range

|                                |                             |     | 67    |      | -1    | 33   |       | -1   | 00    |      |

|--------------------------------|-----------------------------|-----|-------|------|-------|------|-------|------|-------|------|

| Parameter                      | eter Description            |     | 4S72V | CYD0 | 9S72V | CYD1 | 8S72V | CYD1 | 8S72V | Unit |

|                                |                             | Min | Max   | Min  | Max   | Min  | Max   | Min  | Мах   |      |

| f <sub>MAX2</sub>              | Maximum operating frequency | -   | 167   | -    | 133   | -    | 133   | -    | 100   | MHz  |

| t <sub>CYC2</sub>              | Clock cycle time            | 6.0 | -     | 7.5  | -     | 7.5  | -     | 10   | -     | ns   |

| t <sub>CH2</sub>               | Clock HIGH time             | 2.7 | -     | 3.0  | -     | 3.4  | -     | 4.5  | -     | ns   |

| t <sub>CL2</sub>               | Clock LOW time              | 2.7 | -     | 3.0  | -     | 3.4  | -     | 4.5  | -     | ns   |

| t <sub>R</sub> <sup>[40]</sup> | Clock rise time             | _   | 2.0   | -    | 2.0   | _    | 2.0   | -    | 3.0   | ns   |

| t <sub>F</sub> <sup>[40]</sup> | Clock fall time             | _   | 2.0   | _    | 2.0   | _    | 2.0   | _    | 3.0   | ns   |

| t <sub>SA</sub>                | Address set-up time         | 2.3 | -     | 2.5  | -     | 2.2  | -     | 2.7  | -     | ns   |

| t <sub>HA</sub>                | Address hold time           | 0.6 | _     | 0.6  | -     | 1.0  | -     | 1.0  | _     | ns   |

| t <sub>SB</sub>                | Byte select set-up time     | 2.3 | -     | 2.5  | _     | 2.2  | -     | 2.7  | _     | ns   |

| t <sub>HB</sub>                | Byte select hold time       | 0.6 | -     | 0.6  | -     | 1.0  | -     | 1.0  | -     | ns   |

| t <sub>SC</sub>                | Chip enable set-up time     | 2.3 | -     | 2.5  | _     | NA   | -     | NA   | _     | ns   |

| t <sub>HC</sub>                | Chip enable hold time       | 0.6 | -     | 0.6  | _     | NA   | -     | NA   | _     | ns   |

| t <sub>SW</sub>                | R/W set-up time             | 2.3 | -     | 2.5  | _     | 2.2  | -     | 2.7  | _     | ns   |

| t <sub>HW</sub>                | R/W hold time               | 0.6 | -     | 0.6  | _     | 1.0  | -     | 1.0  | _     | ns   |

| t <sub>SD</sub>                | Input data set-up time      | 2.3 | -     | 2.5  | _     | 2.2  | -     | 2.7  | _     | ns   |

| t <sub>HD</sub>                | Input data hold time        | 0.6 | -     | 0.6  | _     | 1.0  | -     | 1.0  | -     | ns   |

#### Notes

38. C<sub>OUT</sub> also references  $C_{I/O}$ . 39. Except INT and CNTINT which are 20 pF. 40. Except JTAG signal (t<sub>R</sub> and t<sub>F</sub> < 10 ns max).

Page 14 of 30

### Switching Characteristics Over the Operating Range (continued)

|                                       |                                                   | -1   | 67    |      | -1    | 33   |       | -1        | 00   |        |

|---------------------------------------|---------------------------------------------------|------|-------|------|-------|------|-------|-----------|------|--------|

| Parameter                             | Description                                       | CYD0 | 4S72V | CYD0 | 9S72V | CYD1 | 8S72V | CYD18S72V |      | Unit   |

|                                       |                                                   | Min  | Max   | Min  | Мах   | Min  | Max   | Min       | Max  |        |

| t <sub>SAD</sub>                      | ADS set-up time                                   | 2.3  | _     | 2.5  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>HAD</sub>                      | ADS hold time                                     | 0.6  | _     | 0.6  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>SCN</sub>                      | CNTEN set-up time                                 | 2.3  | _     | 2.5  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>HCN</sub>                      | CNTEN hold time                                   | 0.6  | _     | 0.6  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>SRST</sub>                     | CNTRST set-up time                                | 2.3  | _     | 2.5  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>HRST</sub>                     | CNTRST hold time                                  | 0.6  | _     | 0.6  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>SCM</sub>                      | CNT/MSK set-up time                               | 2.3  | _     | 2.5  | _     | NA   | _     | NA        | _    | ns     |

| t <sub>HCM</sub>                      | CNT/MSK hold time                                 | 0.6  | _     | 0.6  | _     | NA   | _     | NA        | _    | ns     |

| tor                                   | Output enable to data valid                       | _    | 4.0   | -    | 4.4   | _    | 5.5   | _         | 5.5  | ns     |

| t <sub>OLZ</sub> <sup>[41, 42]</sup>  | OE to Low Z                                       | 0    | _     | 0    | _     | 0    | _     | 0         | _    | ns     |

| t <sub>OHZ</sub> <sup>[41, 42]</sup>  | OE to High Z                                      | 0    | 4.0   | 0    | 4.4   | 0    | 5.5   | 0         | 5.5  | ns     |

| t <sub>CD2</sub>                      | Clock to data valid                               | -    | 4.0   | -    | 4.4   | -    | 5.0   | -         | 5.2  | ns     |

| t <sub>CA2</sub>                      | Clock to counter address valid                    | -    | 4.0   | -    | 4.4   | -    | NA    | -         | NA   | ns     |

| t <sub>CM2</sub>                      | Clock to mask register readback valid             | _    | 4.0   | _    | 4.4   | _    | NA    | _         | NA   | ns     |

| t <sub>DC</sub>                       | Data output hold after clock<br>HIGH              | 1.0  | _     | 1.0  | _     | 1.0  | _     | 1.0       | _    | ns     |

| t <sub>CKHZ</sub> [41, 42]            | Clock HIGH to output High Z                       | 0    | 4.0   | 0    | 4.4   | 0    | 4.7   | 0         | 5.0  | ns     |

| t <sub>CKLZ</sub> <sup>[41, 42]</sup> | Clock HIGH to output Low Z                        | 1.0  | 4.0   | 1.0  | 4.4   | 1.0  | 4.7   | 1.0       | 5.0  | ns     |

| t <sub>SINT</sub>                     | Clock to INT set time                             | 0.5  | 6.7   | 0.5  | 7.5   | 0.5  | 7.5   | 0.5       | 10   | ns     |

| t <sub>RINT</sub>                     | Clock to INT reset time                           | 0.5  | 6.7   | 0.5  | 7.5   | 0.5  | 7.5   | 0.5       | 10   | ns     |

| t <sub>SCINT</sub>                    | Clock to CNTINT set time                          | 0.5  | 5.0   | 0.5  | 5.7   | NA   | NA    | NA        | NA   | ns     |

| t <sub>RCINT</sub>                    | Clock to CNTINT reset time                        | 0.5  | 5.0   | 0.5  | 5.7   | NA   | NA    | NA        | NA   | ns     |

| Port to Por                           | t Delays                                          |      | ı     |      |       | I.   |       |           |      |        |

| t <sub>CCS</sub>                      | Clock to clock skew                               | 5.2  | _     | 6.0  | _     | 5.7  | _     | 8.0       | _    | ns     |

| Master Res                            | et Timing                                         |      | ı     |      |       | I.   |       |           |      |        |

| t <sub>RS</sub>                       | Master reset pulse width                          | 5.0  | _     | 5.0  | _     | 5.0  | -     | 5.0       | _    | cycles |

| t <sub>RSS</sub>                      | Master reset set-up time                          | 6.0  | _     | 6.0  | _     | 6.0  | -     | 8.5       | _    | ns     |

| t <sub>RSR</sub>                      | Master reset recovery time                        | 5.0  | -     | 5.0  | -     | 5.0  | -     | 5.0       | _    | cycles |

| t <sub>RSF</sub>                      | Master Reset to outputs inactive                  | _    | 10.0  | _    | 10.0  | _    | 10.0  | _         | 10.0 | ns     |

| t <sub>RSCNTINT</sub>                 | Master reset to counter interrupt flag reset time | _    | 10.0  | -    | 10.0  | -    | NA    | -         | NA   | ns     |

Notes41. This parameter is guaranteed by design, but is not production tested.42. Test conditions used are Load 2.

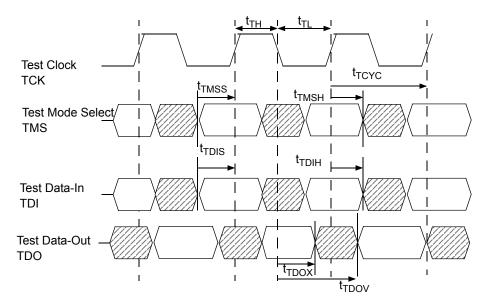

### **JTAG Timing Characteristics**

| Parameter         | Description                           | CYD0<br>CYD1 | CYD04S72V<br>CYD09S72V<br>CYD18S72V<br>-167/-133/-100 |     |  |

|-------------------|---------------------------------------|--------------|-------------------------------------------------------|-----|--|

|                   |                                       | Min          | Max                                                   |     |  |

| f <sub>JTAG</sub> | Maximum JTAG TAP controller frequency | -            | 10                                                    | MHz |  |

| t <sub>TCYC</sub> | TCK clock cycle time                  | 100          | -                                                     | ns  |  |

| t <sub>TH</sub>   | TCK clock HIGH time                   | 40           | -                                                     | ns  |  |

| t <sub>TL</sub>   | TCK clock LOW time                    | 40           | -                                                     | ns  |  |

| t <sub>TMSS</sub> | TMS set-up to TCK clock rise          | 10           | -                                                     | ns  |  |

| t <sub>TMSH</sub> | TMS hold after TCK clock rise         | 10           | -                                                     | ns  |  |

| t <sub>TDIS</sub> | TDI set-up to TCK clock rise          | 10           | -                                                     | ns  |  |

| t <sub>TDIH</sub> | TDI hold after TCK clock rise         | 10           | -                                                     | ns  |  |

| t <sub>TDOV</sub> | TCK clock LOW to TDO valid            | -            | 30                                                    | ns  |  |

| t <sub>TDOX</sub> | TCK clock LOW to TDO invalid          | 0            | -                                                     | ns  |  |

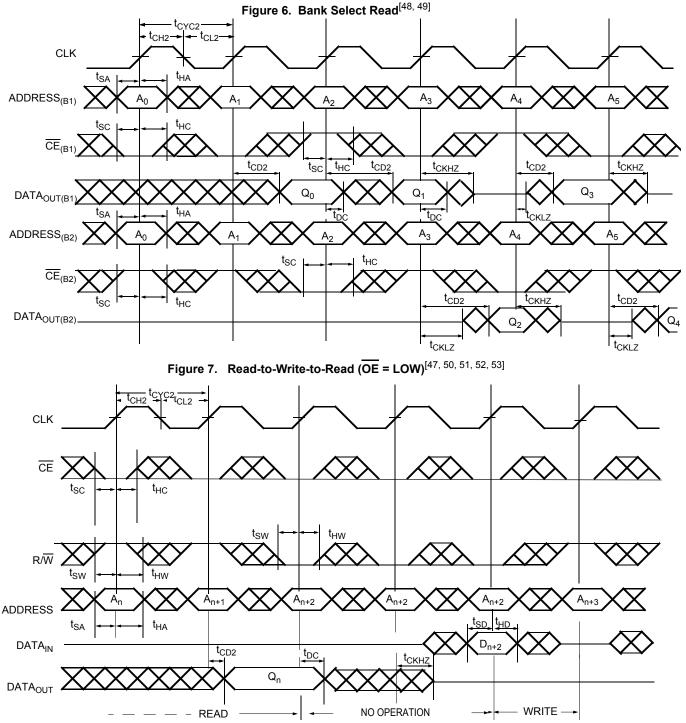

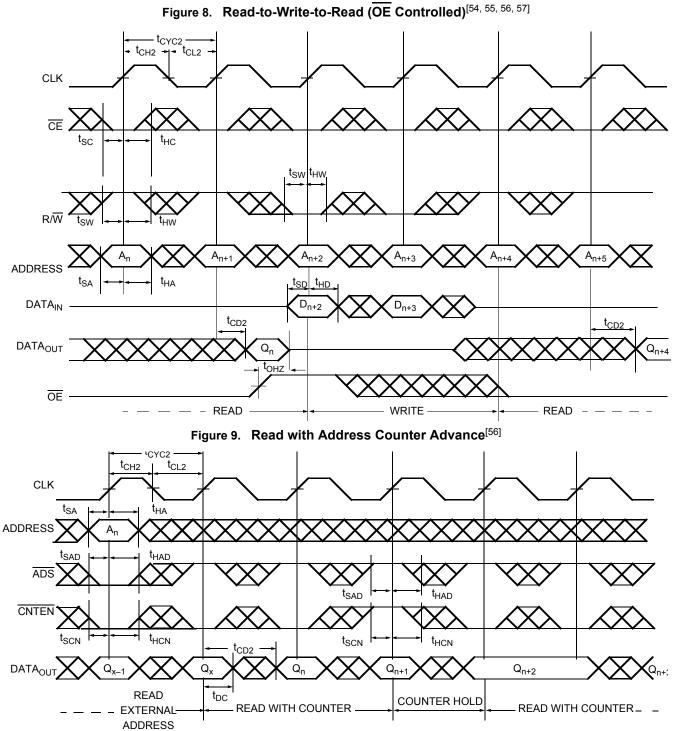

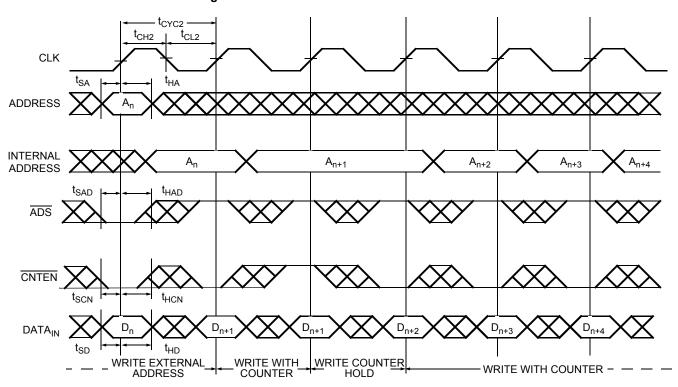

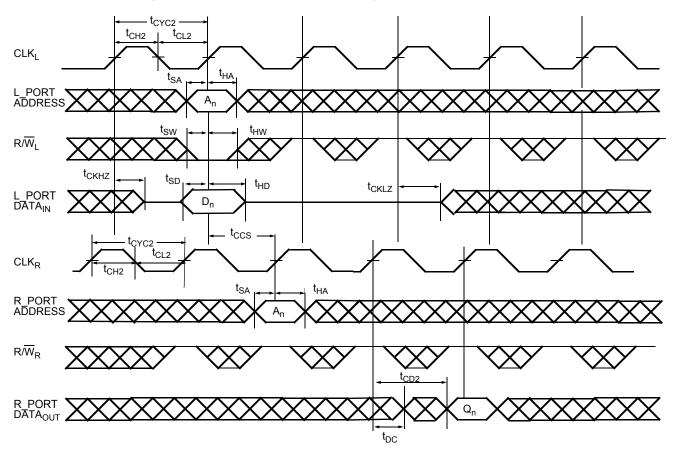

### **Switching Waveforms**

- Notes

43. CE is internal signal. CE = LOW if CE<sub>0</sub> = LOW and CE<sub>1</sub> = HIGH. For a single Read operation, CE only needs to be asserted once at the rising edge of the CLK and can be deasserted after that. Data will be out after the following CLK edge and will be three-stated after the next CLK edge.

44. OE is asynchronously controlled; all other inputs (excluding MRST and JTAG) are synchronous to the rising clock edge.

45. ADS = CNTEN = LOW, and MRST = CNTRST = CNT/MSK = HIGH.

- 46. The output is disabled (high-impedance state) by  $\overrightarrow{CE} = V_{||I|}$  following the next rising edge of the clock. 47. Addresses do not have to be accessed sequentially since  $\overrightarrow{ADS} = \overrightarrow{CNTEN} = V_{||L|}$  with  $\overrightarrow{CNT/MSK} = V_{||I|}$  constantly loads the address on the rising edge of the CLK. Numbers are for reference only.

#### Notes

48. In this depth-expansion example, B1 represents Bank #1 and B2 is Bank #2; each bank consists of one Cypress FLEx72 device from this data sheet. ADDRESS(B1) = ADDRESS(B2).

49. ADS = CNTEN = BE0 - BE7 = OE = LOW; MRST = CNTRST = CNT/MSK = HIGH.

50. Output state (HIGH, LOW, or high-impedance) is determined by the previous cycle control signals.

51. During "No Operation," data in memory at the selected address may be corrupted and should be rewritten to ensure data integrity.