# Dual Input Network Clock Generator/Synchronizer

AD9549

#### **FEATURES**

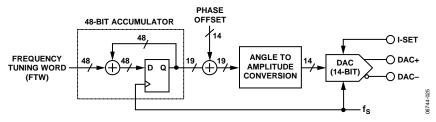

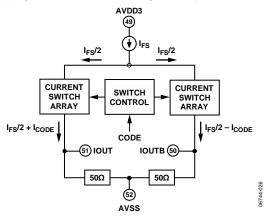

Flexible reference inputs Input frequencies: 8 kHz to 750 MHz Two reference inputs Loss of reference indicators Auto and manual holdover modes Auto and manual switchover modes Smooth A-to-B phase transition on outputs **Excellent stability in holdover mode** Programmable 16 + 1-bit input divider, R **Differential HSTL clock output Output frequencies to 750 MHz** Low jitter clock doubler for frequencies of >400 MHz Single-ended CMOS output for frequencies of <150 MHz Programmable digital loop filter (<1 Hz to ~100 kHz) High speed digitally controlled oscillator (DCO) core Direct digital synthesizer (DDS) with integrated 14-bit DAC

Direct digital synthesizer (DDS) with integrated 14-bit Excellent dynamic performance

Programmable 16 + 1-bit feedback divider, S

Software controlled power-down

Available 64-lead LFCSP package

#### **APPLICATIONS**

Network synchronization

Reference clock jitter cleanup

SONET/SDH clocks up to OC-192, including FEC

Stratum 3/3E reference clocks

Wireless base station, controllers

Cable infrastructure

Data communications

#### **GENERAL DESCRIPTION**

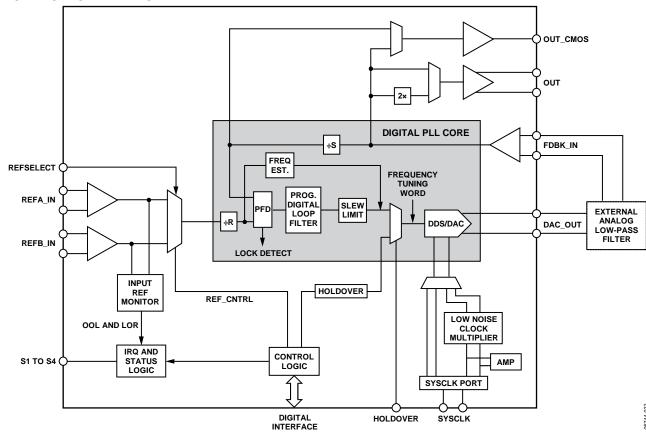

The AD9549 provides synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9549 generates an output clock, synchronized to one of two external input references. The external references may contain significant time jitter, also specified as phase noise. Using a digitally controlled loop and holdover circuitry, the AD9549 continues to generate a clean (low jitter), valid output clock during a loss of reference condition, even when both references have failed.

The AD9549 operates over an industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

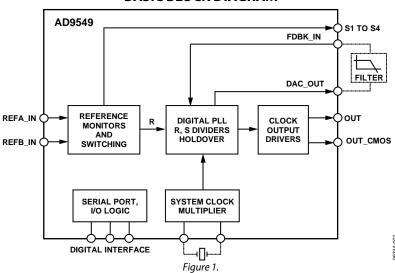

#### **BASIC BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| reatures                                         | 1  |

|--------------------------------------------------|----|

| Applications                                     | 1  |

| General Description                              | 1  |

| Basic Block Diagram                              | 1  |

| Revision History                                 | 3  |

| Specifications                                   | 4  |

| DC Specifications                                | 4  |

| AC Specifications                                | 6  |

| Absolute Maximum Ratings                         | 9  |

| Thermal Resistance                               | 9  |

| ESD Caution                                      | 9  |

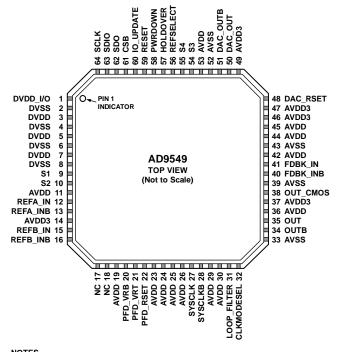

| Pin Configuration and Function Descriptions      | 10 |

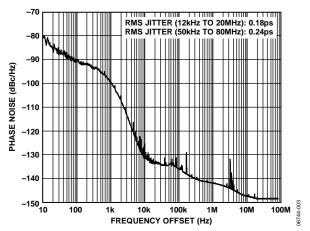

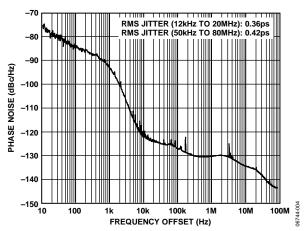

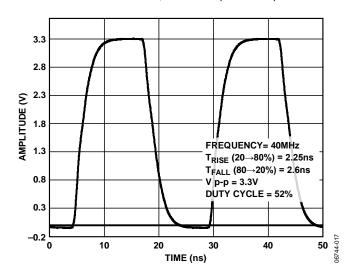

| Typical Performance Characteristics              | 13 |

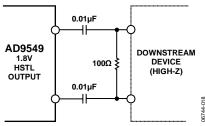

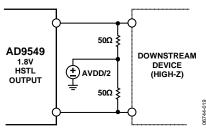

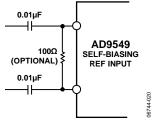

| Input/Output Termination Recommendations         | 16 |

| Theory of Operation                              | 17 |

| Overview                                         | 17 |

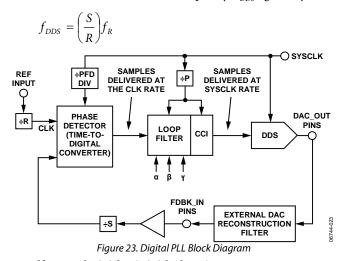

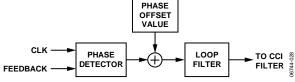

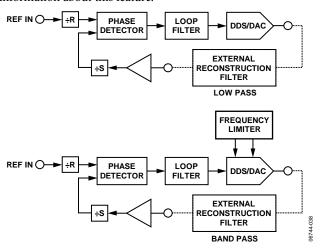

| Digital PLL Core (DPLLC)                         | 17 |

| Phase Detector                                   | 21 |

| Digital Loop Filter Coefficients                 | 22 |

| Closed-Loop Phase Offset                         | 24 |

| Lock Detection                                   | 24 |

| Reference Monitors                               | 26 |

| Reference Switchover                             | 27 |

| Holdover                                         | 29 |

| Output Frequency Range Control                   | 32 |

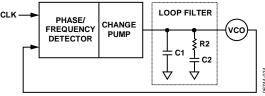

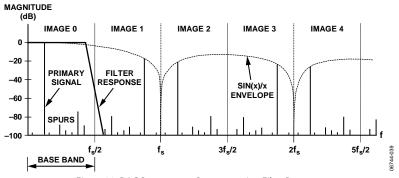

| Reconstruction Filter                            | 32 |

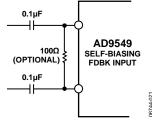

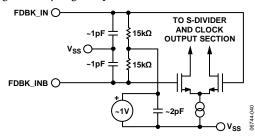

| FDBK_IN Inputs                                   | 33 |

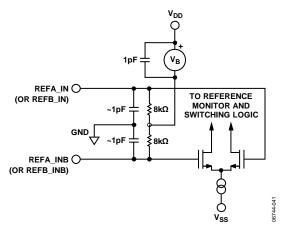

| Reference Inputs                                 | 33 |

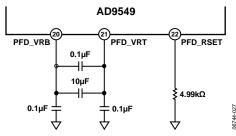

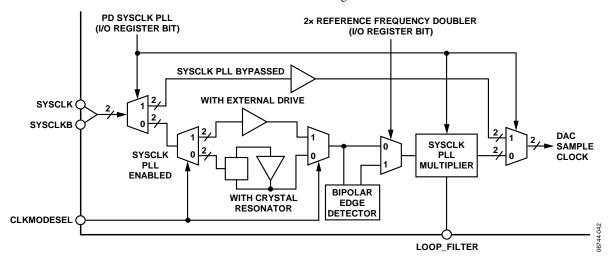

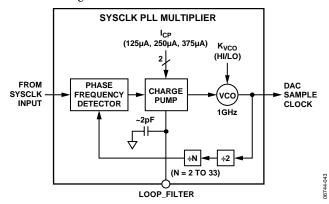

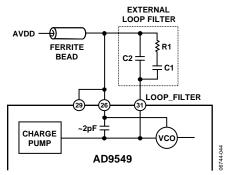

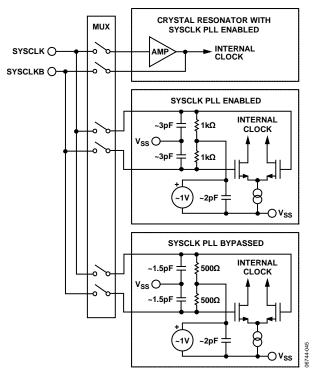

| SYSCLK Inputs                                    | 33 |

| Harmonic Spur Reduction                          | 35 |

| Output Clock Drivers and 2× Frequency Multiplier | 36 |

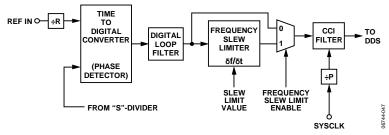

| Frequency Slew Limiter                           | 37 |

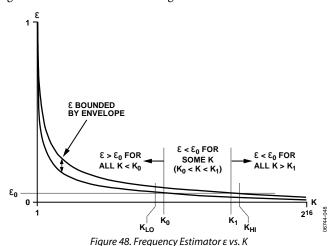

| Frequency Estimator                              | 37 |

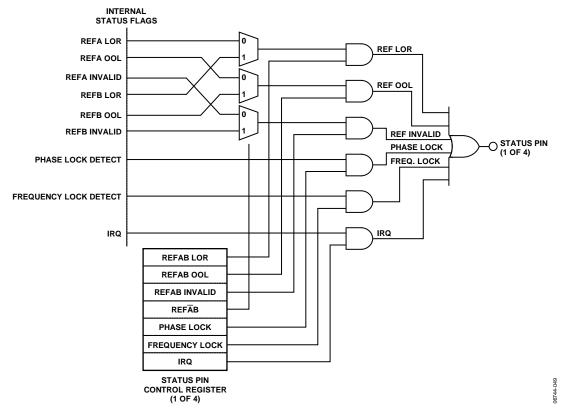

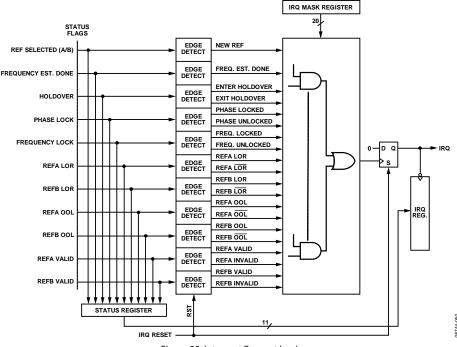

| Status and Warnings                              | 39 |

| Thermal Performance                              | 41 |

| Power-Up4                                                               | 2  |

|-------------------------------------------------------------------------|----|

| Power-On Reset                                                          | 2  |

| Programming Sequence4                                                   | 2  |

| Power Supply Partitioning4                                              | 3  |

| 3.3 V Supplies                                                          | 3  |

| 1.8 V Supplies4                                                         | 3  |

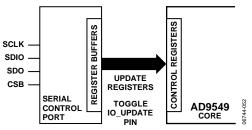

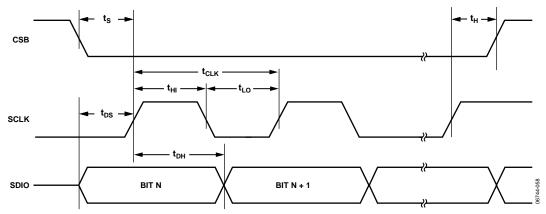

| Serial Control Port4                                                    | 4  |

| Serial Control Port Pin Descriptions4                                   | 4  |

| Operation of Serial Control Port4                                       | 4  |

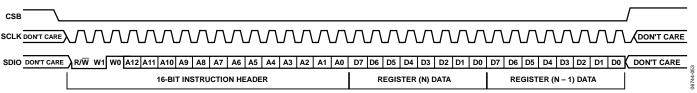

| The Instruction Word (16 Bits)4                                         | 5  |

| MSB/LSB First Transfers                                                 | 5  |

| I/O Register Map4                                                       | 8  |

| I/O Register Descriptions5                                              | 3  |

| Serial Port Configuration (Register 0x0000 to Register 0x0005)          | 3  |

| Power-Down and Reset (Register 0x0010 to Register 0x0013)               |    |

| System Clock (Register 0x0020 to Register 0x0023)5                      | 4  |

| Digital PLL Control and Dividers (Register 0x0100 to Register 0x0130)   | 55 |

| Free-Run (Single-Tone) Mode (Register 0x01A0 to Register 0x01AD)        | 51 |

| Reference Selector/Holdover (Register 0x01C0 to Register 0x01C3)        |    |

| Doubler and Output Drivers (Register 0x0200 to Register 0x0201)         |    |

| Monitor (Register 0x0300 to Register 0x0335)                            |    |

| Calibration (User-Accessible Trim) (Register 0x0400 to Register 0x0410) |    |

| Harmonic Spur Reduction (Register 0x0500 to Register 0x0509)            | 1  |

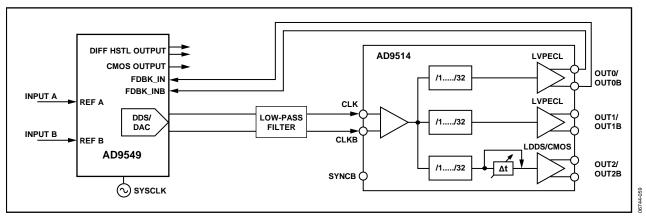

| Applications Information7                                               | 3  |

| Sample Applications Circuit                                             | ′3 |

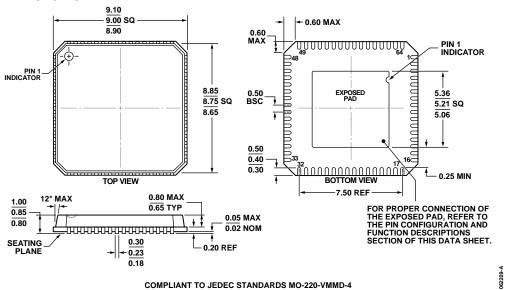

| Outline Dimensions                                                      | 4  |

| Ordering Guide                                                          | 4  |

### **REVISION HISTORY**

| 12/10—Rev. C to Rev. D                                                            |

|-----------------------------------------------------------------------------------|

| Changes to I <sub>AVDD</sub> (Pin 19, Pin 23 to Pin 26, Pin 29, Pin 30,           |

| Pin44, Pin 45) Parameter4                                                         |

| Changes to Total Power Dissipation Parameter and Added                            |

| Endnote 45                                                                        |

| Changes to Pin 59 Description11                                                   |

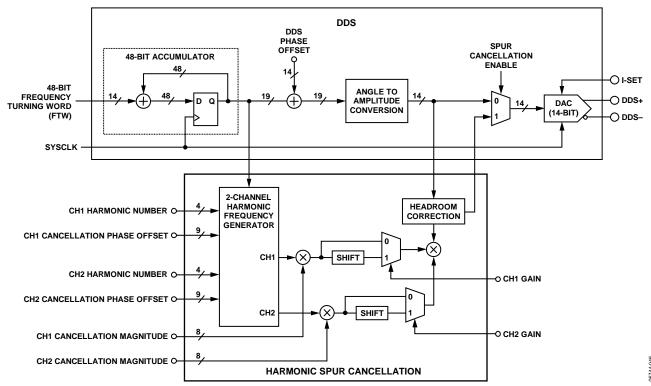

| Changes to Direct Digital Synthesizer (DDS) Section20                             |

| Changes to Power-Up Section42                                                     |

| Changes to Address 0x0002 Default Value (in Table 13)48                           |

| Changes to Address 0x0400 and Address 0x40E Default Values                        |

| (in Table 13)52                                                                   |

|                                                                                   |

| 5/10—Rev. B to Rev. C                                                             |

| D.1.(.164 I1 I.DCCD (CD 64 1)                                                     |

| Deleted 64-Lead LFCSP (CP-64-1)Universal                                          |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input                          |

|                                                                                   |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input                          |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| Changes to SYSCLK PLL Enabled/Minimum Differential Input Level Parameter, Table 2 |

| 12/09—Rev. 0 to Rev. A                                  |   |

|---------------------------------------------------------|---|

| Added 64-Lead LFCSP (CP-64-7) Universa                  | 1 |

| Changes to Total Power Dissipation Parameter            | 5 |

| Changes to Serial Port Timing Specifications and        |   |

| Propagation Delay Parameters                            | 3 |

| Added Exposed Paddle Notation to Figure 2; Changes to   |   |

| Table 410                                               | ) |

| Corrected DDS Phase Offset Resolution from 16 Bits to   |   |

| 14 Bits Throughout; Change to Figure 2520               | ) |

| Changes to Phase Lock Detection Section24               | 4 |

| Change to Figure 3025                                   |   |

| Changes to Loss of Reference and Reference Frequency    |   |

| Monitor Sections                                        | 5 |

| Change to Output Frequency Range Control Section32      | 2 |

| Change to Figure 4636                                   | 5 |

| Changes to Frequency Estimator Section33                | 7 |

| Changes to Programming Sequence Section42               | 2 |

| Changes to Power Supply Partitioning Section43          |   |

| Change to Serial Control Port Section44                 | 1 |

| Changes to Figure 5440                                  |   |

| Added Exposed Paddle Notation to Outline Dimensions and |   |

| Changes to Ordering Guide74                             | 4 |

8/07—Revision 0: Initial Version

## SPECIFICATIONS DC SPECIFICATIONS

$AVDD = 1.8 \text{ V} \pm 5\%, AVDD3 = 3.3 \text{ V} \pm 5\%, DVDD = 1.8 \text{ V} \pm 5\%, DVDD\_I/O = 3.3 \text{ V} \pm 5\%. AVSS = 0 \text{ V}, DVSS = 0 \text{ V}, unless otherwise noted.}$

Table 1.

| Parameter                                            | Min     | Тур     | Max      | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|---------|---------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLY VOLTAGE                                       |         |         |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DVDD_I/O (Pin 1)                                     | 3.135   | 3.30    | 3.465    | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DVDD (Pin 3, Pin 5, Pin 7)                           | 1.71    | 1.80    | 1.89     | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AVDD3 (Pin 14, Pin 46, Pin 47, Pin 49)               | 3.135   | 3.30    | 3.465    | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AVDD3 (Pin 37)                                       | 1.71    | 3.30    | 3.465    | V      | Pin 37 is typically 3.3 V, but can be set to 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AVDD (Pin 11, Pin 19, Pin 23 to Pin 26, Pin 29,      | 1.71    | 1.80    | 1.89     | V      | in the syptem year of the section in |

| Pin 30, Pin 36, Pin 42, Pin 44, Pin 45, Pin 53)      |         |         |          | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SUPPLY CURRENT                                       |         |         |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I <sub>AVDD3</sub> (Pin 14)                          |         | 4.7     | 5.6      | mA     | REFA, REFB buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I <sub>AVDD3</sub> (Pin 37)                          |         | 3.8     | 4.5      | mA     | CMOS output clock driver at 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I <sub>AVDD3</sub> (Pin 46, Pin 47, Pin 49)          |         | 26      | 29       | mA     | DAC output current source, $f_s = 1$ GSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I <sub>AVDD</sub> (Pin 36, Pin 42)                   |         | 21      | 26       | mA     | FDBK_IN input, HSTL output clock driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AVDD (* 2 s) *                                       |         |         |          |        | (output doubler turned on)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I <sub>AVDD</sub> (Pin 11)                           |         | 12      | 15       | mA     | REFA and REFB input buffer 1.8 V supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sub>AVDD</sub> (Pin 19, Pin 23 to Pin 26, Pin 29, |         | 215     | 281      | mA     | Aggregate analog supply, including system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin 30, Pin 44, Pin 45)                              |         |         |          |        | clock PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I <sub>AVDD</sub> (Pin 53)                           |         | 41      | 49       | mA     | DAC power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I <sub>DVDD</sub> (Pin 3, Pin 5, Pin 7)              |         | 254     | 265      | mA     | Digital core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sub>DVDD_I/O</sub> (Pin 1)                        |         | 4       | 6        | mA     | Digital I/O (varies dynamically)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LOGIC INPUTS (Except Pin 32)                         |         |         |          |        | Pin 9, Pin 10, Pin 54 to Pin 61, Pin 63, Pin 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input High Voltage (V <sub>IH</sub> )                | 2.0     |         | DVDD_I/O | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Low Voltage (V <sub>II</sub> )                 | DVSS    |         | 0.8      | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |         | ±60     | ±200     | μΑ     | At $V_{IN} = 0 \text{ V}$ and $V_{IN} = DVDD_I/O$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Maximum Input Capacitance (C <sub>IN</sub> )         |         | 3       |          | pF     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLKMODESEL (Pin 32) LOGIC INPUT                      |         |         |          | T.     | Pin 32 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Input High Voltage (V <sub>IH</sub> )                | 1.4     |         | AVDD     | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Low Voltage (V <sub>IL</sub> )                 | AVSS    |         | 0.4      | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) | 755     | -18     | -50      | μA     | At $V_{IN} = 0$ V and $V_{IN} = AVDD$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Maximum Input Capacitance (C <sub>IN</sub> )         |         | 3       |          | рF     | The vine of and vine the state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LOGIC OUTPUTS                                        |         |         |          |        | Pin 62 and the following bidirectional pins:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

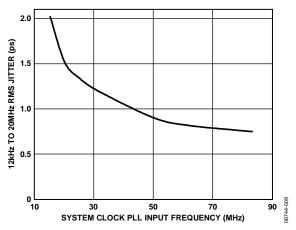

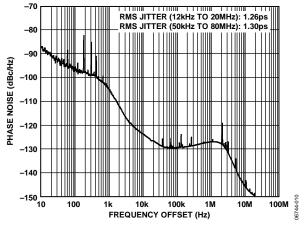

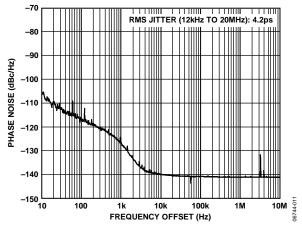

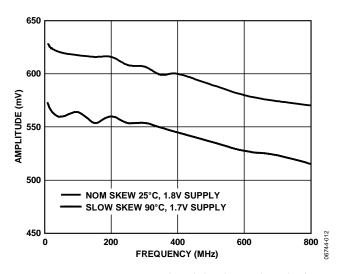

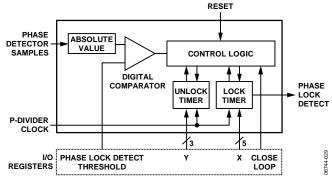

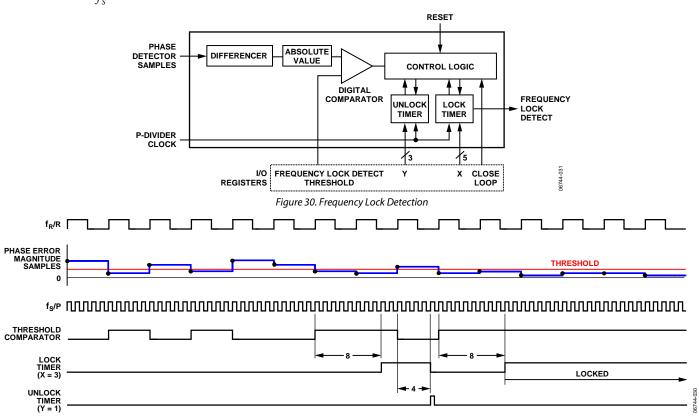

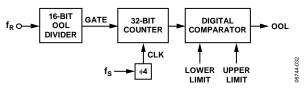

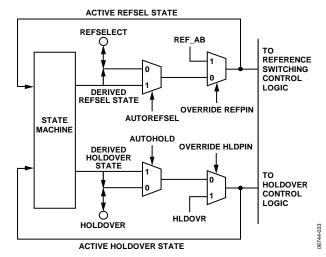

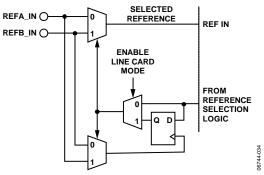

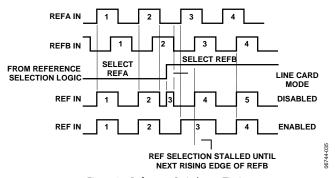

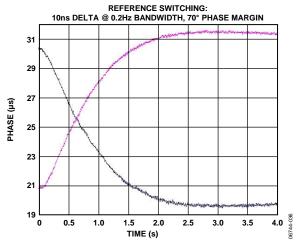

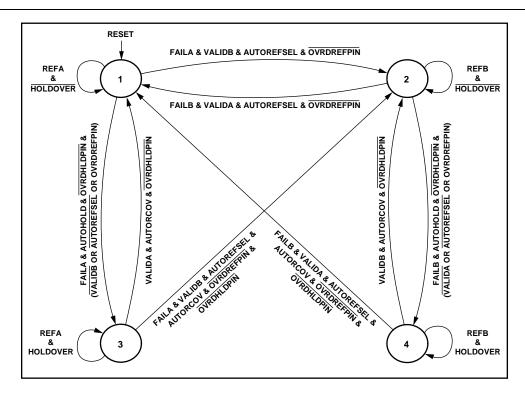

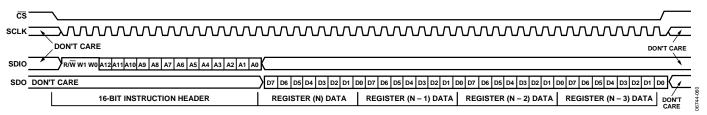

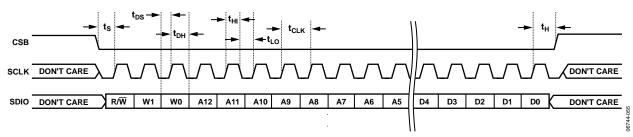

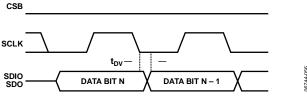

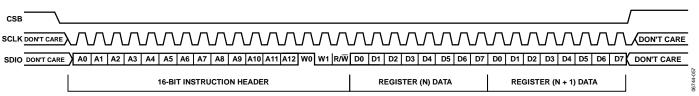

|                                                      |         |         |          |        | Pin 9, Pin 10, Pin 54, Pin 55, Pin 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |