# Integrated Circuit High Speed Operational Amplifier

AD505

**FEATURES**

High Slew Rate: 120V/ $\mu$ sec min Fast Settling Time: 0.1% in 800nsec

0.01% in 2μsec

Low V<sub>OS</sub>: 2.5mV max (K) Low V<sub>OS</sub>: 2.5mV max (K)

Low  $V_{os}$  Drift:  $15\mu V/^{\circ}C$  max (K)

Drives 1000pF

Low Price: \$10.00 (100's, J)

APPLICATIONS

D/A and A/D Conversion

Wideband Amplifiers

Active Filters

Pulse Amplifiers

Fast Multiplier Pre-Amps

PRODUCT DESCRIPTION

The Analog Devices AD505 J, AD505 K and AD505 S are monolithic operational amplifiers that are specifically designed for applications requiring high slew rate and fast settling time to high accuracy. The AD505 achieves a minimum slew rate of  $120V/\mu$ sec, provides an adjustable unity gain bandwidth product of 4MHz to 10MHz, and settles to 0.1% in 800nsec. In addition to its superior dynamic characteristics, the AD505 maintains high gain, maximum offset voltage drift of  $15\mu V/^{\circ}$ C, maximum bias currents of 25nA and high output swing.

The circuit has a stable 6dB/octave rolloff for closed loop operation. It is also capable of being externally adjusted for up to 35dB of additional closed loop gain at high frequencies, without causing the small signal or large signal bandwidth to decrease, and without increasing settling times.

The AD505 is designed for high speed inverting applications by using a feed-forward technique. It can drive capacitive loads in excess of 1000pF and is short circuit protected.

The AD505 provides performance superior to most high speed IC op amps and comparable to modular versions. Because of its monolithic construction, however, its cost is significantly below that of modules, and becomes even lower in large quantities.

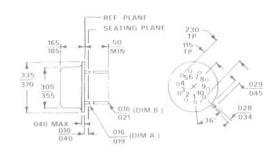

All the circuits are supplied in the TO-100 package. The AD505J and AD505K are specified for  $0^{\circ}$ C to  $+70^{\circ}$ C temperature range operation; the AD505S for operation from  $-55^{\circ}$ C to  $+100^{\circ}$ C.

PRODUCT HIGHLIGHTS

- The AD506 achieves a minimum slew rate of 120V/µsec and settles to 0.1% in 800nsec.

- 2. All guaranteed parameters, including slew rate and offset voltage drift, are 100% tested.

- 3. The AI 505 maintains low bias currents of 25nA max and low  $V_{OS}$  drift of  $15\mu V/^{\circ}C$  max.

- 4. Ease of use and predictability of operation make the AD505 an all-purpose amplifier that is free of the problems found in most high frequency amplifiers

#### SLEW RATE AND SETTLING TIME

Both slew rate and settling time are measures of an amplifier's speed of response to an input. Slew rate is an inherent characteristic of the amplifier and, thus, is generally less subject to misinterpretation than is settling time, which is often more dependent upon the test circuit than the amplifier's ability to perform.

Slew rate defines the maximum rate of change of output voltage for a large input step change and can be related to the full power response  $(f_p)$  by the relationship . . . . .

$$S=2\pi f_p E_0$$

.... where Eo is the peak output voltage.

(continued on page 3)

# SPECIFICATIONS (typical @ +25°C and ±15VDC, unless otherwise noted)

| PARAMETER                                                                                                                                             | AD505J                                                                            | AD505K                                             | AD505S                                                    |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|--------|

| $\begin{aligned} & \text{OPEN LOOP GAIN} \\ & R_L = 2k\Omega, V_0 = \pm 10V \\ & \text{Over Temp Range } (T_{min} \text{ to } T_{max}) \end{aligned}$ | 100,000 min (500,000 typ)<br>75,000 min                                           | 200,000 min (500,000 typ)<br>150,000 min           | **<br>100,000 min                                         |        |

| OUTPUT CHARACTERISTICS $Voltage @ R_L = 2k\Omega \\ Over Temp Range (T_{min} to T_{max}) \\ Current @ V_O = \pm 10V \\ Short Circuit Current$         | ±10V min (±12V typ)<br>±10mA<br>25mA                                              | :                                                  | *                                                         |        |

| FREQUENCY RESPONSE Unity Gain, Small Signal Full Power Response Slew Rate Settling Fime (Note 1) tw 0.1%                                              | 4 - 10MHz (adjustable)<br>2.0MHz min (2.5MHz typ)<br>120V/μsec min (150V/μsec typ | * * *                                              | •                                                         |        |

| INPUT OFFSET VOLTAGE Initial, RS \leq 10k\Omega\$  Avg vs Temp (Tmin to Tmax)  vs Supply (min to Tmax)                                                | 2.0µsec  10mV max (1.0mV typ) 15µV/° C 15µV/V max (80µV/V typ)                    | * 2.5mV max (1.0mV typ) 15µV/°C max (8µV/°C typ) * | ** 20µV/°C max (10µV/°C typ)                              |        |

| INPUT RIAS CURRENT Initial Over Temp Range (min to Tmax) Avg vs Temp (Tmin to Tmax)                                                                   | 75nA max (15nA typ)<br>10/nA max<br>5.1nA/C                                       | 27nA max (15nA typ)<br>OnA max<br>*                | **<br>80nA max<br>*                                       | ·<br>/ |

| INPUT IMPEDANCE<br>DC<br>Above 10Hz                                                                                                                   | 2MΩ<br>20kΩ                                                                       |                                                    |                                                           |        |

| INPUT NOISE  Voltage, 0.01 to 10Hz(p-p)  0.01 to 1.0MHz(rms)  Current, 0.01 to 10Hz(p-p)                                                              | 2.5μV<br>10μV<br>0.1nA                                                            |                                                    |                                                           |        |

| POWER SUPPLY Rated Performance Operating, Derated Performance Current, Quiescent                                                                      | ±15V<br>±(5 to 20)V<br>8.0mA max (6.0mA typ)                                      | :                                                  | :                                                         |        |

| TEMPERATURE RANGE Rated Performance (T <sub>min</sub> to T <sub>max</sub> ) Operating Storage                                                         | 0°C to +70°C<br>-25°C to +85°C<br>-65°C to +150°C                                 | •                                                  | -55°C to +100°C (Note 2)<br>-55°C to +100°C (Note 2)<br>* |        |

| PRICE (Note 3)<br>(1–24)<br>(25–99)<br>(100–999)                                                                                                      | \$15.00<br>\$12.00<br>\$10.00                                                     | \$18.00<br>\$14.40<br>\$12.00                      | \$21.00<br>\$16.80<br>\$14.00                             |        |

# NOTES:

<sup>&</sup>lt;sup>1</sup>See Figure 1 for test circuit diagram.

3+125°C operation is possible with a 100°C/W heat sink.

Subject to change; refer to latest Microcircuit Price List

<sup>\*</sup>Specifications same as AD505J \*\*Specifications same as AD505K

## (continued from page 1)

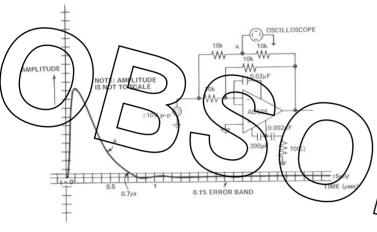

Settling time is defined as the time elapsed from the application of a fast step input to the time when the amplifier output has entered and remained within a specified error band that is symmetrical about the final value. Settling time, therefore, is comprised of an initial propagation delay, an additional time for the amplifier to slew to the vicinity of some value of output voltage, and a time period to recover from overload and sertle within the given error band (see Figure 1).

ADI tests for slew rate and settling time in a unity gain configuration (RS =  $R_f = 10k\Omega$ ), no capacitive load, and a -10 volt to a +10 volt output swing.

Figure 1. Settling Time of the AD505.

The full power response of the AD505 is displayed in Figure 2 for supply voltages of  $\pm 15 \text{V}$  and  $\pm 10 \text{V}$ . Note that at  $\text{VS} = \pm 15 \text{V}$  the full power response is greater than 2MHz and that it decreases as the supply voltages are lowered.

Figure 2. Full Power Response of the AD505.

#### APPLICATIONS CONSIDERATIONS

The AD505 combines excellent DC characteristics and dynamic performance with ease of application. Because it is a wideband, fast settling amplifier, certain practical stabilization and interconnection techniques are suggested to insure proper operation and minimize user experimentation.

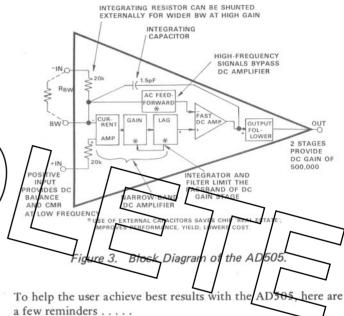

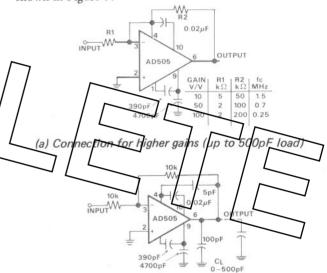

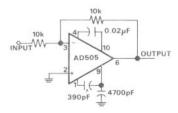

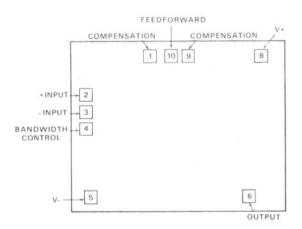

The feed-forward operation of the AD505 is shown in the block diagram in Figure 3. The DC signal is via the input differential current amplifier, followed by a gain stage. An external 390pF capacitor connected between pins 1 and 9 makes this gain stage an integrator and optimizes settling time. A 4700pF capacitor in series with a  $100\Omega$  resistor is connected between pins 9 and 5 (V–) to provide a lag which insures that this portion of the amplifier rolls off to below unity gain above the frequency at which the fast DC amplifier starts its rolloff. The AC signal is fed forward by an external  $0.02\mu F$  capacitor connected between pin 4 and pin 10 into the other differential input of the fast DC amplifier.

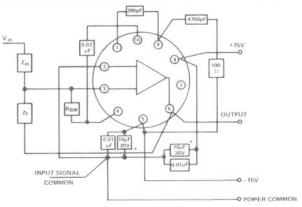

- (1) Power supply bypasses should be provided as close to the amplifier as possible to eliminate ringing due to the inductance of power supply leads. A tantalum  $10\mu\text{F}$  capacitor in parallel with a ceramic  $0.01\mu\text{F}$  capacitor is sufficient for this purpose (see Figure 4).

- (2) All ground connections should be made at a single ground point.

- (3) Keep leads short to eliminate stray impedance effects.

Figure 4 shows an optimum wiring diagram of the AD505.

Figure 4. Wiring Diagram of the AD505.

GENERAL PURPOSE WIDEBAND COMPENSATION An approximate high frequency equivalent circuit of the AD505 is shown in Figure 5. The unity gain open loop gain bandwidth product can be adjusted over the range of 4MHz to 10MHz by selecting resistor (RBW) which is connected between pin 4 and pin 3. The lowest gain bandwidth product is a result of an open circuit (RBW = ∞) between pins 3 and 4, while the maximum is achieved by a short circuit (RBW = 0). Figure 6 displays the open loop frequency and phase response of the AD505. Note that as RBW decreases the open loop gain increases, and that the amplifier is stable as long as the loop unity gain crossover is below 10MHz. In the R<sub>BW</sub> = ∞ condition, the leading phase shift above 200 kHz is a result of stray capacitance across the  $20 k\Omega$ input resistor, and can be used by the designer to increase network stability.

R<sub>BW</sub> ≤180°Ω Approximate High Frequen alent C 90 70 GAIN 60 VOLTAGE 50 40 30 20 FREQUENCY - Hz (a) -80 -90 -90 0 -100 -110 -120 -110 -130 -140 -150

Figure 6. Open Loop Frequency and Phase Response.

FREQUENCY-Hz

(b)

The input impedance at high frequencies can be represented by, in effect, a  $350\Omega$  resistor to common (the "Miller" impedance of a 1.5pF capacitor\*). This low impedance effectively permits the amplifier to be stable (for large enough values of  $R_f$ ) even at low values of signal gain. For example, with  $R_{BW}=0$ , a stable gain of 10 (20dB) can be obtained using  $R_S=5k\Omega$  and  $R_f=50k\Omega$ , since the input impedance of  $500\Omega$  dominates the  $5k\Omega$  source resistor. Similarly, a gain of 50.... without any reduction in bandwidth.....can be obtained using a  $1k\Omega{:}50k\Omega$  ratio.

$$*z_{in} \approx \frac{X_c(\omega)}{G(\omega)} = \frac{1}{2\pi \cdot f \cdot C \cdot G(\omega)} = 350\Omega \text{ at } f = 1 \text{MHz},$$

where  $G(\omega)$  = open loop gain as a function of frequency and  $X_c(\omega)$  = reactive capacitance of capacitor.

Note: At high frequencies,  $Z_{in}$  is approximately constant since f and  $G(\omega)$  are inverse functions of frequency.

In order to provide application flexibility and low cost, the AD505 is externally compensated with several capacitors. Several compensation circuits for differing conditions are shown in Figure 7.

(b) Connection as unity gain inverter (capacitive load)

(c) Connection for 100% feedback (e.g., as low-frequency integrator)

(d) Connection as unity gain inverter

Figure 7. Compensation Connections of AD505 for Various Conditions of Feedback.

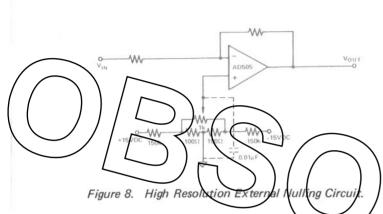

#### **NULLING THE AD505**

The offset voltage of the AD505 is extremely small and, therefore, nulling is generally not required. However, should offset nulling be desirable, Figure 8 shows a very effective, high resolution nulling circuit that may be used without degrading other performance parameters. This offset arrangement can also be used to correct for any system error that may be present, without affecting the performance of the amplifier.

The indicated values in Figure 8 represent one specific case and can be easily adjusted to any particular application. If the impedance of this network as seen from the positive terminal of the AD505 is higher than  $10k\Omega$ , it is suggested that a  $0.01\mu\text{F}$  capacitor to ground be used to bypass the network.

#### INPUT CHARACTERISTICS

In addition to its superior dynamic characteristics, the AD505 maintains low bias currents of 25nA max and a low  $V_{OS}$  drift of  $15\mu V/^{\circ}C$  max.

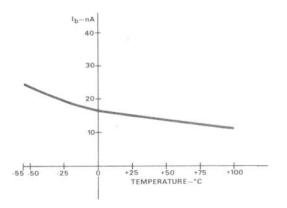

Figure 9 displays the input bias current vs. temperature characteristic of the AD505. Note that the bias current at room temperature is 15nA and increases to less than 25nA at  $-55^{\circ}$ C.

Figure 9. Input Bias Current vs. Temperature.

Figure 10 displays the offset voltage drift characteristic of the AD505. Note that average temperature coefficient of the offset voltage is approximately  $2.5\mu V/^{\circ}C$  for higher temperatures and  $5.0\mu V/^{\circ}C$  for low temperatures.

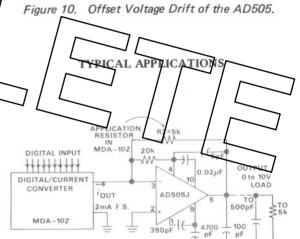

AD505J as Fast Current-to-Voltage Converter.

#### Fast Output Buffer for Digital/Current Converter

In this configuration, the converter and amplifier settle to within 0.1% (1 LSB) in 3 $\mu$ s, and to within ½ LSB in 5 $\mu$ s, typically. With the component values indicated, the AD505 can feed load impedance of 5k $\Omega$  in parallel with 500pF. Interwiring capacitance between the converter output and the amplifier input, plus the converter's output capacitance, should be held to within 10pF if possible. When applied with the *bipolar* version of MDA-10Z, the built-in feedback resistor for ±10V output is 10k $\Omega$ . The 20k $\Omega$  RBW shunt should be replaced by about 5k $\Omega$ .

Although the MDA-10Z is indicated in this example, the AD505 may be used to unload converters having output impedance values other than the MDA-10Z's  $1.5 \mathrm{k}\Omega$ . For example, when used with a 10-bit converter assembled from  $\mu\mathrm{DAC}$  switches and resistor networks, the external  $R_{BW}$  shunt may be omitted and a  $7.5 \mathrm{k}\Omega$  load connected from the summing point to ground.

### **OUTLINE DIMENSIONS**

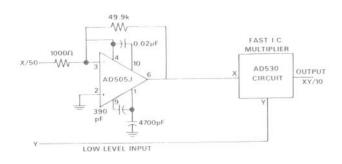

Preamplifier for Fast IC Multiplier

Preamplifier for Fast IC Multiplier

Multipliers often provide their best accuracy when both inputs and output can swing through the full-scale range. One of the problems in taking advantage of the excellent high frequency capabilities of the AD530 Multiplier-Divider is simply finding a low-cost integrated-circuit amplifier capable of driving it with ±10% at requencies up to 1MHz. The AD505 J makes an excellent preamplifier for this purpose it is shown above connected for gdin of 50, and applied to one of the AD530 inputs. Either or both input signals can be preamplified in this manner.

In this circuit, the internal  $20k\Omega$  resistor has been shorted out for maximum bandwidth. The frequency for -3dB response in this configuration is typically 1.6MHz, with full output capability.

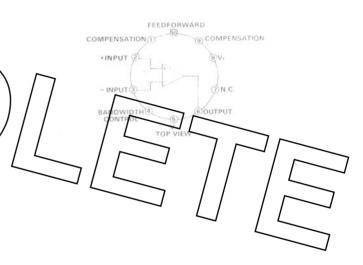

#### **TO-100 PIN CONFIGURATION**

#### **BONDING DIAGRAM**

The AD505 is available in chip or wafer form. Because of the critical nature of using unpackaged devices, it is suggested that the factory be contacted for specific information regarding price, delivery and testing.